В начале октября компания Xilinx представила новый чип Versal, построенный на программируемых вентильных матрицах (FPGA). Логику работы такого устройства можно модифицировать в любой момент в процессе использования. Ожидается, что чип ускорит работу систем ИИ и найдет применение в сетях 5G. Релиз процессора намечен на конец 2019.

Далее рассказываем об устройстве и чем оно поможет сетям нового поколения.

/ Flickr / Mike Mozart / CC

Технология 5G использует высокие частоты — 28 ГГц и выше — поэтому сигнал плохо транслируется на большие расстояния. Плюсом его распространению сильно мешают стены домов. В условиях города это может приводить к снижению качества соединения.

Эксперты говорят, что это станет препятствием для работы большого количества IoT-устройств, активный рост числа которых прогнозируют с 2020 года (как раз тогда, когда будут развернуты полноценные 5G-сети).

Подключенные устройства, например, автомобили или носимые медицинские гаджеты, должны обмениваться данными в реальном времени. Нестабильность подключения может помешать им адекватно оценить обстановку вокруг или передать жизненно важные данные (например, о состоянии здоровья человека) на серверы обслуживающей организации. Компании планируют решать эту проблему расстановкой специальных распределенных антенных систем, однако и с этим возникают трудности.

К примеру, сейчас в Нью-Йорке установлено более тысячи базовых станций. Чтобы покрыть сетью 5G весь город, нужно будет установить еще полмиллиона. Стоимость реализации проекта получится намного выше, чем в случае с предыдущими «G-стандартами».

Устройство Xilinx поможет решить проблемы со стабильностью интернет-соединения с помощью систем ИИ, на работу с которыми оно «заточено». Чип Versal будет заниматься обработкой алгоритмов машинного обучения в сетях 5G, оптимизирующих диаграммы направленности антенн мобильной связи. Это позволит избегать слепых секторов и выбирать подходящий режим трансляции данных.

Еще системы ИИ усовершенствуют хендовер-алгоритмы, которые отвечают за передачу сессий от одной станции к другой. Также сети будут самовосстанавливаться и адаптироваться, автоматически перенаправляя данные, если какой-либо узел выходит из строя. Так, пользователи 5G смогут свободно перемещаться по зданию или городу без сбоев в подключении.

У Xilinx уже появились заказчики на AI-чипы для 5G. Процессоры Versal будут использовать для организации сети на Олимпийских играх 2020.

Концепцию Versal компания Xilinx представила в октябре. Новая микросхема является гетерогенной, то есть использует сразу несколько вычислительных блоков. Этими блоками могут быть процессоры, сопроцессоры, интегральные схем ASIC и FPGA.

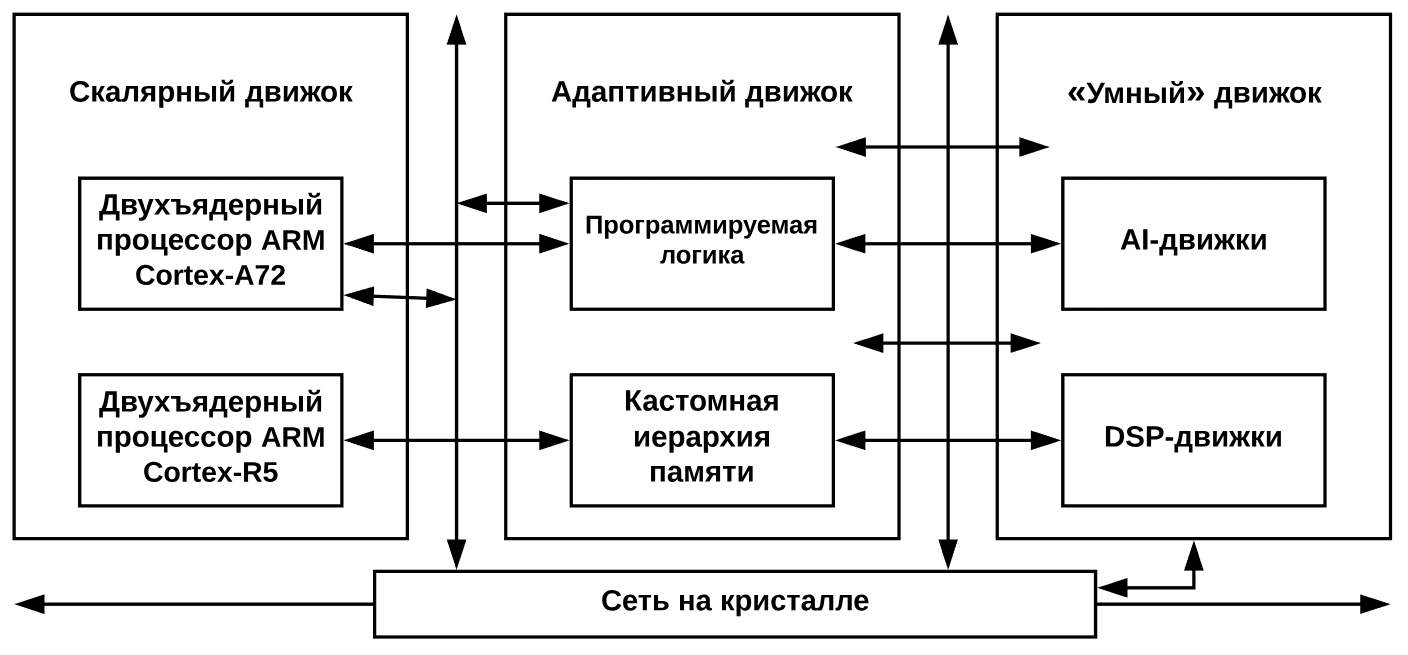

Новый чип Xilinx основан на улучшенной версии FPGA — архитектуре Adaptive Computer Accelerator Platform (ACAP). В её состав входят четыре базовых компонента: скалярный движок, адаптивный движок, векторные ускорители («умный» движок), а также сеть на кристалле (NoC — Network-on-Chip) для связи элементов системы.

Скалярный движок представлен двухъядерными процессорами ARM Cortex-A72 и Cortex-R5. Программируемая логика построена на конфигурируемых логических элементах с таблицами поиска, триггерами, памятью и специальными блоками для связи компонентов. Все это позволяет выстраивать иерархию памяти, заточенную под конкретную вычислительную задачу.

«Умный» движок базируется на VLIW-архитектуре, которая нужна для параллельного выполнения нескольких операций в одной инструкции. Еще применяется принцип вычислений SIMD. Такая структура помогает решать задачи МО и обрабатывать сигналы в 5–10 раз быстрее классических систем. Что касается NoC, то её заявленная пропускная способность составляет 1 Тбит/с.

Схема ACAP-архитектуры выглядит вот так.

Чипы семейства Versal будут производить в TSMC по 7-нм техпроцессу. Другие особенности архитектуры можно найти в официальных PDF-документах — обзоре ASAP-архитектуры и обзоре чипа Versal.

Программируется система на C, C++ и Python. По словам разработчиков, они остановили свой выбор на этих ЯП, так как по данным TIOBE, C, C++ и Python — самые популярные после Java.

Кроме того, эти языки дополняют друг друга. C и C++ — компилируемые, значит, код можно запускать на bare metal (в частности, на FPGA). Python же лучше других подходит для анализа данных и работы с системами ИИ. Другие доводы в пользу своего выбора Xilinx приводят в отдельном исследовании по теме (PDF).

Чипы на базе FPGA разрабатывают и другие компании, например Intel. Из последних продуктов компании можно выделить гибридное устройство Arria. Разработка представляет собой платформу из двух чипов: Xeon E5-2600 v4 и Altera Arria 10.

По словам представителей Intel, устройство подходит для серверов, ЦОД и облачных сервисов, где нагрузка часто увеличивается скачкообразно. Процессор на FPGA поможет обрабатывать данные параллельно, что повысит общую производительность системы. В Fujitsu, например, планируют снабдить этим чипом свою линейку серверов Primergy к концу года.

Другие игроки рынка — AMD, ARM, Qualcomm, Samsung и прочие — в 2012 году создали некоммерческую организацию HSA Foundation. Там популяризируют гетерогенные вычисления: разрабатывают отраслевые стандарты, помогают разработчикам выйти на рынок и спонсируют образовательные программы.

В Xilinx считают, что с развитием систем ИИ и распространением 5G-сетей спрос на FPGA-платформы увеличится. CEO компании Xilinx Виктор Пенг (Victor Peng) отмечает, что единственное препятствие на пути к массовому производству чипов — конкуренция со стороны CPU и GPU, которая не дает FPGA-решениям «захватить» рынок. Но, вероятно, скачка спроса (если он все же произойдет) не стоит ждать раньше 2020 года.

P.S. Дополнительные материалы из корпоративного блога VAS Experts:

P.P.S. Пара свежих статей из нашего блога на Хабре:

Далее рассказываем об устройстве и чем оно поможет сетям нового поколения.

/ Flickr / Mike Mozart / CC

Проблема 5G-сетей

Технология 5G использует высокие частоты — 28 ГГц и выше — поэтому сигнал плохо транслируется на большие расстояния. Плюсом его распространению сильно мешают стены домов. В условиях города это может приводить к снижению качества соединения.

Эксперты говорят, что это станет препятствием для работы большого количества IoT-устройств, активный рост числа которых прогнозируют с 2020 года (как раз тогда, когда будут развернуты полноценные 5G-сети).

Подключенные устройства, например, автомобили или носимые медицинские гаджеты, должны обмениваться данными в реальном времени. Нестабильность подключения может помешать им адекватно оценить обстановку вокруг или передать жизненно важные данные (например, о состоянии здоровья человека) на серверы обслуживающей организации. Компании планируют решать эту проблему расстановкой специальных распределенных антенных систем, однако и с этим возникают трудности.

К примеру, сейчас в Нью-Йорке установлено более тысячи базовых станций. Чтобы покрыть сетью 5G весь город, нужно будет установить еще полмиллиона. Стоимость реализации проекта получится намного выше, чем в случае с предыдущими «G-стандартами».

Как эти проблемы поможет решить Versal

Устройство Xilinx поможет решить проблемы со стабильностью интернет-соединения с помощью систем ИИ, на работу с которыми оно «заточено». Чип Versal будет заниматься обработкой алгоритмов машинного обучения в сетях 5G, оптимизирующих диаграммы направленности антенн мобильной связи. Это позволит избегать слепых секторов и выбирать подходящий режим трансляции данных.

Еще системы ИИ усовершенствуют хендовер-алгоритмы, которые отвечают за передачу сессий от одной станции к другой. Также сети будут самовосстанавливаться и адаптироваться, автоматически перенаправляя данные, если какой-либо узел выходит из строя. Так, пользователи 5G смогут свободно перемещаться по зданию или городу без сбоев в подключении.

У Xilinx уже появились заказчики на AI-чипы для 5G. Процессоры Versal будут использовать для организации сети на Олимпийских играх 2020.

Особенности архитектуры чипа

Концепцию Versal компания Xilinx представила в октябре. Новая микросхема является гетерогенной, то есть использует сразу несколько вычислительных блоков. Этими блоками могут быть процессоры, сопроцессоры, интегральные схем ASIC и FPGA.

Новый чип Xilinx основан на улучшенной версии FPGA — архитектуре Adaptive Computer Accelerator Platform (ACAP). В её состав входят четыре базовых компонента: скалярный движок, адаптивный движок, векторные ускорители («умный» движок), а также сеть на кристалле (NoC — Network-on-Chip) для связи элементов системы.

Скалярный движок представлен двухъядерными процессорами ARM Cortex-A72 и Cortex-R5. Программируемая логика построена на конфигурируемых логических элементах с таблицами поиска, триггерами, памятью и специальными блоками для связи компонентов. Все это позволяет выстраивать иерархию памяти, заточенную под конкретную вычислительную задачу.

«Умный» движок базируется на VLIW-архитектуре, которая нужна для параллельного выполнения нескольких операций в одной инструкции. Еще применяется принцип вычислений SIMD. Такая структура помогает решать задачи МО и обрабатывать сигналы в 5–10 раз быстрее классических систем. Что касается NoC, то её заявленная пропускная способность составляет 1 Тбит/с.

Схема ACAP-архитектуры выглядит вот так.

Чипы семейства Versal будут производить в TSMC по 7-нм техпроцессу. Другие особенности архитектуры можно найти в официальных PDF-документах — обзоре ASAP-архитектуры и обзоре чипа Versal.

Программируется система на C, C++ и Python. По словам разработчиков, они остановили свой выбор на этих ЯП, так как по данным TIOBE, C, C++ и Python — самые популярные после Java.

Кроме того, эти языки дополняют друг друга. C и C++ — компилируемые, значит, код можно запускать на bare metal (в частности, на FPGA). Python же лучше других подходит для анализа данных и работы с системами ИИ. Другие доводы в пользу своего выбора Xilinx приводят в отдельном исследовании по теме (PDF).

Похожие решения

Чипы на базе FPGA разрабатывают и другие компании, например Intel. Из последних продуктов компании можно выделить гибридное устройство Arria. Разработка представляет собой платформу из двух чипов: Xeon E5-2600 v4 и Altera Arria 10.

По словам представителей Intel, устройство подходит для серверов, ЦОД и облачных сервисов, где нагрузка часто увеличивается скачкообразно. Процессор на FPGA поможет обрабатывать данные параллельно, что повысит общую производительность системы. В Fujitsu, например, планируют снабдить этим чипом свою линейку серверов Primergy к концу года.

Другие игроки рынка — AMD, ARM, Qualcomm, Samsung и прочие — в 2012 году создали некоммерческую организацию HSA Foundation. Там популяризируют гетерогенные вычисления: разрабатывают отраслевые стандарты, помогают разработчикам выйти на рынок и спонсируют образовательные программы.

В Xilinx считают, что с развитием систем ИИ и распространением 5G-сетей спрос на FPGA-платформы увеличится. CEO компании Xilinx Виктор Пенг (Victor Peng) отмечает, что единственное препятствие на пути к массовому производству чипов — конкуренция со стороны CPU и GPU, которая не дает FPGA-решениям «захватить» рынок. Но, вероятно, скачка спроса (если он все же произойдет) не стоит ждать раньше 2020 года.

P.S. Дополнительные материалы из корпоративного блога VAS Experts:

P.P.S. Пара свежих статей из нашего блога на Хабре: