Comments 50

Отличная статья с хорошим юмором! У вас тестовые точки используются только для припайки проводов и для щупов осциллографов или вы используете игольчатые поля?

+3

Спасибо, мы старались чтоб было не скучно.

Это контрольные точки для разработчиков, а не для игольчатых полей. В основном мы их ставим на все цепи Power Sequence, на все напряжения питания, на сбросы и на клоки.

Это контрольные точки для разработчиков, а не для игольчатых полей. В основном мы их ставим на все цепи Power Sequence, на все напряжения питания, на сбросы и на клоки.

+4

В Вашем блоге бесподобные статьи.

Можете посоветовать книги/статьи про разработку и архитектуру PCIe устройств, а также best practices, язык не важен, хоть китайский. На русском информации ужасающе мало, а на английском.

Можно ли где-нибудь посмотреть примеры дизайнов устройств?

Можете посоветовать книги/статьи про разработку и архитектуру PCIe устройств, а также best practices, язык не важен, хоть китайский. На русском информации ужасающе мало, а на английском.

Можно ли где-нибудь посмотреть примеры дизайнов устройств?

0

Спасибо.

С точки зрения общего развития — у IDT достаточно много Application Notes посвященных разным вопросам, связанным с PCI Express.

Если говорить именно о топологии — то Intel очень хорошо все описывает в своих Platform Design Guide — но к сожалению данный документ просто так не достать. Надо либо NDA с Intel, либо искать на китайских торрентах всяких.

С точки зрения общего развития — у IDT достаточно много Application Notes посвященных разным вопросам, связанным с PCI Express.

Если говорить именно о топологии — то Intel очень хорошо все описывает в своих Platform Design Guide — но к сожалению данный документ просто так не достать. Надо либо NDA с Intel, либо искать на китайских торрентах всяких.

0

Совершенно восхитительная статья, а конкретно вот этот текст:

нужно сразу в золотую рамку. Вообще, вызывает неподдельное уважение тот факт что у Вас происходит именно серьезный технический анализ проблемы, а не бессмысленные и беспощадные гадания(с периодическим заходом в антинаучные гипотезы)- как это часто происходит в хардварных командах.

По Dfx позвольте спросить:

— часто вообще сталкиваетесь с неправильной ориентацией компонента и отчего идет ошибка(схема или завод)?

— часто сталкиваетесь с проблемами на уровне футпринта?

Ну и вопрос из области чистого любопытства- много смотрел серверных дизайнов на OCP, очень интересно было сравнить разводку памяти между Xeon и POWER, в том смысле что у последнего все выведено на отдельный контроллер Centaur: правильно ли я понимаю, что в случае POWER разводка более трудоемкая как из-за организации включения так и пинаута камня? У тех же Xeon очень оптимизированный пинаут, и чтобы развести много планок не требуется запредельного числа слоев- так ли это?

Самый большой кошмар разработчика — когда все работает сразу. Это значит только одно — где-то закопана мина, которая сработает после отгрузки 100500 единиц оборудования заказчику. Дело в том, что в процессе поиска причины какой-то глобальной проблемы осуществляется проверка нескольких гипотез и как правило выявляется множество мелких неисправностей, никак с возникшей проблемой не связанных. Нет большой проблемы — не найдёте маленьких. Их за вас найдут ваши заказчики.

нужно сразу в золотую рамку. Вообще, вызывает неподдельное уважение тот факт что у Вас происходит именно серьезный технический анализ проблемы, а не бессмысленные и беспощадные гадания(с периодическим заходом в антинаучные гипотезы)- как это часто происходит в хардварных командах.

По Dfx позвольте спросить:

— часто вообще сталкиваетесь с неправильной ориентацией компонента и отчего идет ошибка(схема или завод)?

— часто сталкиваетесь с проблемами на уровне футпринта?

Ну и вопрос из области чистого любопытства- много смотрел серверных дизайнов на OCP, очень интересно было сравнить разводку памяти между Xeon и POWER, в том смысле что у последнего все выведено на отдельный контроллер Centaur: правильно ли я понимаю, что в случае POWER разводка более трудоемкая как из-за организации включения так и пинаута камня? У тех же Xeon очень оптимизированный пинаут, и чтобы развести много планок не требуется запредельного числа слоев- так ли это?

+3

Привет, Максим.

По DFX:

— Ну как часто… бывает. Я не скажу что прям всегда — но первое что мы проверяем когда что-то не запустилось — это первые пины. Вот не далее как месяц назад пришла партия плат на одной из которых квадратный микроконтроллер был повернут на 90 градусов. В чистом виде ошибка фаба.

— Касательно ошибок в схеме и футпринтов — у нас максимальный re-use. Мы стараемся брать не то что компоненты, которые уже применены нами — а целые куски схем из девайса в девайс таскаем. Иногда даже в ущерб оптимизации. У нас пожалуй разнообразия в платах больше, чем в схемах которые на них реализованы. Так что со временем количество таких ошибок минимизируется. Косячки в футпринтах бывают часто — но благо наши PCBA партнеры очень глазастые и внимательно отсматривают наши гербер и ассембли файлы.

Касательно твоего второго вопроса.

Сказать что при проектировании Кентавра IBM вообще не думал о разводке его на плате — это вообще ничего не сказать. У Intel с этим делом все гораздо лучше. Это правда.

По DFX:

— Ну как часто… бывает. Я не скажу что прям всегда — но первое что мы проверяем когда что-то не запустилось — это первые пины. Вот не далее как месяц назад пришла партия плат на одной из которых квадратный микроконтроллер был повернут на 90 градусов. В чистом виде ошибка фаба.

— Касательно ошибок в схеме и футпринтов — у нас максимальный re-use. Мы стараемся брать не то что компоненты, которые уже применены нами — а целые куски схем из девайса в девайс таскаем. Иногда даже в ущерб оптимизации. У нас пожалуй разнообразия в платах больше, чем в схемах которые на них реализованы. Так что со временем количество таких ошибок минимизируется. Косячки в футпринтах бывают часто — но благо наши PCBA партнеры очень глазастые и внимательно отсматривают наши гербер и ассембли файлы.

Касательно твоего второго вопроса.

Сказать что при проектировании Кентавра IBM вообще не думал о разводке его на плате — это вообще ничего не сказать. У Intel с этим делом все гораздо лучше. Это правда.

+3

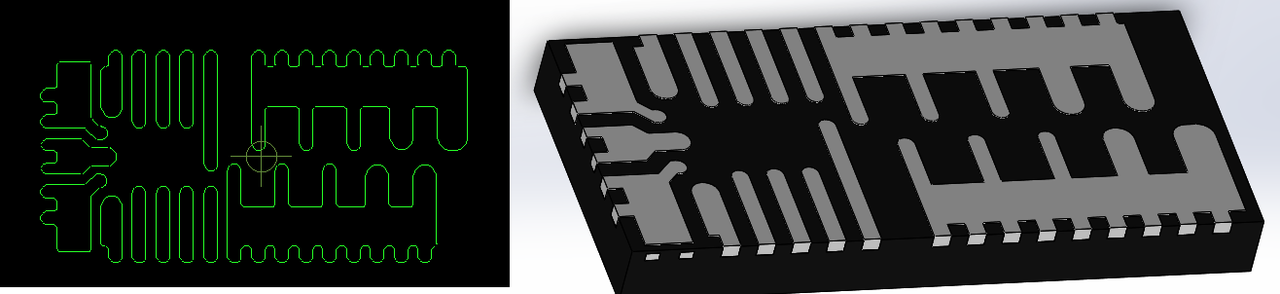

Привет, Антон- и большое спасибо за развернутый ответ. Ну, в случае серверных борд re-use наверное более чем оправдан: даже чисто по-человечески страшновато каждый раз делать все from-sсratch, тем более для дизайнов такого уровня, к тому же жалко не использовать хорошие куски. С футпринтами интересно весьма- я в своих задачах получал в основном негативные фидбеки при использовании manufacturer recommended footprint для нестандартных корпусов как на картинке, пока не начал делать все с нуля включая 3д модели:

В серверах много используются всякие powerstage, drmos и т.п. для организации многофазных POL DC/DC, типа SiC645- у вас бывали проблемы с такими корпусами?

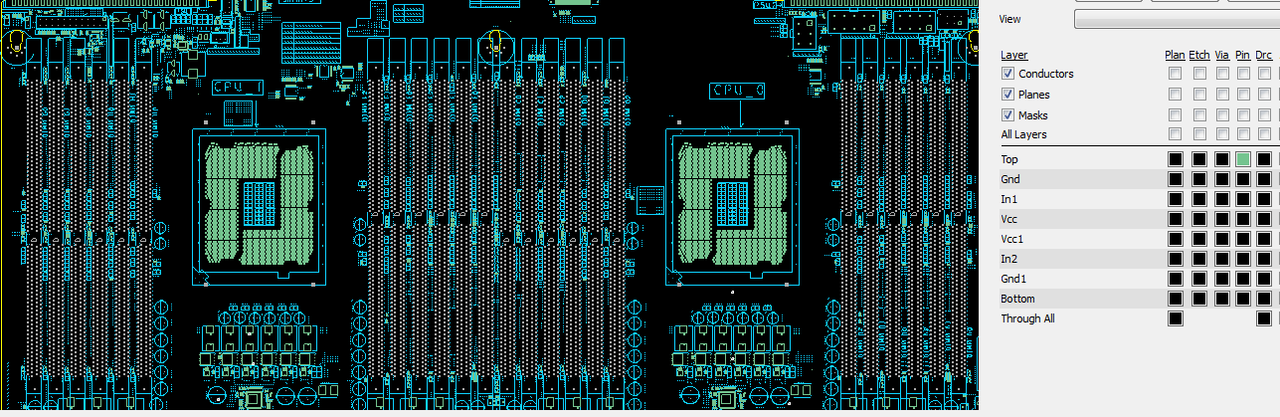

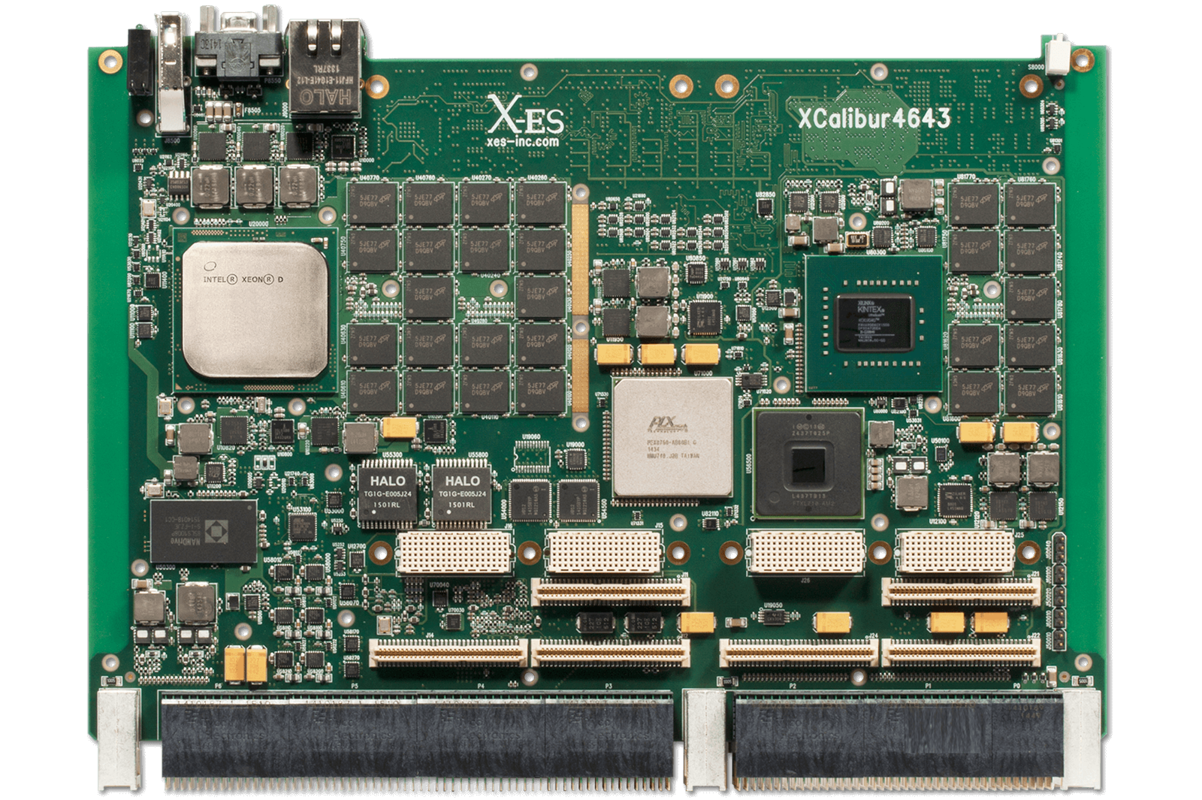

С кентавром стало яснее, пинаут у него конечно страшный но мне кажется, что по-настоящему этот момент заиграл бы если сразу распаивались микросхемы на плату, а не сокеты под модули: с зионом(и заодно 10 стратиксами) судя по всему особых проблем быть не должно- смотрю на примерно такие платы

А с кентавром наверное будет пот, даже не могу представить разводку. С ним вообще бывают memory-down дизайны? Почему привел эти картинки: интересно узнать субъективное мнение- в своих платах я воюю за каждый мм, кладу меандры и проводники без «пустых островов»(~99% использование пространства) и когда вижу разводку зиона, и тем более с модулями памяти, то сразу заведую белой завистью. Сложилось впечатление что в случае кентавра, особенно когда он не один на плате, разводка может и не супер сложная, но очень и очень трудоемкая из-за неудачного пинаута- это так?

В серверах много используются всякие powerstage, drmos и т.п. для организации многофазных POL DC/DC, типа SiC645- у вас бывали проблемы с такими корпусами?

С кентавром стало яснее, пинаут у него конечно страшный но мне кажется, что по-настоящему этот момент заиграл бы если сразу распаивались микросхемы на плату, а не сокеты под модули: с зионом(и заодно 10 стратиксами) судя по всему особых проблем быть не должно- смотрю на примерно такие платы

А с кентавром наверное будет пот, даже не могу представить разводку. С ним вообще бывают memory-down дизайны? Почему привел эти картинки: интересно узнать субъективное мнение- в своих платах я воюю за каждый мм, кладу меандры и проводники без «пустых островов»(~99% использование пространства) и когда вижу разводку зиона, и тем более с модулями памяти, то сразу заведую белой завистью. Сложилось впечатление что в случае кентавра, особенно когда он не один на плате, разводка может и не супер сложная, но очень и очень трудоемкая из-за неудачного пинаута- это так?

0

И вдогонку вопрос- в твоем посте посте упомянуто что:

Неужели такие платы в герберах отправляете? В смысле, почему не ODB++ и/или другие(новые) форматы?

наши PCBA партнеры очень глазастые и внимательно отсматривают наши гербер и ассембли файлы.

Неужели такие платы в герберах отправляете? В смысле, почему не ODB++ и/или другие(новые) форматы?

0

Ну я не знаю как твои китайцы, а наши китайцы всякие такие новомодные штуки — не понимают =)

+1

:) Наверное какие-то привередливые китайцы- в Азии часто встречал проблемы с принятием тех же Gerber X2(которые крайне удобны для HDI плат в сравнении с обычными герберами), а ODB++ никогда не вызывал вопросов, формат весьма зрелый же. Но вполне допускаю что скорее всего здесь многого не знаю, т.к. по больше части дизайню под EU/US заводы- полагаю в то же самое время, борды как у вас наверное делает кто-то уровня фокскона с пегатроном со своими правилами и хотелками.

0

Да нет. С точки зрения технологичности у нас достаточно обыденные борды.

Мы ж не айфоны делаем.

Я думаю их почти все можно в России сделать с технической точки зрения.

У нас есть одна мрачная, но ее мрачность заключается исключительно и только в длине 700мм — мало у кого помещается такая заготовка и проблемы с пайкой (ее коробит) и со сверлением — на длине точность уезжает.

Мы ж не айфоны делаем.

Я думаю их почти все можно в России сделать с технической точки зрения.

У нас есть одна мрачная, но ее мрачность заключается исключительно и только в длине 700мм — мало у кого помещается такая заготовка и проблемы с пайкой (ее коробит) и со сверлением — на длине точность уезжает.

0

Понятно- ну с длинными бордами ситуация ожидаема вполне, да и наверное логично при таких вводных предполагать проблемы также с backdrill на слабых фабах. По поводу пайки, вы когда-нибудь делали LGA(сокетные) to BGA conversion? Понятно что на особо теплых компонентах в этом, пожалуй, смысла нет, но просто интересно: видел как зионы те же так переделывают под rugged серверы.

0

Насчет memory-down.

Без поддержки IBM — memory-down тебе гарантирован.

А если с точки зрения работоспособности в целом — Кентавр не умеет делать Degrade скорости ни по своей последовательной шине 9.6 GT, ни по собственно DDR4 1600. То есть если на данных скоростях оно не поднимется — то опустить частоту чтобы хоть как-то что-то заработало — не получится. Пан или пропал.

Касательно сложности разводки при распаянных чипах — не могу сказать, мы ж его так не разводили.

Без поддержки IBM — memory-down тебе гарантирован.

А если с точки зрения работоспособности в целом — Кентавр не умеет делать Degrade скорости ни по своей последовательной шине 9.6 GT, ни по собственно DDR4 1600. То есть если на данных скоростях оно не поднимется — то опустить частоту чтобы хоть как-то что-то заработало — не получится. Пан или пропал.

Касательно сложности разводки при распаянных чипах — не могу сказать, мы ж его так не разводили.

0

Сложно представить POWER-based дизайн без поддержки IBM, разве что есть какое-то ограничение на «элитность» в духе разделение Tier 1/2/3, но в целом ситуация понятна- даже странно что у отдельного контроллера есть такие ограничения. Даташита на кентавр у меня разумеется нет, но предполагал что он невероятно интеллектуальный- м.б. может даже перекидывать адреса как удобно(в духе Nvidia Tegra K1 например или круче). Но наверное проще таки заручиться поддержкой чем потеть с memory-down в случае с кентавром.

0

В серверах много используются всякие powerstage, drmos и т.п. для организации многофазных POL DC/DC, типа SiC645- у вас бывали проблемы с такими корпусами?

Пока нет — но я боюсь их как огня если честно.

0

А почему если не секрет? Классные приборы вроде и удобно.

0

А ты пойди его реворкни, если ошибешься.

Или руками перепаяй.

Или руками перепаяй.

0

Насчет реворка 100% соглашусь- тут проводками не наиграешься особенно, но именно в части перепайки коллеги сообщали о проблемах только в случае конкретно больших и мощных SIP, вроде ISL8272 или EM2130L01QI

Вообще, как например в случае с RF фронтендами, часто делаю отдельную тестовую плату с целевой разводкой под POL DC/DC- ее прогоняли, а потом ставили в целевую борду: и то, по большей части чтобы проверить футпринт- производители довольно часто допускают ошибки в чертежах на корпус. Но разумеется и в плане чисто электрических тестов это очень сподручно.

Вообще, как например в случае с RF фронтендами, часто делаю отдельную тестовую плату с целевой разводкой под POL DC/DC- ее прогоняли, а потом ставили в целевую борду: и то, по большей части чтобы проверить футпринт- производители довольно часто допускают ошибки в чертежах на корпус. Но разумеется и в плане чисто электрических тестов это очень сподручно.

0

Подскажите, пжлст, в чём такая красота делается/трассируется?

0

Расскажите, пожалуйста, про глазковую диаграмму.

Как определить хорошую от плохой.

Я задним умом понимаю, что смотрятся передние и задние фронты, поэтому получается «глаз».

Но вдруг, есть что то новое.

Как определить хорошую от плохой.

Я задним умом понимаю, что смотрятся передние и задние фронты, поэтому получается «глаз».

Но вдруг, есть что то новое.

0

Ну если совсем на пальцах — то существует так называемая Compliance Mask. Это ромбик который врисосывается в центр глаза. Точнее даже не в центр глаза — а в точку захвата приемником. Если глаз наползает на ромб — fail, не наползает — pass.

А сам глаз получается посредством прогона в канале PRBS последовательности которая нарезается по три бита и все эти кучки по 3 бита друг на друга накладываются. PRBS формируется таким образом что в ней происходит перебор все-возможных переходов от 000 до 111 в разных комбинациях.

А сам глаз получается посредством прогона в канале PRBS последовательности которая нарезается по три бита и все эти кучки по 3 бита друг на друга накладываются. PRBS формируется таким образом что в ней происходит перебор все-возможных переходов от 000 до 111 в разных комбинациях.

+1

Кстати на иллюстрациях в статье это на самом деле не глазковая диаграмма в классическом понимании. Потому что внутри чипа конечно нет никакого осциллографа в традиционном понимании. Это графическое отображение интенсивности ошибок при сдвиге точки захвата приемника в системе координат напряжение/время. Фигурально выражаясь — он двигает прицелом и смотрит есть ошибки приема или нет. Темно синяя зона — это 0 ошибок. То есть это некий допуск приемника в пределах которого он может гулять.

Но по сути — та же глазковая диаграмма.

Но по сути — та же глазковая диаграмма.

+2

Я наверное уже основательно достал своими вопросами :), но осмелюсь спросить еще- как на таких платах дезигнаторы на шелкографии ставите? Руки, скрипты, CAM редактор, другое?

0

Спрашивай — не жалко.

Автосилк + руки.

Ну то есть это я так думаю что наши топологи в основном именно так и делают.

Но так как я сам в нашей компании платы не развожу и в процесс расстановки шелкографии особо не лезу — то вполне допускаю, что они делают не совсем так.

Автосилк + руки.

Ну то есть это я так думаю что наши топологи в основном именно так и делают.

Но так как я сам в нашей компании платы не развожу и в процесс расстановки шелкографии особо не лезу — то вполне допускаю, что они делают не совсем так.

0

Спрашивай — не жалко.

Спасибо=) Ну, раз добро получено, хочу поинтересоваться(именно с оглядкой на серверную тематику)- пользуетесь ли и как часто следующими вещами:

— выравнивание паттерном trombone и особенно его разновидностью под названием switchback

— разводка под произвольным углом(не зигзаги), в т.ч. с дугами

— snake routing для бга с выводами в шахматном порядке

— торцевая металлизация плат (особенно жирных, бэкплейны не в счет)

— broadside coupled пары

— differential coplanar пары(связь с окружающей землей на том же слое)

— active/passive line conditioner для отдельных хайспидов

— индуктивности с дополнительным экранированием в питании

— конденсаторы с реверсированным корпусом(электрод по длинной стороне) и 3х выводные

Заодно интересно, какие задачи решаете с помощью Tag-Connect- понятно что дебаг, но что именно отлаживается?

0

— тромбон/аккордион — используем конечно, про switchback впервые слышу

— 11 градусов — да, арки нет. В одном проекте только были, c 12.5 GHz сердесами. Арки слайдить муторно.

— snake routing — да

— торцевую металлизацию не делаем. Мы не отводим тепло в торцы платы. А про чудодейственное улучшение ЭМС металлизацией торцев — ИМХО миф.

Все остальное по списку — нет.

Tag-Connect мы цепляем к Aadvark. А с этим девайсом добрая половина I2C дебажного софта работает.

— 11 градусов — да, арки нет. В одном проекте только были, c 12.5 GHz сердесами. Арки слайдить муторно.

— snake routing — да

— торцевую металлизацию не делаем. Мы не отводим тепло в торцы платы. А про чудодейственное улучшение ЭМС металлизацией торцев — ИМХО миф.

Все остальное по списку — нет.

Tag-Connect мы цепляем к Aadvark. А с этим девайсом добрая половина I2C дебажного софта работает.

0

тромбон/аккордион — используем конечно, про switchback впервые слышу

С аккордеоном понятно- его все используют. Switchback, это как бы «однократный тромбон»- с ним очень легко накрутить много длины если большой разбег в матчгруппе, в то же время с ним проще всего облажаться при тюнинге в плотном дизайне.

11 градусов — да, арки нет. В одном проекте только были, c 12.5 GHz сердесами. Арки слайдить муторно.

Арки слайдить конечно сложнее чем прямые- я сам чаще обычно скругляю уже разведенное: это гораздо проще. Примечательно что почти все платы которые смотрел с ОСР были именно с разводкой под произвольным углом- поэтому стало любопытно.

торцевую металлизацию не делаем. Мы не отводим тепло в торцы платы. А про чудодейственное улучшение ЭМС металлизацией торцев — ИМХО миф.

Склоняюсь к мнению что эта технология несколько переоцененная в ряде случаев, но она точно небесполезна, в т.ч. с точки зрения того же ЭМС. Скорее ее «сила» не такая большая как некоторые ожидают(чудо-таблетка).

А используют ли в POWER-based серверах HMC?

0

Switchback, это как бы «однократный тромбон»- с ним очень легко накрутить много длины если большой разбег в матчгруппе, в то же время с ним проще всего облажаться при тюнинге в плотном дизайне.

Вот эту хрень, которая Switchback — мы используем постоянно. Но я не знал что она так называется.

Тромбон и тромбон…

Арки слайдить конечно сложнее чем прямые- я сам чаще обычно скругляю уже разведенное: это гораздо проще.

Скругление углов… — ну вообще сам же понимаешь что это марафет. В полосе до 10GHz — ничего не дает. Только лишнюю головную боль.

Про произвольный угол — ну вообще мы хотели просить PCB Shop просто поворачивать заготовку на 11 градусов. Но потом поняли что проконтролировать мы его не сможем. Он отрежет прямо, а денег возьмет как будто повернул и пол-заготовки выкинул. Поэтому — иногда да, упарываемся зигзагом под 11 градусов когда тянуть далеко надо. Там Fiberwave эффект уже по настоящему начинает влиять. Причем не только на Skew Match но и на Lane-Lane match.

Склоняюсь к мнение что эта технология несколько переоцененная в ряде случаев, но она точно небесполезна, в т.ч. с точки зрения того же ЭМС. Скорее ее «сила» не такая большая как некоторые ожидают(чудо-таблетка).

Хочешь тихие торцы — сделай питание уже опорной земли диэлектриков на 7-10. Этого достаточно.

А используют ли в POWER-based серверах HMC?

По перспективным технологиям у нас Алексей эксперт — может ответит позже.

+1

Вот эту хрень, которая Switchback — мы используем постоянно. Но я не знал что она так называется.

Тромбон и тромбон…

Тут видимо я ввел тебя в заблуждение формулировкой- просто привык что классический тромбон, это просто «перевернутый» аккордеон, а свичбэк всегда в 1 «виток» и может уже следовать по траектории проводника с изломами.

Скругление углов… — ну вообще сам же понимаешь что это марафет. В полосе до 10GHz — ничего не дает. Только лишнюю головную боль.

Да, разумеется- хотя часто использую там где не получается сохранить минимальную длину 45гр сегментов(т.е. где выходит сильно меньше скажем 1.5х ширины трассы).

Про произвольный угол — ну вообще мы хотели просить PCB Shop просто поворачивать заготовку на 11 градусов. Но потом поняли что проконтролировать мы его не сможем. Он отрежет прямо, а денег возьмет как будто повернул и пол-заготовки выкинул. Поэтому — иногда да, упарываемся зигзагом под 11 градусов когда тянуть далеко надо. Там Fiberwave эффект уже по настоящему начинает влиять. Причем не только на Skew Match но и на Lane-Lane match.

Ну тут я не понимаю немного- а откуда именно это значение, 11гр? Про борьбу с влиянием струтуры диэлектрика разумеется знаю из первых рук :), но история именно про полностью произвольные углы, например:

— Xeon to Xeon

— POWER to POWER

Хочешь тихие торцы — сделай питание уже опорной земли диэлектриков на 7-10. Этого достаточно.

Всегда бы места столько было:) Но тут больше интересно улучшение земли, особенно в RF бордах(почти всегда в них использовал), да и в HDI с BGA/WLCSP на краях тоже часто нет возможности убирать края плейнов питания внутрь.

По перспективным технологиям у нас Алексей эксперт — может ответит позже.

Весьма интересно было бы послушать.

0

HMC пока удел сильно специфического железа, то есть там, где реально это нужно — дорого же очень…

0

Спасибо за пояснение- а если не секрет, HMC подсоединяется напрямую или через какой-то контроллер, вроде того же кентавра? У HMC весьма удобный пинаут и вывод сигналов, но наверное это будет нивелироваться пинаутом POWER/контроллера?

0

У HMC же вообще свой интерфейс, ничего общего с DDR4 не имеющий, а значит требуется его поддержка со стороны хоста. Из популярных вычислительных платформ ее нет, насколько я знаю, ни у кого. Под FPGA — да, есть IP-ядра, но это логично. Вроде как она поддерживается еще в каких-то чипах быстрых сетевых свичей, но тут я точно не скажу — не занимался этим.

0

А можно для совсем непосвященных — кто является клиентами и откуда вообще берется все это железо?

0

Про клиентов я говорить не буду — у меня нет на это полномочий. Да я и не знаю особо, если честно.

А вопрос про происхождение железа — я не понял.

А вопрос про происхождение железа — я не понял.

+1

Ну в моем мирке все должно тестироваться производителем. Но судя по рассказу, вы не производите железо, вам его привозят (разное, от обычных материнских плат до каких-то кастомных железяк), причем какие-то опытные образцы… Вы в России? Кто-то производит материснские платы и собирает кастомные сервера? Расскажите об этом.

0

А, понятно.

Вам просто надо было прочитать все рассказы ))).

Железо мы разрабатываем по большей части — сами.

Я сначала хотел написать и расписать что мы делаем, но потом решил, что возможно завтра кто-нибудь из маркетинг-людей скажет это более правильными словами.

Сходите к нам на сайт www.yadro.com — там в принципе уже есть достаточно информации (его таки запустили).

Вам просто надо было прочитать все рассказы ))).

Железо мы разрабатываем по большей части — сами.

Я сначала хотел написать и расписать что мы делаем, но потом решил, что возможно завтра кто-нибудь из маркетинг-людей скажет это более правильными словами.

Сходите к нам на сайт www.yadro.com — там в принципе уже есть достаточно информации (его таки запустили).

+1

Мы в России. Разрабатываем сами архитектуру, печатные платы, корпуса, встроенное ПО для своих продуктов. Микросхемы и стандартные базовые компоненты (вентиляторы, блоки питания, диски, планки памяти) не делаем. По собственным изделиям, можно сказать, делаем всё, кроме непосредственно изготовления. Распространённая fabless-модель, по которой работает большинство производителей вычислительных систем.

Сборочное производство у нас тоже есть своё, в России. Кстати, одно из единичных в мире, сертифицированных по стандартам IBM — в новостях есть об этом упоминания.

Имена заказчиков я пока не могу называть — стандартной практикой раскрытия информации о поставках является публикация пресс-релиза совместно с заказчиком. В своё время сообщим.

Про некоторые разработки мы писали в этом блоге — можно почитать про архитектуру сервера в целом, технологию вывода PCIe наружу через кабели и отладку её технической реализации, плату управления сервером. Писали также про OpenBMC применительно к OpenPOWER, и вот совсем недавно — про первые тесты дисковой подсистемы сервера.

Что касается тестов железа, то часть проверок делается сразу на фабрике, детальное тестирование проходит у нас в лаборатории. Тут надо ещё на всякий случай сказать, если вдруг не вполне очевидно, что в этой статье Антон описал процесс тестирования изделий, ещё не вышедших в серийное производство. Опытных образцов, как правило первой ревизии, когда надо не только проверить соответствие произведённого изделия проекту, — но и выявить на практике, что в проекте надо улучшить или исправить до выпуска изделия в серию.

Контроль качества изготовления серийной продукции — отдельная большая тема.

Сборочное производство у нас тоже есть своё, в России. Кстати, одно из единичных в мире, сертифицированных по стандартам IBM — в новостях есть об этом упоминания.

Имена заказчиков я пока не могу называть — стандартной практикой раскрытия информации о поставках является публикация пресс-релиза совместно с заказчиком. В своё время сообщим.

Про некоторые разработки мы писали в этом блоге — можно почитать про архитектуру сервера в целом, технологию вывода PCIe наружу через кабели и отладку её технической реализации, плату управления сервером. Писали также про OpenBMC применительно к OpenPOWER, и вот совсем недавно — про первые тесты дисковой подсистемы сервера.

Что касается тестов железа, то часть проверок делается сразу на фабрике, детальное тестирование проходит у нас в лаборатории. Тут надо ещё на всякий случай сказать, если вдруг не вполне очевидно, что в этой статье Антон описал процесс тестирования изделий, ещё не вышедших в серийное производство. Опытных образцов, как правило первой ревизии, когда надо не только проверить соответствие произведённого изделия проекту, — но и выявить на практике, что в проекте надо улучшить или исправить до выпуска изделия в серию.

Контроль качества изготовления серийной продукции — отдельная большая тема.

+1

В том году разрабатывал одноплатник на IMX6DL. Видео на борту не требовалось, поэтому я не подключал модуль LVDS к питанию. Потом оказалось что от этой ноги питается контроллер DDR.

Вытянул проволоку с советского реле РЭС49 и припаял паяльником.

В итоге все заработало.

P.S. Паял в самопальной печи)

0

Это пример одной из двух крайностей.

Первая — это когда на каждый вывод питания вешают 100500 разномастных декапов и фильтров.

Второй — когда контроллер DDR запитывают проволокой.

Нормально =).

Мы сейчас пытаем борд (на рентгене который нарисован) — у него на Backplane коннекторе куда-то пропали контакты. Заводской брак. Причем на разных платах разные. Где-то клока нет, где-то неизвестно чего пока нет.

Так и живем.

Первая — это когда на каждый вывод питания вешают 100500 разномастных декапов и фильтров.

Второй — когда контроллер DDR запитывают проволокой.

Нормально =).

Мы сейчас пытаем борд (на рентгене который нарисован) — у него на Backplane коннекторе куда-то пропали контакты. Заводской брак. Причем на разных платах разные. Где-то клока нет, где-то неизвестно чего пока нет.

Так и живем.

+1

UFO just landed and posted this here

Вопрос не совсем в тему конкретно этой статьи, но тем не менее интересно используются ли глухие переходные отверстия на вашей материнской плате? Если можно поподробнее о глубине/диаметре, допустимых токах и других нюансах глухих отверстий.

0

Мы делали вариант дизайна с глухими отверстиями, но по-моему в производство мы его так и не отправили, потому что железка заработала и так. Там были проблемы с хвостами переходных отверстий, а бакдрилл не влезал из-за того, что к нему полагаются серьезные антипады.

Но в общем и целом — нет не используем, почему-то так получается, что там где у нас обычно проблемы с разводкой — они не спасают. Так что мне Вам особо и рассказать тут нечего.

Но в общем и целом — нет не используем, почему-то так получается, что там где у нас обычно проблемы с разводкой — они не спасают. Так что мне Вам особо и рассказать тут нечего.

+1

так как вы наверняка забыли перепаять компоненты, у которых в дизайне перепутаны ноги

Ха, а я думал это я один такой неудачник. У меня на каждой второй плате такая ерунда, хоть и проверяю по десять раз перед отправкой на производство… Думал они заколдованные какие-то.

0

Sign up to leave a comment.

Несколько слов о тестировании сложных аппаратных комплексов