Comments 80

Очень интересный опыт! А 5-10-50 пластин если заказывать, то они так и будут по 30к каждая или «оптом дешевле»?

0

Так и будут идти, потому что для завода это и так массовое серийное изделие.

0

Жаль… Плакала мечта нашего инженегра вместо микросборок свою микросхему толкать в оборудование :)

Ну глядишь, такими темпами через десяток-другой лет можно по почте будет получать готовые кристаллы по персональному проекту за стоимость пары бутербродов.

Надеюсь, доживу :)

Ну глядишь, такими темпами через десяток-другой лет можно по почте будет получать готовые кристаллы по персональному проекту за стоимость пары бутербродов.

Надеюсь, доживу :)

0

К сожалению, базовые расходы завода никуда не денутся. Но никто не отменял шаттлы, т.е. групповой заказ. Если у вас 4 инициативных разработчика, то на одного уже меньше 10к получается. Аналогично и для студентов это работает, т.е. есть дополнительные пути снижения стоимости для конечного заказчика.

+2

Вы количество чипов на пластине учитывайте еще. При тиражах в несколько тысяч штук в год собственный ASIC вполне может оказаться конкурентоспособным даже по 350-180 нм технологиям на зарубежных фабриках, не то что на БМК в России.

0

С разработкой под БМК в качестве студенческого проекта есть важная проблема: нужно много времени и сил, чтобы научить студента проектировать под БМК, и это будет время, которое студент не будет учить, например, САПР, на котором он потом реально будет работать.

Плюс это должен быть не дипломный проект, а курсовой — потому что диплом должен в идеале делаться в привязке к будущей работе. А курсовой проект — это как минимум на год раньше и как минимум на год знаний у студента меньше, то есть реалистичный проект — это будет сдвиговый регистр или мультиплексор на 16 каналов, но никак не огромный и сложный генератор синуса.

То есть, при всей большой привлекательности этой идеи (я был бы очень рад, если бы у нас такое было), у нее есть объективные недостатки, которые надо обойти при реализации.

Плюс это должен быть не дипломный проект, а курсовой — потому что диплом должен в идеале делаться в привязке к будущей работе. А курсовой проект — это как минимум на год раньше и как минимум на год знаний у студента меньше, то есть реалистичный проект — это будет сдвиговый регистр или мультиплексор на 16 каналов, но никак не огромный и сложный генератор синуса.

То есть, при всей большой привлекательности этой идеи (я был бы очень рад, если бы у нас такое было), у нее есть объективные недостатки, которые надо обойти при реализации.

+4

Если целью ставить именно работу с большими ASIC'ами в будущей проф. деятельности, то надо брать большие БМК, от Ангстрема, например. Цифровой маршрут от Cadence можно допилить для расстановки компонентов на кристалле типа «море транзисторов». Стоимость такого проекта, разумеется, вырастет.

Что касается именно маленьких БМК, то да, есть задача изучения специфических деталей маршрута, которые потом, может быть, не пригодятся. А может и обратно будет: научившись работать с БМК, люди перестанут от них шарахаться и начнут массово выпускать дешевые чипы… эхх, замечтался.

Но в целом идея была в том, чтобы показать о возможности дёшево выпустить микросхему по полноценному современному маршруту проектирования. На мой взгляд факт наличия возможности получить собственный кристалл должен очень сильно мотивировать студентов. При простом изучении САПРа «в ящик» такой мотивации нету и близко.

В целом, не каждый студент может осилить такой маршрут и работать надо много. Но это и касается работы в отрасли в целом.

Что касается именно маленьких БМК, то да, есть задача изучения специфических деталей маршрута, которые потом, может быть, не пригодятся. А может и обратно будет: научившись работать с БМК, люди перестанут от них шарахаться и начнут массово выпускать дешевые чипы… эхх, замечтался.

Но в целом идея была в том, чтобы показать о возможности дёшево выпустить микросхему по полноценному современному маршруту проектирования. На мой взгляд факт наличия возможности получить собственный кристалл должен очень сильно мотивировать студентов. При простом изучении САПРа «в ящик» такой мотивации нету и близко.

В целом, не каждый студент может осилить такой маршрут и работать надо много. Но это и касается работы в отрасли в целом.

+3

А кристаллы с завода приходят уже с разваренными выводами? Или варили выводы вручную, если да то как?

0

Конкретно я этот маршрут осваивал во время работы на предприятии, которое этим маршрутом пользуется в своих разработках. Поэтому нам кристаллы приходят в виде пластин. Пластины измеряются на зондовых автоматах, затем нарезаются и корпусируются. В случае заказа со стороны возможно попросить завод нарезать кристаллы, а корпусировать по системе Chip-on-board, разваривая кристалл прямо на печатную плату. Например, МЭЛТ этим(разваркой на плату) занимается для бытовых изделий.

+1

В статье идет речь про измерения прямо на пластине, зондовой станцией.

Но конкретно автор, думаю, после измерений на пластине варил выводы сам, а заводе, заводским оборудованием. Оно в принципе не смертельно дорогое и сложное, там больше проблем с легальным оборотом золота, чем с самим оборудованием.

UPD Ну да, я был прав

Но конкретно автор, думаю, после измерений на пластине варил выводы сам, а заводе, заводским оборудованием. Оно в принципе не смертельно дорогое и сложное, там больше проблем с легальным оборотом золота, чем с самим оборудованием.

UPD Ну да, я был прав

+1

UFO just landed and posted this here

Что продавать? Студенческий дипломный проект? Не думаю, что хотя бы один процент студентов способен сделать «продавабельный» диплом (а большинство тех, кто способен, делает составные части больших проектов). А вот собственноручно реализованое АЛУ или хотя бы сдвиговый регистр, в процессе разработки которых набиты типоые шишки — это то, что может быть нужно студенту для того, чтобы стать толковым спецом.

0

UFO just landed and posted this here

Так, стоп. Мы с вами, кажется, о разных вещах говорим. Я (и автор статьи) — о внедрении разработки под БМК в процесс обучения студентов и разработке в первую очередь для изучения процесса, в которой результат — только приятный бонус и дополнительная мотивация.

А вы, судя по всему, про любительские или DIY-проекты, где, несмотря на очевидную ценность разработки как процесса, результат все же первичен.

А вы, судя по всему, про любительские или DIY-проекты, где, несмотря на очевидную ценность разработки как процесса, результат все же первичен.

+2

Хабр торт!

+6

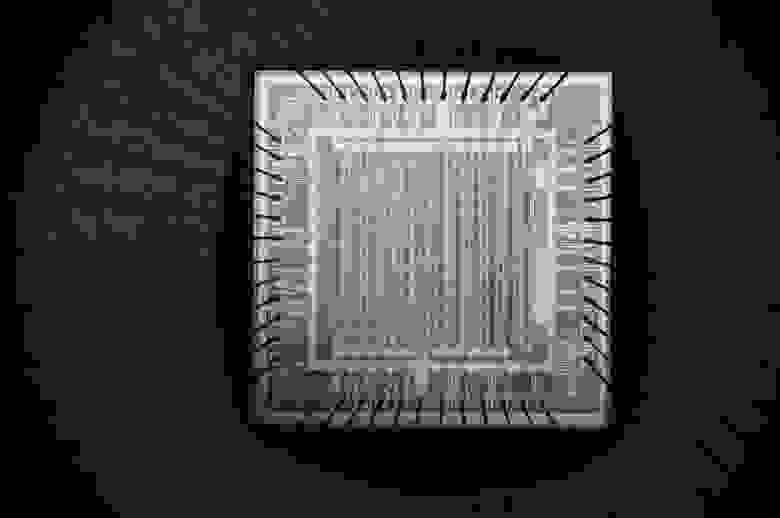

Хоть бы одну фотографию живого кристалла, так интересно поглядеть. А почему здесь был упомянут родной НИЦЭВТ?

+2

Потому что предприятие, на котором я работаю, когда то было микроэлектронным подразделением НИЦЭВТа.

Фотография БМК, правда не на 3к, а не 0.5к вентилей. Не лучшая фотка, но на скорую не нашел лучше.

Фотография БМК, правда не на 3к, а не 0.5к вентилей. Не лучшая фотка, но на скорую не нашел лучше.

Смотреть, весит 5МБ

+2

Справа вверху понятно реперные метки, а в левом верхнем углу — это трио тестовых транзисторов для контроля параметров?

П, З, И, С2-4 — это подложка, затвор, сток, исток? Куда делись С0 и С1?

П, З, И, С2-4 — это подложка, затвор, сток, исток? Куда делись С0 и С1?

0

Спасибо. Я просто много-много лет проработал в НИЦЭВТе. Это была самая моя лучшая работа.

+1

Зачем это всё? 30 000 рублей стоит выпуск одной пластины диаметром 100мм по технологии 2мкм. За эти деньги мы получаем ...

Любопытствую:

30 000 руб — а где это практически, какое предприятие?

Каков % выхода?

Выпустят ли всего одну пластину?

Сколько будет стоить еще и корпусировка, т.е. во сколько обходится конечный продукт (микросхемы)?

Это в статье всё теоретические соображения (включая 30 т.р.), или это практические выводы уже по свершившемуся факту?

0

Это и минский Интеграл, и наши Микрон с Ангстремом. Цены для этой технологии примерно одинаковы, рынок все же. Технологический выход годных выше 90%, что для такой старой технологии вполне неплохо. Ну и от завода к заводу выход годных разный. Одну пластину выпустят, но есть одно, которое напишу в конце.

30к рублей это моя личная оценка, основанная на большой практике. В последний раз ценами интересовался года два назад, поэтому сделал поправку «вверх». Корпусировка по chip-on-board стоит копейки.

К сожалению, не получится энтузиасту-частнику прийти с улицы на завод и начать с ним работать на таких же условиях, как и предприятию с большими объемами заказов. Спектр причин «а почему» на самом деле очень велик :) Но главной проблемой будет, я думаю, отсутствие налаженного маршрута работы с физ. лицами.

30к рублей это моя личная оценка, основанная на большой практике. В последний раз ценами интересовался года два назад, поэтому сделал поправку «вверх». Корпусировка по chip-on-board стоит копейки.

К сожалению, не получится энтузиасту-частнику прийти с улицы на завод и начать с ним работать на таких же условиях, как и предприятию с большими объемами заказов. Спектр причин «а почему» на самом деле очень велик :) Но главной проблемой будет, я думаю, отсутствие налаженного маршрута работы с физ. лицами.

+2

Про спектр «а почему» я примерно понимаю. Но всё же… Большие объемы, это интересно, сколько по деньгам. Как пример опять же, почему сразу энтузиаст-частник-физлицо. Кому надо можно и предприятие зарегистрировать, а может и уже есть.

То что вы написали в этом ответе все-таки противоречит и названию статьи, и некоторым её положениям.

Выше я забыл ещё спросить, а какая технология? PMOS? Depletion-mode NMOS (n-канальный МОП в режиме обеднения)? CMOS?

Но давайте я просто сразу спрошу то, что меня интересует. Есть старые оригинальные микросхемы, например Z80 (NMOS/CMOS), 6502 начинающие потихоньку становиться дефицитом. Или уже не выпускающийся и весьма дефицитный в мире MOS Technology SID (NMOS/HMOS-II). Возможно ли (в рамках предприятия, а не частного лица) организовать небольшую партию производства этих чипов, с условием того что маски, схемотехника, итд есть (грубо говоря — пересняты)? Каков минимальный уровень заказа (в тыс. рублей или млн.) реален? Положим что все маски есть. Насколько это возможно именно в практическом плане конкретных заводов итд?

То что вы написали в этом ответе все-таки противоречит и названию статьи, и некоторым её положениям.

Выше я забыл ещё спросить, а какая технология? PMOS? Depletion-mode NMOS (n-канальный МОП в режиме обеднения)? CMOS?

Но давайте я просто сразу спрошу то, что меня интересует. Есть старые оригинальные микросхемы, например Z80 (NMOS/CMOS), 6502 начинающие потихоньку становиться дефицитом. Или уже не выпускающийся и весьма дефицитный в мире MOS Technology SID (NMOS/HMOS-II). Возможно ли (в рамках предприятия, а не частного лица) организовать небольшую партию производства этих чипов, с условием того что маски, схемотехника, итд есть (грубо говоря — пересняты)? Каков минимальный уровень заказа (в тыс. рублей или млн.) реален? Положим что все маски есть. Насколько это возможно именно в практическом плане конкретных заводов итд?

0

Технология КМОП, HV КМОП.

В нашей практике были случаи, когда комплект фотошаблонов передавался с одного завода на другой вместе с информацией по тех. процессу, и новый завод начинал изготовление по новому тех. процессу. Если у вас есть только фотошаблоны, а данных по тех. процессу нету, или тех. процесс включает некие спеицифичные шаги, которые невозможно повторить на наличствующем оборудовании, то вероятность успешного выпуска сильно снижается. Но опять же, я не представляю ни один из заводов, это только мое мнение и моя практика. Лучше поискать на том же линкдине работников заводов и попытаться «изнутри» узнать о такой возможности.

В нашей практике были случаи, когда комплект фотошаблонов передавался с одного завода на другой вместе с информацией по тех. процессу, и новый завод начинал изготовление по новому тех. процессу. Если у вас есть только фотошаблоны, а данных по тех. процессу нету, или тех. процесс включает некие спеицифичные шаги, которые невозможно повторить на наличствующем оборудовании, то вероятность успешного выпуска сильно снижается. Но опять же, я не представляю ни один из заводов, это только мое мнение и моя практика. Лучше поискать на том же линкдине работников заводов и попытаться «изнутри» узнать о такой возможности.

0

В вашем случае проще и лучше не копировать шаблоны, а пенести на базис КМОП БМК логическую модель вашего чипа и получить другое, но пин-совместимое изделие.

+1

Хороший совет.

Но есть «но».

1. SID — аналого-цифровая микросхема.

2. Умельцы многократно копировали его и на микроконтроллерах с обвязкой, и на FPGA.

3. Для любителей старины и прочих ламповых аудиофилов (на SID делают музыкальные инструменты) это будет «подделкой». Его откроют первым же делом, и тут окажется «а SID-то не настоящий!»

4. Не всё просто копируется логикой и не просто так заставить это потом работать поскольку есть нюансы. Внутри даже 8-битных процов есть куча старых, милых приколов основанных чисто на транзисторах, типа bus precharge. Умельцы умудрились «выловить» программно диагностируемые отличия Z80 которые вылезли при смене технологии NMOS -> CMOS, и при передирании Z80 на наших заводах.

Но есть «но».

1. SID — аналого-цифровая микросхема.

2. Умельцы многократно копировали его и на микроконтроллерах с обвязкой, и на FPGA.

3. Для любителей старины и прочих ламповых аудиофилов (на SID делают музыкальные инструменты) это будет «подделкой». Его откроют первым же делом, и тут окажется «а SID-то не настоящий!»

4. Не всё просто копируется логикой и не просто так заставить это потом работать поскольку есть нюансы. Внутри даже 8-битных процов есть куча старых, милых приколов основанных чисто на транзисторах, типа bus precharge. Умельцы умудрились «выловить» программно диагностируемые отличия Z80 которые вылезли при смене технологии NMOS -> CMOS, и при передирании Z80 на наших заводах.

0

30Круб это цена одного кристалла БМК или пластина(wafer)? Если пластина, сколько на ней кристаллов БМК?

0

Судя по фото автора, БМК на 500 вентилей 2*2 мм размером. Судя опять же по той же фотографии, аналогичный БМК на 3к вентилей должен быть примерно 4*4 мм. С 100 мм пластины должно получаться больше тысячи чипов 2*2 и штук триста чипов 4*4.

0

Пластины, конечно. С оценкой по количеству amartology почти угадал. Кристаллов на 3к вентилей получается 120, кристаллов на 0.5к — 390.

0

Спасибо! Просто вы пишите про студентов и обучение, а экономику и технологию процессов для обучения не приводите.

Т.е. за 1 раз 20-30 студентов могут заполнить пластину проектами из расчета что 1 студент это 3-4 проекта(или одинаковых чипа с учетом брака) плюс преподаватель свои исследовательские проекты вставит.

Не очень понятно про тестирование — надо ВУЗу иметь тестовое оборудование или оно есть на заводе и надо только оформить тест чтобы на заводе проверили что получилось?

Тесты они автоматически формируются при проектировании или студент должен их подготовить?

Т.е. за 1 раз 20-30 студентов могут заполнить пластину проектами из расчета что 1 студент это 3-4 проекта(или одинаковых чипа с учетом брака) плюс преподаватель свои исследовательские проекты вставит.

Не очень понятно про тестирование — надо ВУЗу иметь тестовое оборудование или оно есть на заводе и надо только оформить тест чтобы на заводе проверили что получилось?

Тесты они автоматически формируются при проектировании или студент должен их подготовить?

0

Все несколько сложнее. На одной пластине может выпускаться несколько кристаллов, в нашем случае — до 4-х. Но это только для маленьких кристаллов. Для БМК на 3к вентилей уже идет только 1 кристалл на пластину. С т.з. производства иметь пластину с десятком разных кристаллов не рационально все же.

Не привожу, потому что объем статьи и так очень большой.

Самый дешевый вариант выглядит так: группа студентов из 20 человек делится на команды по 5 человек. Внутри команды у них разделение ролей: схемотехника, топология, верификация и т.д. За время дипломного проекта выпускается 4 пластины. 2 — для первого запуска, и 2 — с исправлением ошибок. Это получается 120к рублей на полтора года, т.е. меньше 1к/месяц/студент, что примерно равно нынешней стипендии, или, например, бесплатному(для студента) летнему лагерю на две недели на Волге(если речь про МИФИ).

Вариаций на самом деле море, можно повернуть методику так, как будет удобнее конкретному ВУЗу. Можно на одном кристалле тестировать несколько схем, например.

Что касается тестирования, то тут возможны варианты. Лучше, конечно, иметь договор с предприятием, у которого есть оборудование, и готовить тестовые вектора. Тесты студент должен составить сам, а вот тестовые вектора для измерительной установки из среды моделирования получаются средствами САПР.

Не привожу, потому что объем статьи и так очень большой.

Самый дешевый вариант выглядит так: группа студентов из 20 человек делится на команды по 5 человек. Внутри команды у них разделение ролей: схемотехника, топология, верификация и т.д. За время дипломного проекта выпускается 4 пластины. 2 — для первого запуска, и 2 — с исправлением ошибок. Это получается 120к рублей на полтора года, т.е. меньше 1к/месяц/студент, что примерно равно нынешней стипендии, или, например, бесплатному(для студента) летнему лагерю на две недели на Волге(если речь про МИФИ).

Вариаций на самом деле море, можно повернуть методику так, как будет удобнее конкретному ВУЗу. Можно на одном кристалле тестировать несколько схем, например.

Что касается тестирования, то тут возможны варианты. Лучше, конечно, иметь договор с предприятием, у которого есть оборудование, и готовить тестовые вектора. Тесты студент должен составить сам, а вот тестовые вектора для измерительной установки из среды моделирования получаются средствами САПР.

+1

Т.е. для 0.5к на пластине 390 кристаллов по максимум 4 проектам, а для 3к — 120 по 1 проекту.

Мне кажется зря не приводите, так хоть каждый преподаватель/завкафедрой сможет примерить на свои возможности введение в курс такой практики.

Мне кажется зря не приводите, так хоть каждый преподаватель/завкафедрой сможет примерить на свои возможности введение в курс такой практики.

0

Просто такая оценка не совсем корректная. Заводов много, технологические возможности разные, предприятий производителей БМК тоже много. А вы мою внутреннюю кухню хотите представить как некий срез данных. Но это же совсем не так! Много данных было бы упущено, а я все таки хотел дать обзорную статью с широким взглядом на ситуацию.

Ну и опять же. На один кристалл 0.5к вы можете уместить много разных схем, если речь вести про аналоговые схемы. Да даже и цифровые, например, разные архитектуры сумматоров. На одном кристалле может работать несколько команд студентов, вполне.

Это уже вопрос возможностей и желаний кафедр/институтов и их студентов. Если кто-то вдруг захочет обсудить возможность работы в таком направлении через предприятие, где я работаю — велкам в личку, нам это было бы интересно.

Ну и опять же. На один кристалл 0.5к вы можете уместить много разных схем, если речь вести про аналоговые схемы. Да даже и цифровые, например, разные архитектуры сумматоров. На одном кристалле может работать несколько команд студентов, вполне.

Это уже вопрос возможностей и желаний кафедр/институтов и их студентов. Если кто-то вдруг захочет обсудить возможность работы в таком направлении через предприятие, где я работаю — велкам в личку, нам это было бы интересно.

0

думаю, в принципе отсутствие возможности работы с физ лицами.

0

Как разработчик БМК и микросхем на основе БМК не могу пройти мимо и не вставить свои пять копеек:

Если мы говорим про обучение будущих кадров и приобретении опыта, то маленькие БМК с древними САПРами («Невод» и «Ковчег») следует отмести сразу. Мы же хотим утолить «кадровый голод»?? Значит, нужно людям сразу давать нормальные САПРы и нормальные БМКшные базы. ПО от Cadence прекрасно подходит для работы с современными БМК, начинающий разработчик сможет увидеть и использовать все актуальные методологии проектирования.

А работа с однометалльным БМК с поликремниевыми «поднырами» — зло.

Генерация тактового сигнала из сигнала данных — двойное зло (руки бы поотрывать, простите).

Не спорю, что умение собирать схему вручную является хорошим навыком, но намного правильнее прививать молодому разработчику современную культуру синтеза нетлиста из RTL. Опять же, критические участки всегда можно переписать на вентильном уровне.

Трассировка вручную — зачем?? Лучше почитать объёмные мануалы по тому же Encounter'у / Innovus'у, там есть это всё: и как трассировать автоматом/полуавтоматом/вручную, и контроль нагрузочных способностей, и т.д. и т.п.

Все эти навыки вряд ли пригодятся при разработке конкурентоспособных микросхем, это трата времени. Если цель — сделать микросхему на основе древних БМК и поставить на полочку, мол, «я сделал», то да, вся эта возня стоит выделки. Если же цель — набраться опыта для удовлетворения хотелок будущего работодателя, то затея плоха: людей приходится переучивать, тратится драгоценное время (которого, как вы знаете, всегда не хватает..)

Если мы говорим про обучение будущих кадров и приобретении опыта, то маленькие БМК с древними САПРами («Невод» и «Ковчег») следует отмести сразу. Мы же хотим утолить «кадровый голод»?? Значит, нужно людям сразу давать нормальные САПРы и нормальные БМКшные базы. ПО от Cadence прекрасно подходит для работы с современными БМК, начинающий разработчик сможет увидеть и использовать все актуальные методологии проектирования.

А работа с однометалльным БМК с поликремниевыми «поднырами» — зло.

Генерация тактового сигнала из сигнала данных — двойное зло (руки бы поотрывать, простите).

Не спорю, что умение собирать схему вручную является хорошим навыком, но намного правильнее прививать молодому разработчику современную культуру синтеза нетлиста из RTL. Опять же, критические участки всегда можно переписать на вентильном уровне.

Трассировка вручную — зачем?? Лучше почитать объёмные мануалы по тому же Encounter'у / Innovus'у, там есть это всё: и как трассировать автоматом/полуавтоматом/вручную, и контроль нагрузочных способностей, и т.д. и т.п.

Все эти навыки вряд ли пригодятся при разработке конкурентоспособных микросхем, это трата времени. Если цель — сделать микросхему на основе древних БМК и поставить на полочку, мол, «я сделал», то да, вся эта возня стоит выделки. Если же цель — набраться опыта для удовлетворения хотелок будущего работодателя, то затея плоха: людей приходится переучивать, тратится драгоценное время (которого, как вы знаете, всегда не хватает..)

+6

Вы просто пропустили абзац, в котором я объясняю, почему именно маленькие БМК надо разрабатывать и трассировать вручную :) Если вкратце, то на таких объемах человеческий труд в разы эффективнее любого синтезатора.

К тому же, не забывайте про аналоговые схемы — тут синтезаторы никому не нужны, а хорошие аналоговые схемы по-прежнему в моде.

Касательно остальных замечаний на эмоциях(видимо), то здесь ответ простой. Пока канальные БМК приносят прибыль, они никуда с рынка не уйдут.

Что касается маршрута, то тут я уже упустил это в статье — и так огромная получилась. Не знаю, что там с Неводом и Ковчегом, а лично мой текущий маршрут позволяет легко и бесшовно интегрировать и цифровую разработку БМК, и аналоговую, в современные маршруты проектирования. И говоря про разработку на БМК, я имел ввиду как раз такое применение, что видно по таблице сравнения. Если запутал — извиняйте ;)

Еще одна проблема больших БМК, это размер проекта. Лично я не уверен, что студент может сделать схему на, условно, 100к вентилей и при этом целиком понять что и где он сделал :) А стоить будет больше, выпускаться — дольше.

PS. Я тоже за пример университета Цюриха, где можно по 180нм дипломный проект выпустить. Но кто ж нам даст…

К тому же, не забывайте про аналоговые схемы — тут синтезаторы никому не нужны, а хорошие аналоговые схемы по-прежнему в моде.

Касательно остальных замечаний на эмоциях(видимо), то здесь ответ простой. Пока канальные БМК приносят прибыль, они никуда с рынка не уйдут.

Что касается маршрута, то тут я уже упустил это в статье — и так огромная получилась. Не знаю, что там с Неводом и Ковчегом, а лично мой текущий маршрут позволяет легко и бесшовно интегрировать и цифровую разработку БМК, и аналоговую, в современные маршруты проектирования. И говоря про разработку на БМК, я имел ввиду как раз такое применение, что видно по таблице сравнения. Если запутал — извиняйте ;)

Еще одна проблема больших БМК, это размер проекта. Лично я не уверен, что студент может сделать схему на, условно, 100к вентилей и при этом целиком понять что и где он сделал :) А стоить будет больше, выпускаться — дольше.

PS. Я тоже за пример университета Цюриха, где можно по 180нм дипломный проект выпустить. Но кто ж нам даст…

+2

Насчёт рынка вы, безусловно, правы: если есть заказы, то будет и спрос на исполнителя.

Видимо, для студента сначала стоит определить, под какие технологии он хочет разрабатывать (в начале своей, хм, карьеры). Проблем и задач полно, что в микронных нормах, что в субмикронных (а если говорить про спецстойкость, то тут ещё вопрос, что лучше :) ). И если работодателю нужны именно такие спецы, то, да, условные 30 (50?? 100?? не важно) тысяч рублей для вовлечения студентов в дивный мир разработки микросхем вполне оправданы.

Но за всем этим нужен строгий контроль и проверка того, понимает ли человек, что он делает и зачем он это делает.

Видимо, для студента сначала стоит определить, под какие технологии он хочет разрабатывать (в начале своей, хм, карьеры). Проблем и задач полно, что в микронных нормах, что в субмикронных (а если говорить про спецстойкость, то тут ещё вопрос, что лучше :) ). И если работодателю нужны именно такие спецы, то, да, условные 30 (50?? 100?? не важно) тысяч рублей для вовлечения студентов в дивный мир разработки микросхем вполне оправданы.

Но за всем этим нужен строгий контроль и проверка того, понимает ли человек, что он делает и зачем он это делает.

0

На мой взгляд студенту за время обучения надо попробовать как можно большое, чтобы понять, чем они хотят заниматься. В МИФИ например на 4м курсе студенты не знают, что такое верификация. В принципе. Вот как так?) Да собственно и потом тоже не знают, потому что этому никто не учит. Вроде в МИЭТе получше с этим, но есть ли там практика применения тулов в реальном проекте? За другие ВУЗы я просто совсем не в курсе, может местные подскажут что и как.

А на счет контроля это очень верно. Обязательно должен быть ведущий всех этих обучающих проектов. Причем желательно не от института, а практикующий, и не зависящий от ректората в плане дисциплинарных решений. Не выполнили этап маршрута — свободны, не занимайте место.

А то когда нулевые дипломы на тройку натягивают… тоска.

А на счет контроля это очень верно. Обязательно должен быть ведущий всех этих обучающих проектов. Причем желательно не от института, а практикующий, и не зависящий от ректората в плане дисциплинарных решений. Не выполнили этап маршрута — свободны, не занимайте место.

А то когда нулевые дипломы на тройку натягивают… тоска.

0

В минском БГУИРе (закончил 4 года назад) САПР был отрывочным но мы попробовали все и поэтапно: отдельно моделирование технологии в Silvaco (Athena, Atlas) + чуток приборного моделирования получившейся кристальной структуры (для тех кому было мало, был еще Synopsis и всякие Ab-initio CADs), отдельно схемотехническое моделирование в Cadence как «цифры», так и аналоговых схем, отдельно топологическое проектирование там же со всеми «танцами с бубном» по минимизации площади, соблюдения design rules и борьбы с паразитными емкостями между шинами, методами монте-карло и параметрическими анализами. В конце 4го курса был курсовой, где мне выпал 4х-разрядный сумматор по 180 мкм кмоп технологии. Сначала нужно было прописать типовой маршрут изготовления, промоделировав его, потом и собственно полученную кмоп-структуру (все в Silvaco), затем уже ручками собираешь уже в Cadenсe из этих транзисторов все логические элементы от элементарного инвертора до 3XOR и самого сумматора, моделируешь в связке схема-топология с проверкой всех таблиц истинности и расчета фронтов. В общем, было весело. Сейчас кажется просто, но на тот момент это была миссия невыполнима.

К сожалению, большинству из нас, когда к 5 курсу нам по программе попытались дочитать про Verilog i VHDL, было почему-то не до этого. Но в целом впечатление дали полное, те же БМК в какой-то DOS-программе собирали в каком-то из семестров. И перед каждым практическим этапом познания современных САПР, была естественно теория, ну и ходили на Интеграл в цеха конечно.

Проблема у нас была в другом, в наших бестолковых головах с парой извилин. Не смотря на вполне качественную программу, через нас (большинство) всё проходило, как вода сквозь дуршлаг.

К сожалению, большинству из нас, когда к 5 курсу нам по программе попытались дочитать про Verilog i VHDL, было почему-то не до этого. Но в целом впечатление дали полное, те же БМК в какой-то DOS-программе собирали в каком-то из семестров. И перед каждым практическим этапом познания современных САПР, была естественно теория, ну и ходили на Интеграл в цеха конечно.

Проблема у нас была в другом, в наших бестолковых головах с парой извилин. Не смотря на вполне качественную программу, через нас (большинство) всё проходило, как вода сквозь дуршлаг.

+2

зачем??

Мне как технологу ранее кристального, теперь уже сборочного производства, подобные умения, полученные в университете именно за счет «ручной» проработки каждого этапа проетирования ИС, помогает решать обратные задачи:

Где накосячили гореразработчики, когда у меня ОКРы, а иногда и серийка никак не может достигнуть плановых процентов выхода, одни нулевые партии пластин/приборов, на полностью отработанной технологии и отсутствии каких-либо сбоев в оборудовании.

+2

(немного оффтоп) Ооо, по личному опыту скажу, что если бы в головы горе-разработчикам вбили тезис «Слово технолога — закон», то косяков было бы меньше.

Не надо спорить с технологами. Это как спорить с хирургом во время операции. Если, конечно, технология отлажена и правила проектирования присутствуют. Когда мне технолог говорит «делай так», я не пытаюсь «обхитрить» и извратиться, забивая на правила. К сожалению, в нашей местечковой реальности часть разработчиков считает, что правила писаны не для них, да и вообще, «зачем верификация??». В итоге… ну, не мне вам рассказывать. А казалось бы, взрослые, образованные люди.

А так-то, конечно, все знания полезны, их много не бывает, никто тут спорить не будет.

Не надо спорить с технологами. Это как спорить с хирургом во время операции. Если, конечно, технология отлажена и правила проектирования присутствуют. Когда мне технолог говорит «делай так», я не пытаюсь «обхитрить» и извратиться, забивая на правила. К сожалению, в нашей местечковой реальности часть разработчиков считает, что правила писаны не для них, да и вообще, «зачем верификация??». В итоге… ну, не мне вам рассказывать. А казалось бы, взрослые, образованные люди.

А так-то, конечно, все знания полезны, их много не бывает, никто тут спорить не будет.

0

В современной fabless-модели разработки и производства слово технолога и есть закон. Какой процесс и правила дали, с теми и работаешь, любой маленький шаг в сторону — будь добр подписать бумагу, снимающую с фабрики ответственность за результат. Любой большой шаг в сторону — и твой чип просто без лишних слов не примут в производство.

0

Во первых спасибо за действительно интересную статью.

Хотелось бы вы внесли некоторую ясность, почему вы считаете, что при проектировании на ПЛИС не происходит работа в современных САПРах, не нужно понимание работы синтезатора, понимание требований констрейнтов, нет возможности делать размещение, и нет возможности делать моделирование с экстракцией?

Во-первых, есть ПЛИС, которые хорошо прототипируют ASIC серия так и называется ProASIC, делает Actel (Microsemi). В LiberoIDE, например, вы абсолютно так же как и с БМК можете работать напрямую с библиотекой, так же при желании можете сделать схему вручную и сами же вручную сделать её размещение, трассировка правда будет все равно автоматическая и нужное кол-во буферов система поставит сама, но это можно и отдельно объяснить студентам.

Во-вторых любая САПР, работающая с ПЛИС выдаст вам файл с задержками, который так же нужно подключить к системе моделирования.

В-третьих Ваш подход с проектирование без тестирования как раз очень хорошо подходит для работы с ПЛИС: спроектировал устройство -> прошил, если не заработало -> разобрался почему, если не разобрался -> воткнул SignalTAP -> разобрался почему… Вот как раз здесь цена ошибки 0р (естественно при использовании хороших демо плат), что при обучении очень полезно. В вашем случае цена ошибки 30к рублей. Я лично ещё не встречал студента, который мне с первого раза банальный счетчик без ошибок написал даже на Verilog, спроектировать с первого раза же рабочий БМК не получилось даже у вас, а вы наверное уже не студент. И здесь кроется большая проблема, неправильная и неработающая схема, которую уже не исправить это отрицательная обратная связь, которая легко может оттолкнуть студента от развития в данной области в дальнейшем…

В-четвертых работа с зондами это хорошо, но вопрос в том, что врят ли в нормальной фирме, человек который пишет код, сам же настраивает и проводит тестирование на данном оборудование, в лучшем случае разработчик получит набор откликов, снимать же осциллограммы можно и с ПЛИС.

В-пятых при обучении важно понимать, кого мы учим, а варианты здесь, как минимум, такие: RTL-программист, схемотехник, верификатор, тополог, технолог. Каждый должен развивать навыки в своей области, при небольшом понимании смежных.

В-шестых я бы на вашем месте не был бы столь категоричен в отношении современных систем синтеза, они очень хорошо умеют оптимизировать и синтезировать правильно написанный код, крайне сложно самому спроектировать схему лучше, чем это за вас сделает синтезатор используя правильно написанный вами RTL-код.

По поводу БМК, для маленьких БМК, которые в принципе достаточно бесполезны, кроме как на замену рассыпухи ваш процесс проектирования может и подходит. Для любых проектов, где емкость измеряется в сотнях тысяч вентилей все равно нужен САПР синтеза их для этого и придумали, что спроектировать верную схему такого кристалла вручную очень сложно.

Ну и от себя добавлю мой опыт работы с БМК такой:

1) Пишем RTL код.

2) Параллельно другие люди пишут тестовую систему.

3) Моделируем RTL.

4) Отправляем на предприятие на синтез, обратно получаем синтезируемую схему в базисе БМК, можно и самому синтезировать, но вот цена софта… да и библиотека кстати не всегда открыта…

5) Моделируем полученную схему в той же тестовой системе, что и RTL, если обнаруживаются несоответствия или схема получилась слишком большой, исправляем и отправляем опять на синтез, если ошибок не обнаружено, то переходим к пункту 6.

6) На предприятии из полученной схемы отдельные люди делают топологию, на выходе получается файл схемы и файл, содержащий задержки.

6) Моделируем схему с задержками, если находим ошибки или не укладываемся во время, опять все исправляем и отправляем на синтез, далее по кругу пока все не исправим. Если все хорошо, то идем далее.

7) Предприятие изготавливает кристалл.

8) Параллельно вытаскиваем из тестовой системы файл воздействий и откликов для оборудования, которое будет тестировать кристалл. Отправляем этот файл на предприятие.

9) Предприятие тестирует кристалл, если тесты проходят, то его корпусируют и присылают заказчику.

10) Далее уже вставляем полученный чип в тестовую плату и тестируем на стенде.

Некоторые производители позволяют до пункта 6 синтезировать схему в базис имитатора на ПЛИС и проверить микросхему на том же посадочном месте и реальной плате и стенде, что и в последствии спроектированный чип.

Я понимаю, что вы вполне знаете подобный маршрут, я лишь хочу ещё раз отметить… Что нужно разделять разработчика, верификатора и тополога и учить их по-разному.

И ещё одно дополнение, нужно понимать, что такое обилие БМК в нашем отечестве возникло не от хорошей жизни, а потому что наше отечество не умеет делать ПЛИС… При наличии хороших ПЛИС необходимость в БМК отпадает, это кстати подтверждает обильное использование на западе да и у нас ПЛИС в авиации и космонавтике…

Хотелось бы вы внесли некоторую ясность, почему вы считаете, что при проектировании на ПЛИС не происходит работа в современных САПРах, не нужно понимание работы синтезатора, понимание требований констрейнтов, нет возможности делать размещение, и нет возможности делать моделирование с экстракцией?

Во-первых, есть ПЛИС, которые хорошо прототипируют ASIC серия так и называется ProASIC, делает Actel (Microsemi). В LiberoIDE, например, вы абсолютно так же как и с БМК можете работать напрямую с библиотекой, так же при желании можете сделать схему вручную и сами же вручную сделать её размещение, трассировка правда будет все равно автоматическая и нужное кол-во буферов система поставит сама, но это можно и отдельно объяснить студентам.

Во-вторых любая САПР, работающая с ПЛИС выдаст вам файл с задержками, который так же нужно подключить к системе моделирования.

В-третьих Ваш подход с проектирование без тестирования как раз очень хорошо подходит для работы с ПЛИС: спроектировал устройство -> прошил, если не заработало -> разобрался почему, если не разобрался -> воткнул SignalTAP -> разобрался почему… Вот как раз здесь цена ошибки 0р (естественно при использовании хороших демо плат), что при обучении очень полезно. В вашем случае цена ошибки 30к рублей. Я лично ещё не встречал студента, который мне с первого раза банальный счетчик без ошибок написал даже на Verilog, спроектировать с первого раза же рабочий БМК не получилось даже у вас, а вы наверное уже не студент. И здесь кроется большая проблема, неправильная и неработающая схема, которую уже не исправить это отрицательная обратная связь, которая легко может оттолкнуть студента от развития в данной области в дальнейшем…

В-четвертых работа с зондами это хорошо, но вопрос в том, что врят ли в нормальной фирме, человек который пишет код, сам же настраивает и проводит тестирование на данном оборудование, в лучшем случае разработчик получит набор откликов, снимать же осциллограммы можно и с ПЛИС.

В-пятых при обучении важно понимать, кого мы учим, а варианты здесь, как минимум, такие: RTL-программист, схемотехник, верификатор, тополог, технолог. Каждый должен развивать навыки в своей области, при небольшом понимании смежных.

В-шестых я бы на вашем месте не был бы столь категоричен в отношении современных систем синтеза, они очень хорошо умеют оптимизировать и синтезировать правильно написанный код, крайне сложно самому спроектировать схему лучше, чем это за вас сделает синтезатор используя правильно написанный вами RTL-код.

По поводу БМК, для маленьких БМК, которые в принципе достаточно бесполезны, кроме как на замену рассыпухи ваш процесс проектирования может и подходит. Для любых проектов, где емкость измеряется в сотнях тысяч вентилей все равно нужен САПР синтеза их для этого и придумали, что спроектировать верную схему такого кристалла вручную очень сложно.

Ну и от себя добавлю мой опыт работы с БМК такой:

1) Пишем RTL код.

2) Параллельно другие люди пишут тестовую систему.

3) Моделируем RTL.

4) Отправляем на предприятие на синтез, обратно получаем синтезируемую схему в базисе БМК, можно и самому синтезировать, но вот цена софта… да и библиотека кстати не всегда открыта…

5) Моделируем полученную схему в той же тестовой системе, что и RTL, если обнаруживаются несоответствия или схема получилась слишком большой, исправляем и отправляем опять на синтез, если ошибок не обнаружено, то переходим к пункту 6.

6) На предприятии из полученной схемы отдельные люди делают топологию, на выходе получается файл схемы и файл, содержащий задержки.

6) Моделируем схему с задержками, если находим ошибки или не укладываемся во время, опять все исправляем и отправляем на синтез, далее по кругу пока все не исправим. Если все хорошо, то идем далее.

7) Предприятие изготавливает кристалл.

8) Параллельно вытаскиваем из тестовой системы файл воздействий и откликов для оборудования, которое будет тестировать кристалл. Отправляем этот файл на предприятие.

9) Предприятие тестирует кристалл, если тесты проходят, то его корпусируют и присылают заказчику.

10) Далее уже вставляем полученный чип в тестовую плату и тестируем на стенде.

Некоторые производители позволяют до пункта 6 синтезировать схему в базис имитатора на ПЛИС и проверить микросхему на том же посадочном месте и реальной плате и стенде, что и в последствии спроектированный чип.

Я понимаю, что вы вполне знаете подобный маршрут, я лишь хочу ещё раз отметить… Что нужно разделять разработчика, верификатора и тополога и учить их по-разному.

И ещё одно дополнение, нужно понимать, что такое обилие БМК в нашем отечестве возникло не от хорошей жизни, а потому что наше отечество не умеет делать ПЛИС… При наличии хороших ПЛИС необходимость в БМК отпадает, это кстати подтверждает обильное использование на западе да и у нас ПЛИС в авиации и космонавтике…

+3

Тут скорее момент не в том, что я чем-то категорично не согласен, а с тем, что тематика настолько обширная, что уместить всё в одну статью решительно невозможно :) И так получилось очень много, а ведь статья вроде для широкого круга читателей предназначалась. Понятное дело, что специалисты в этой статье «дыр» и «шероховатостей» могут найти вагон и маленькую тележку, я и сам их вижу.

Поэтому про ПЛИС я обсуждать не буду, а просто соглашусь :)

(Upd. Все же скажу. Тот уровень, на котором при работе с ПЛИС, требуется хорошее понимание перечисленных вещей зачастую настолько далек от реалий студенческих курсовых проектов, что я счел возможным отметить пункты отсутствующими в программе. Во всяком случае во время моего обучения именно так и было. Сданный на третьей неделе семестра курсовой и семестр халявы вместо курса про Verilog)

Касательно следующих пунктов.

3. У меня не получилось, потому что я бился обо все углы сам. Предполагается, что в институте будет курс, следуя которому вероятность «выстрела в ногу» будет пренебрежительно мала.

4. Нормальная фирма это какая? 100млн оборота в год? 200? Или миллиард? Или другие оценки? Или 20 гос. ОКР в год?)

5. Это идеальный вариант. Вот только как студент узнает, что ему по душе, если не попробует? А так можно и в стандарт целл дизайн пойти.

6. А сколько вы БМК спроектировали вручную? Я столь категоричен, потому что у меня есть все основания так полагать. И ни в одной беседе, ни один собеседник, не смог привести примера, когда синтезатор подошел бы хотя бы близко к ручной работе. А вот примеры обратного процесса, когда ПЛИС 20к LUT укладывается в 3к вентилей есть(озвучивать не буду, разве что в личку).

Ну и про маленькие БМК. Вы все мыслите категориями сотен тысяч вентилей, потому что у вас проекты свои такие. Но я вас уверяю, что даже для БМК на 500 вентилей есть место на рынке, объемом в сотни миллионов рублей.

А что касается замены БМК ПЛИСами, то тут опять же есть свои нюансы. ПЛИС — это огромная, избыточная, дорогая, прожорливая схема. Если в каком-то применении эти параметры начинают сильно мешать, то люди ищут другие варианты. Один из них — БМК. А в целом, конечно, ПЛИС удобнее для разработчика. Особенно, если надо десять штук в год.

Поэтому про ПЛИС я обсуждать не буду, а просто соглашусь :)

(Upd. Все же скажу. Тот уровень, на котором при работе с ПЛИС, требуется хорошее понимание перечисленных вещей зачастую настолько далек от реалий студенческих курсовых проектов, что я счел возможным отметить пункты отсутствующими в программе. Во всяком случае во время моего обучения именно так и было. Сданный на третьей неделе семестра курсовой и семестр халявы вместо курса про Verilog)

Касательно следующих пунктов.

3. У меня не получилось, потому что я бился обо все углы сам. Предполагается, что в институте будет курс, следуя которому вероятность «выстрела в ногу» будет пренебрежительно мала.

4. Нормальная фирма это какая? 100млн оборота в год? 200? Или миллиард? Или другие оценки? Или 20 гос. ОКР в год?)

5. Это идеальный вариант. Вот только как студент узнает, что ему по душе, если не попробует? А так можно и в стандарт целл дизайн пойти.

6. А сколько вы БМК спроектировали вручную? Я столь категоричен, потому что у меня есть все основания так полагать. И ни в одной беседе, ни один собеседник, не смог привести примера, когда синтезатор подошел бы хотя бы близко к ручной работе. А вот примеры обратного процесса, когда ПЛИС 20к LUT укладывается в 3к вентилей есть(озвучивать не буду, разве что в личку).

Ну и про маленькие БМК. Вы все мыслите категориями сотен тысяч вентилей, потому что у вас проекты свои такие. Но я вас уверяю, что даже для БМК на 500 вентилей есть место на рынке, объемом в сотни миллионов рублей.

А что касается замены БМК ПЛИСами, то тут опять же есть свои нюансы. ПЛИС — это огромная, избыточная, дорогая, прожорливая схема. Если в каком-то применении эти параметры начинают сильно мешать, то люди ищут другие варианты. Один из них — БМК. А в целом, конечно, ПЛИС удобнее для разработчика. Особенно, если надо десять штук в год.

+2

3. Ну нормальный курс ещё нужно сделать, как показывает опыт даже на базе ПЛИС очень сложно выстроить понятный курс, на базе БМК я даже боюсь представить где нужно искать такого специалиста, который в рамках курсового сможет студенту рассказать и объяснить все подводные камни.

4. Из тех, что знаю, например, в МЦСТ точно каждый уровень делают разные люди, но там естественно и класс задач другой… В любом случае для меня кажется полный цикл из одного человека это уже перебор, только если это фриланс.

5. Опять же по своему опыту даже RTL интересен очень малому числу студентов, топологи я вещи ниже интересны ещё меньшему числу студентов, но это моя выборка, возможно в МИЭТ найдется больше желающих заниматься топологий

6. В БМК опыт не сильно большой, но в ПЛИС есть некоторый опыт… Так вот большинство попыток сделать лучше синтезатора оказывались не очень удачными, возможно сказывается специфика проектов, возможно их размер… Если не сложно скинте в личку алгоритм…

А можно пример реально мелкого БМК, который выпускается большой серией… Я знаю есть интересные БМК 5503, но не более… Ну и тем более не знаю какие там серии и насколько они окупились…

Ну да для БМК нужна определенная серия больше, чем у ПЛИС, но меньше чистого ASIC. Наверное каждый раз стоит считать отдельно.

И ещё кстати было бы неплохо добавить в начале направления, студентам которых вы хотели бы рекомендовать этот курс…

Ну и ещё по поводу вашей идеи, у нас в институте кафедра, занимающаяся обучением по специальности приборостроение приобрела линейку по производству ПП, вот там в принципе ваш метод работает, но на мой взгляд все же изготовить работающую плату немного легче, чем разработать БМК.

4. Из тех, что знаю, например, в МЦСТ точно каждый уровень делают разные люди, но там естественно и класс задач другой… В любом случае для меня кажется полный цикл из одного человека это уже перебор, только если это фриланс.

5. Опять же по своему опыту даже RTL интересен очень малому числу студентов, топологи я вещи ниже интересны ещё меньшему числу студентов, но это моя выборка, возможно в МИЭТ найдется больше желающих заниматься топологий

6. В БМК опыт не сильно большой, но в ПЛИС есть некоторый опыт… Так вот большинство попыток сделать лучше синтезатора оказывались не очень удачными, возможно сказывается специфика проектов, возможно их размер… Если не сложно скинте в личку алгоритм…

А можно пример реально мелкого БМК, который выпускается большой серией… Я знаю есть интересные БМК 5503, но не более… Ну и тем более не знаю какие там серии и насколько они окупились…

Ну да для БМК нужна определенная серия больше, чем у ПЛИС, но меньше чистого ASIC. Наверное каждый раз стоит считать отдельно.

И ещё кстати было бы неплохо добавить в начале направления, студентам которых вы хотели бы рекомендовать этот курс…

Ну и ещё по поводу вашей идеи, у нас в институте кафедра, занимающаяся обучением по специальности приборостроение приобрела линейку по производству ПП, вот там в принципе ваш метод работает, но на мой взгляд все же изготовить работающую плату немного легче, чем разработать БМК.

+1

У БМК в принципе и сейчас есть сфера применения, если надо сконвертировать ПЛИС в ASIC быстро и недорого. Intel буквально пару недель назад приобрел производителя БМК eASIC, продукты которого уже некоторое время стоят в недрах их серверных процессоров.

ПЛИС это тоже на самом деле решение не от хорошей жизни, а для того, чтобы не платить огромные NRE разработки ASIC.

ПЛИС это тоже на самом деле решение не от хорошей жизни, а для того, чтобы не платить огромные NRE разработки ASIC.

0

Очень любопытно, спасибо!

Но есть три момента:

1. «Допилить» тулы будет непросто, а учить самопальному софту синтеза и лейаута для БМК (Ковчег?) — бессмысленно, поскольку очень уж устарела эта технология.

2. Что потом делать с этой пластиной за 30К? Для просто диплома или обучения слишком дорого. Здесь надо смотреть на опыт зарубежных ВУЗов — там студентам до последнего вдалбливают САПРы, и лишь в исключительных случаях под конкретный грант/задачу делают чип — на деньги гранта. Разумеется, ни о каких БМК речь не идет — есть университетский программы, где выпуск эсик очень дешев, в т.ч. и для РФ. БМК ведь не просто морально устарел, на 2мкм даже мегагерц 50 не выжать, и потребление по современным меркам огромно. Это эпоха 8086 процессоров, динозавр по сути. Боюсь, и задач таких уже нет, где 2 мкм имело бы какой то смысл. Единственное преимущество — стоимость.

3. Эсики проектируют при ВУЗах по университетским программам (европрактис). При МИФИ точно что то подобное было, и при МИЭТ. А в некоторых ВУЗах едва знают как с ПЛИС обращаться, им до эсика как до Китая пешком. Вопрос в другом — а надо ли таких специалистов готовить? Вся ППП страны работает в 99% случаев на государство. Без коммерческой составляющей нет развития, а значит что и специалисты не нужны, и государству нет нужды их готовить. Да и самим специалистам — оно надо? Ведь работа на государство = госслужащие = низкие зарплаты. Меня в институте кормили завтраками, что все уже развивается, все будет. Прошло 20 лет, а что изменилось? Да ничего, технологическое отставание только увеличилось. В нашем отечестве если что и менять, то совсем с другого конца — с развития коммерческой электроники, которая потащит спрос на специалистов, повысит зарплаты и привлекательность профессии, ну а там и ВУЗы подтянутся. Звучит утопично, да и сам процесс не быстрый. Получается, даже если изменения и начнутся, то пройдут десятилетия, прежде чем эффект станет ощутим.

Но есть три момента:

1. «Допилить» тулы будет непросто, а учить самопальному софту синтеза и лейаута для БМК (Ковчег?) — бессмысленно, поскольку очень уж устарела эта технология.

2. Что потом делать с этой пластиной за 30К? Для просто диплома или обучения слишком дорого. Здесь надо смотреть на опыт зарубежных ВУЗов — там студентам до последнего вдалбливают САПРы, и лишь в исключительных случаях под конкретный грант/задачу делают чип — на деньги гранта. Разумеется, ни о каких БМК речь не идет — есть университетский программы, где выпуск эсик очень дешев, в т.ч. и для РФ. БМК ведь не просто морально устарел, на 2мкм даже мегагерц 50 не выжать, и потребление по современным меркам огромно. Это эпоха 8086 процессоров, динозавр по сути. Боюсь, и задач таких уже нет, где 2 мкм имело бы какой то смысл. Единственное преимущество — стоимость.

3. Эсики проектируют при ВУЗах по университетским программам (европрактис). При МИФИ точно что то подобное было, и при МИЭТ. А в некоторых ВУЗах едва знают как с ПЛИС обращаться, им до эсика как до Китая пешком. Вопрос в другом — а надо ли таких специалистов готовить? Вся ППП страны работает в 99% случаев на государство. Без коммерческой составляющей нет развития, а значит что и специалисты не нужны, и государству нет нужды их готовить. Да и самим специалистам — оно надо? Ведь работа на государство = госслужащие = низкие зарплаты. Меня в институте кормили завтраками, что все уже развивается, все будет. Прошло 20 лет, а что изменилось? Да ничего, технологическое отставание только увеличилось. В нашем отечестве если что и менять, то совсем с другого конца — с развития коммерческой электроники, которая потащит спрос на специалистов, повысит зарплаты и привлекательность профессии, ну а там и ВУЗы подтянутся. Звучит утопично, да и сам процесс не быстрый. Получается, даже если изменения и начнутся, то пройдут десятилетия, прежде чем эффект станет ощутим.

+1

1. Для БМК с несколькими слоями металла тулы уже допилены, во всяком случае Cadence. А технология устареет тогда, когда будет коммерчески убыточной. Пока же — прибыльна.

2. Я вам из практики говорю, 2мкм не устарели. Рынок 2мкм технологии исчисляется миллиардами рублей. Это, конечно, не intel, но как по мне — вполне прилично.

3. То, что заявлено, как «есть при ВУЗе» на самом деле может и не быть. Вот вам пример. МИФИ и Cadence проводят ежегодно конференции с частью лекций и частью лабораторных работ.

Я подавал заявку на участие в лабораторной части и во время учебы, и уже после нее. Ни разу мне эту заявку не одобрили. А вы говорите про ASIC.

2. Я вам из практики говорю, 2мкм не устарели. Рынок 2мкм технологии исчисляется миллиардами рублей. Это, конечно, не intel, но как по мне — вполне прилично.

3. То, что заявлено, как «есть при ВУЗе» на самом деле может и не быть. Вот вам пример. МИФИ и Cadence проводят ежегодно конференции с частью лекций и частью лабораторных работ.

Я подавал заявку на участие в лабораторной части и во время учебы, и уже после нее. Ни разу мне эту заявку не одобрили. А вы говорите про ASIC.

0

Грустно слышать. Тоже учился в МИФИ, 3я кафедра. Был только пикад под DOS и программирование мк(PIC). Ни верилога, ни эсика, хотя на кафедре что то уже было организовано — кто то уже рисовал топологию чипов.

Что касается лабораторных работ и лекций кэденс, толку от них не много. Маркетинговая политика кэденса основана на придерживании информации: документация специально куцая, лекции и лабораторки специально неполноценны для того чтобы начать работать, и в рез-те Вы вынужденно докупаете к тулу еще и платный саппорт, который -разумеется — отвечает только на те вопросы, которые вы зададите. Итого, Кэденс продает тулы, потом, отдельно — общие сведения о методике под вывеской трейнингов, и в завершение — платный саппорт, который выдаст недостающую (но не всю) информацию для работы. Так что их лекции и лабы практически бесполезны, Вы ничего не пропустили. Можно просто прочитать их юзергайды — та же информация что в лекциях, и еще пройти RAKи — те же самые лабораторки. К счастью, кроме кэданса существует и другой софт, с гораздо лучшей документацией, по которой проще учить базовые вещи.

Что касается лабораторных работ и лекций кэденс, толку от них не много. Маркетинговая политика кэденса основана на придерживании информации: документация специально куцая, лекции и лабораторки специально неполноценны для того чтобы начать работать, и в рез-те Вы вынужденно докупаете к тулу еще и платный саппорт, который -разумеется — отвечает только на те вопросы, которые вы зададите. Итого, Кэденс продает тулы, потом, отдельно — общие сведения о методике под вывеской трейнингов, и в завершение — платный саппорт, который выдаст недостающую (но не всю) информацию для работы. Так что их лекции и лабы практически бесполезны, Вы ничего не пропустили. Можно просто прочитать их юзергайды — та же информация что в лекциях, и еще пройти RAKи — те же самые лабораторки. К счастью, кроме кэданса существует и другой софт, с гораздо лучшей документацией, по которой проще учить базовые вещи.

0

Ну допустим вбив на HH Verilog можно найти некоторое число вакансий и от более-менее коммерческих фирм. Кстати хорошая зарплата это какая ради интереса?

-1

Вакансии Verilog, это в первую очередь ПЛИС, и только во вторую эсик.

По зарплатам, в Москве с опытом это 80-120к (960к-1.2М в год), в других городах делите на 1.5-3, а, к примеру, в Европе за верилог платят около 65к в год (4М). Выводов не делаю, просто информация.

По зарплатам, в Москве с опытом это 80-120к (960к-1.2М в год), в других городах делите на 1.5-3, а, к примеру, в Европе за верилог платят около 65к в год (4М). Выводов не делаю, просто информация.

+1

Ок, можно объяснить по другому.

Что такое веб дизайнер. Это рабочее место за стоимость компа и стола, и еще такая же сумма на стоимость лиц. софта. Теперь, что такое разработчик эсика. Это стоимость компа и стола + несколько сотен $k в год за лицензию. Из этого следует, почему вебдизайнерам в сотни и тысячи раз проще найти работу. И почему вакансий разработчика эсик было, есть и будет очень мало. Почему практически нет стартапов разработки эсик. Вывод не делаю, но было бы неплохо еще составить диаграмму с числом специалистов, занятых в области, или их совокупный доход в год. Эсик-дизайнеров Вы даже разглядеть не сможете на общем фоне.

Что такое веб дизайнер. Это рабочее место за стоимость компа и стола, и еще такая же сумма на стоимость лиц. софта. Теперь, что такое разработчик эсика. Это стоимость компа и стола + несколько сотен $k в год за лицензию. Из этого следует, почему вебдизайнерам в сотни и тысячи раз проще найти работу. И почему вакансий разработчика эсик было, есть и будет очень мало. Почему практически нет стартапов разработки эсик. Вывод не делаю, но было бы неплохо еще составить диаграмму с числом специалистов, занятых в области, или их совокупный доход в год. Эсик-дизайнеров Вы даже разглядеть не сможете на общем фоне.

+1

Спрос да низкий, но он растущий, но и предложение крайне низкое, тут весь вопрос в том, сколько человек в каждой области претендует на вакансию… Многие вакансии на HH висят чуть ли не годами… Что-то мне подсказывает, что найти Web-дизайнера в разы проще, чем RTL-дизайнера и уж тем более тополога. А дальше каждый сам решает, просто вы крайне категоричны в своих заявлениях, я же могу сказать данный рынок развивается и спрос есть небольшой, но стабильный и на ASIC и на FPGA. И со всей этой канителью с импортозамещением ещё будет развиваться.

0

Я бы не назвал именно рынок эсик-дизайна развивающимся. Развитие, если и есть, то по чайной ложке в год, да и то в Москве (за другие страны СНГ не говорю — не знаю). Опять же, не надо мешать вакансии «верилог» для ПЛИС и для эсик, рынок проектов на ПЛИС, мк, и другой готовой ЭКБ действительно развивается. Далее, большая часть «висящих годами» вакансий — это почтовые ящики, которые хотят все сразу и за копейки. Кому захочется сдать загранпаспорт в сейф начальника в 23 года (после института)? Или, кому захочется менять работу на никому неизвестную организацию, которая появилась из ниоткуда (вспоминаем, что рынок оооочень маленький)? Что касается импортозамещения, заказчик остается тот же — государство. Фактически, это просто поддержание отрасли, но никак не импульс к развитию (поскольку госзаказ, а не коммерческое производство).

0

А как же быть с full custom analog/mixed-signal design?

Насколько я понимаю, аналог в БМК это либо готовые IP, либо какое-то количество транзисторов коммутируемых, поправьте, если я не прав.

Таким образом не получится позаниматься топологией, что для аналога очень важная часть вместе с физической верификацией.

P.S. Я тоже учился в МИФИ, кафедра 3. Спроектировал IP в 180 нм для диплома, изготовили через Europractice. Включить-измерить, к сожалению, смог только через несколько месяцев после защиты, так что вставить красивые картинки в диплом или притащить плату с осциллографом на защиту не вышло. Но при большом желании возможность что-то запустить есть, если не в рамках общего курса, то в рамках НИР точно.

Насколько я понимаю, аналог в БМК это либо готовые IP, либо какое-то количество транзисторов коммутируемых, поправьте, если я не прав.

Таким образом не получится позаниматься топологией, что для аналога очень важная часть вместе с физической верификацией.

P.S. Я тоже учился в МИФИ, кафедра 3. Спроектировал IP в 180 нм для диплома, изготовили через Europractice. Включить-измерить, к сожалению, смог только через несколько месяцев после защиты, так что вставить красивые картинки в диплом или притащить плату с осциллографом на защиту не вышло. Но при большом желании возможность что-то запустить есть, если не в рамках общего курса, то в рамках НИР точно.

+1

Конечно, вот прям full custom не получится. Однако ж транзисторы не скоммутированы, и на БМК вы вполне можете собирать любую аналоговую схему. Разумеется, отработать топологические нюансы в полном объеме не получится. Но от этого схема не становится менее аналоговой :) И опять же для студента того объема знаний, который предлагается, будет более, чем достаточно.

Что касается вашего примера, то об этом и речь. Долго, дорого, эксклюзивно. А надо быстро, дешево и массово. И опять же — «при большом желании». А должно быть по умолчанию.

PS. Вообще существует большой спектр цифро-аналоговых БМК, и там с аналогом получше, но все равно до full-custom, как до луны, конечно.

Что касается вашего примера, то об этом и речь. Долго, дорого, эксклюзивно. А надо быстро, дешево и массово. И опять же — «при большом желании». А должно быть по умолчанию.

PS. Вообще существует большой спектр цифро-аналоговых БМК, и там с аналогом получше, но все равно до full-custom, как до луны, конечно.

0

Насколько я понимаю, аналог в БМК это либо готовые IP, либо какое-то количество транзисторов коммутируемых, поправьте, если я не прав.

БМК бывают с разной степенью интеграции составных частей. По-английски это называется fine grain или coarse grain, подходящий русскоязычнй термин я не смог сход вспомнить.

У Дизайн-центра «Союз» есть 5400 серия аналого-цифровых БМК, в которых есть как «море транзисторов», состоящее из согласованных пар (чтобы собрать дифпару или зеркало тока) и есть уже готовые блоки, от операционников и компараторов до АЦП и ЦАП.

У автора статьи технологии попроще, но, насколько я понимаю, принцип тот же.

Собственно, при наличии хорошо расставленных транзисторов вполне можно показать студенту, как правильно из них собрать common centroid (например в разных вариантах, и потом сравнить смещение нуля), а сильно больше от студенческого проекта и не требуется. Даи будем честны, ananlog/mixed-signal/power дизайнеров требуется намного меньше, чем цифровых.

Но при большом желании возможность что-то запустить есть, если не в рамках общего курса, то в рамках НИР точно.В рамках НИР и при большом желании — это не то же самое, что часть общего учебного процесса.

0

Спасибо, очень интересная статья!

А с точки зрения стоимости разработки, о каких суммах может идти речь? В смысле, допустим, есть некоторый девайс на контроллере (stm32l0) с обвязкой. Всё его предназначение — по нажатию кнопки просыпаться и моргать светодиодом с нужной частотой. До следующего нажатия, которое опять переводит систему в сон. Я понимаю, что без нормального ТЗ оценить сложно. Но хотя бы плюс-минус лапоть, сколько по человеко-часам такое может занять и сколько стоит такая работа?

А с точки зрения стоимости разработки, о каких суммах может идти речь? В смысле, допустим, есть некоторый девайс на контроллере (stm32l0) с обвязкой. Всё его предназначение — по нажатию кнопки просыпаться и моргать светодиодом с нужной частотой. До следующего нажатия, которое опять переводит систему в сон. Я понимаю, что без нормального ТЗ оценить сложно. Но хотя бы плюс-минус лапоть, сколько по человеко-часам такое может занять и сколько стоит такая работа?

0

Вопрос в объемах потребления. Если пара штук в год, то разработка будет дорогой, а если пару тысяч в год, то стоимость разработки «разделится» по серийному выпуску. Из примерно похожего мы делали контроллер для травмата Оса, но экономику того проекта я не знаю.

0

Человеко-часы в смысле выплаты зарплат в этой отрасли ничего не стоят в сравнении со стоимостью лицензий: цена айпи для указанного мк с периферией может перевалить за $50к, стоимость тулов — сотни $k (с лицензией европрактис запрещено делать коммерческие проекты, поэтому ценник совсем другой выходит). Плюс, надо понимать, что на БМК с процессом 2мкм такой мк не сделать: нет флеша, память получится чудовищно огромной, нет IO для современных интерфейсов, да и частоту интерфейсов тоже не удастся вытянуть.

Но! Если Вас устроит процессор уровня 8086 или r3000 (привет из 80х) с параллельным интерфейсом (в лучшем случае rs-232), то БМК 2мкм — Ваш выбор. А еще, не придется платить за айпи и, вероятно, лицензии.

Но! Если Вас устроит процессор уровня 8086 или r3000 (привет из 80х) с параллельным интерфейсом (в лучшем случае rs-232), то БМК 2мкм — Ваш выбор. А еще, не придется платить за айпи и, вероятно, лицензии.

0

Не надо вносить путаницу. Заменить строго определенную функцию некоего устройства, разработанного на мк с обвязкой с помощью БМК можно и экономически выгодно даже на рынке общего применения. Пример тому приведен выше.

А что касается в целом вашего комментария, то не надо пытаться «натянуть» данные из статьи про образовательные БМК на коммерческий рынок.

А что касается в целом вашего комментария, то не надо пытаться «натянуть» данные из статьи про образовательные БМК на коммерческий рынок.

0

Хотите сказать, что у Ангстрема (или где эти 2мкм БМК делают) есть образовательные программы (или просто льготы) для ВУЗов? И софт отдают для обучения студентов?

Мне кажется, Ваша статья это скорее выражение идеи, которую неплохо было бы сделать, но пока этого нет.

Мне кажется, Ваша статья это скорее выражение идеи, которую неплохо было бы сделать, но пока этого нет.

0

Моя статья это безусловно выражение идеи. Что касается реальных примеров, то в различных компаниях в рамках НИРов студентам разрешали/разрешено выпускать собственные кристаллы. Моя же идея в том, чтобы это было на уровне стандарта не в сторонней фирме, а прямо в университете.

Софт для обучения в университеты Cadence предоставляет уже сейчас, и думаю, что немного усилий потребуется для получения студенческих лицензий на Synopsys.

PS. Какие льготы по-вашему еще нужны? Для университетов 30к рублей — копейки. Стоимость обучения сейчас(в МИФИ) — 134к/семестр. На кафедре микроэлектроники студенты учатся 2.5года, всего студентов около 40 в двух группах. Это почти 27 миллионов рублей, затраченных на обучение. Один БМК стоит 30к. Из расчета группового запуска по 4 типа кристаллов на пластине, и минимального запуска на заводе в 2 пластины, получаем 8 запусков по 30к за время обучения. Это менее 1% сверху от общей суммы.

Софт для обучения в университеты Cadence предоставляет уже сейчас, и думаю, что немного усилий потребуется для получения студенческих лицензий на Synopsys.

PS. Какие льготы по-вашему еще нужны? Для университетов 30к рублей — копейки. Стоимость обучения сейчас(в МИФИ) — 134к/семестр. На кафедре микроэлектроники студенты учатся 2.5года, всего студентов около 40 в двух группах. Это почти 27 миллионов рублей, затраченных на обучение. Один БМК стоит 30к. Из расчета группового запуска по 4 типа кристаллов на пластине, и минимального запуска на заводе в 2 пластины, получаем 8 запусков по 30к за время обучения. Это менее 1% сверху от общей суммы.

0

В таком случае, притягиванием за уши занимаюсь Вы не я.

Во-первых потому, что у производителей БМК нет университетских программ — они не делают скидки, не предоставляют софт. Ведь недостаточно просто иметь софт кэденс, нужно иметь библиотеки и все те костыли (скрипты для синтеза, P&R), которые разработаны специально для работы с БМК, без них Вы ничего не спроектируете. Библиотеки передают? Думаю что нет. А если отдавать всю разработку на сторону, то разве студентов Вы учите?

Во-вторых, касательно «Заменить строго определенную функцию некоего устройства, разработанного на мк с обвязкой с помощью БМК». Пример очень и очень плохой, объясню почему. Согласен, что под конкретную задачу автомат можно упростить: у процессора выкинуть неиспользуемую периферию, память, даже отдельные инструкции. Или, спроектировать автомат на основе спецификации, вообще выкинув процессор. Или, спроектировать автомат асинхронным, выкинув к тому же еще и клок. Но! Подобное решение сужает возможности изделия, лишает его гибкости и возможности что то скорректировать. Малейшая ошибка выльется как минимум в переделку масок. Разумеется, можно придумать ситуации, где плюсы перевешивают минусы (Ваш пример с Осой). Но нельзя и спорить с фактом, что мировая тенденция — универсальность. Миллиардными тиражами гонятся дешевые кортесы, стоимость которых копейки, а на этих универсальных мк делаются уже реализации вплоть до задачи мигания диодом. Попробуйте найти программиста писать на асме — таких уже почти не осталось. С точки зрения масс-продакшн влезать в частные решения — экономически дорого и потому в 99% случаев невыгодно. Что будете писать в дипломе/диссертации в части экономического обоснования? Т.е. Ваш случай — отнюдь не типовой, и учить студентов подковывать блоху — не лучшее решение, на мой взгляд.

Ну и в третьих, о цене вопроса. Считать чужие деньги — занятие неблагодарное и бесполезное: надо понимать, что доход от обучения коммерческих студентов распределяется по всему институту, а не тратится на непосредственно на этих студентов. Кафедры этих денег вообще не видят. У кафедр зачастую нет денег даже оборудовать лабораторию дешевыми ПЛИС-макетами, а Вы пишете про выпуск БМК. А если речь о выпуске микросхем за счет студентов (на собственные средства), то не проще ли тогда делать эсики с помощью европрактис? В Европе есть старые фабы, где выпуск MPW очень дешев. Прайса европрактис у меня нет, но минимальный ценник, думаю, сопоставим с 30к. И это будет уже не БМК, а полноценный эсик. А если государство печется именно об отечественном производстве, то почему бы не профинансировать учебные MPW на Микроне, скажем — 250 мкм, или что то более дешевое? Но это уже вопрос не к Вам, а к минОбру.

Во-первых потому, что у производителей БМК нет университетских программ — они не делают скидки, не предоставляют софт. Ведь недостаточно просто иметь софт кэденс, нужно иметь библиотеки и все те костыли (скрипты для синтеза, P&R), которые разработаны специально для работы с БМК, без них Вы ничего не спроектируете. Библиотеки передают? Думаю что нет. А если отдавать всю разработку на сторону, то разве студентов Вы учите?

Во-вторых, касательно «Заменить строго определенную функцию некоего устройства, разработанного на мк с обвязкой с помощью БМК». Пример очень и очень плохой, объясню почему. Согласен, что под конкретную задачу автомат можно упростить: у процессора выкинуть неиспользуемую периферию, память, даже отдельные инструкции. Или, спроектировать автомат на основе спецификации, вообще выкинув процессор. Или, спроектировать автомат асинхронным, выкинув к тому же еще и клок. Но! Подобное решение сужает возможности изделия, лишает его гибкости и возможности что то скорректировать. Малейшая ошибка выльется как минимум в переделку масок. Разумеется, можно придумать ситуации, где плюсы перевешивают минусы (Ваш пример с Осой). Но нельзя и спорить с фактом, что мировая тенденция — универсальность. Миллиардными тиражами гонятся дешевые кортесы, стоимость которых копейки, а на этих универсальных мк делаются уже реализации вплоть до задачи мигания диодом. Попробуйте найти программиста писать на асме — таких уже почти не осталось. С точки зрения масс-продакшн влезать в частные решения — экономически дорого и потому в 99% случаев невыгодно. Что будете писать в дипломе/диссертации в части экономического обоснования? Т.е. Ваш случай — отнюдь не типовой, и учить студентов подковывать блоху — не лучшее решение, на мой взгляд.

Ну и в третьих, о цене вопроса. Считать чужие деньги — занятие неблагодарное и бесполезное: надо понимать, что доход от обучения коммерческих студентов распределяется по всему институту, а не тратится на непосредственно на этих студентов. Кафедры этих денег вообще не видят. У кафедр зачастую нет денег даже оборудовать лабораторию дешевыми ПЛИС-макетами, а Вы пишете про выпуск БМК. А если речь о выпуске микросхем за счет студентов (на собственные средства), то не проще ли тогда делать эсики с помощью европрактис? В Европе есть старые фабы, где выпуск MPW очень дешев. Прайса европрактис у меня нет, но минимальный ценник, думаю, сопоставим с 30к. И это будет уже не БМК, а полноценный эсик. А если государство печется именно об отечественном производстве, то почему бы не профинансировать учебные MPW на Микроне, скажем — 250 мкм, или что то более дешевое? Но это уже вопрос не к Вам, а к минОбру.

-1

Прайса европрактис у меня нет, но минимальный ценник, думаю, сопоставим с 30к.Нууу как сопоставим. Вот актуальный прайс. Минимум, который там есть — 1500 евро за 5 мм2 площади.

Малейшая ошибка выльется как минимум в переделку масок.БМК для того и сделаны, чтобы экономить на переделке масок)

Что же касается мигания диодами при помощи микроконтроллера, то все зависит от тиражей, и для любой функции, от мигания диода до майнинга биткоинов, есть тираж, на котором специализированный чип становится выгоднее програмиируемого универсального (будь то МК или ПЛИС). Кроме этого, есть задачи, где важны такие вещи, как маленький корпус и малое энергопотребление, которых не всегда можно добиться без ASIC. ПЛИС и МК выгоднее при малых тиражах и при очень быстрых сроках выхода на серийное изделие, а не «всегда лучше, потому что такая мировая тенденция». Плюс не забывайте, что у российского рынка есть своя специфика в виде госзаказа, и не всякий «кортекс минимальными тиражами» там можно применить, поэтому резонов делать специализиваронные решения еще больше.

Во-первых потому, что у производителей БМК нет университетских программАвтор поста работает в производителе БМК. Возможно, он как раз и прощупывает почву для такой университетской программы)

0

Я там ниже уже написал, что для учебных целей нет резона делать один чип = один проект. 1.5к евро — сущие копейки. Правда это цена без корпуса, но… я все же считаю что ценник сопоставим.

Что до тиражей, то речь ведь об учебных проектах, верно? ;-) А значит, тираж очень маленький.

По поводу специфики российского рынка — как это соотносится с обучением?

Валер, ты правда думаешь, что студентов надо сразу учить работать на единственного российского заказчика со всей его спецификой? На мой взгляд, это и самому заказчику не выгодно, учитывая отставание в технологиях, и прочие российские нюансы. Государству выгодно это отставание сокращать, а значит — готовить кадры по новому, а не обучать технологиям 2мкм и костылям с БМК. Да и ты сам — пошел бы учиться, зная что тебя будут учить технологиям 20-ти летней давности? Мне кажется, для студента лучше сразу найти подработку на относительно современном предприятии, а институт пусть лучше мат. часть вдалбливает.

Что до тиражей, то речь ведь об учебных проектах, верно? ;-) А значит, тираж очень маленький.

По поводу специфики российского рынка — как это соотносится с обучением?

Валер, ты правда думаешь, что студентов надо сразу учить работать на единственного российского заказчика со всей его спецификой? На мой взгляд, это и самому заказчику не выгодно, учитывая отставание в технологиях, и прочие российские нюансы. Государству выгодно это отставание сокращать, а значит — готовить кадры по новому, а не обучать технологиям 2мкм и костылям с БМК. Да и ты сам — пошел бы учиться, зная что тебя будут учить технологиям 20-ти летней давности? Мне кажется, для студента лучше сразу найти подработку на относительно современном предприятии, а институт пусть лучше мат. часть вдалбливает.

0

Речь не идет об обучении технологии 2 мкм, она идет об обучении при помощи технологии 2 мкм.

Для того, чтобы вдолбить в студента основы матчасти, не нужны ни 14 нм, ни даже 180 нм. Нужно максимально дешево и разумно быстро (вот тут кстати лежит главное преимущество БМК над MPW за границей) пройти со студентом основные пункты маршрута проектирования, используя готовый чип на выходе в качестве мотиватора. Проект «нарисовать схему и топологию сдвигового регистра» на 2 мкм ничем не хуже, чем на 180 нм, серьезно. Разве что два металла было бы круто в первом случае иметь, а не один.

Для того, чтобы вдолбить в студента основы матчасти, не нужны ни 14 нм, ни даже 180 нм. Нужно максимально дешево и разумно быстро (вот тут кстати лежит главное преимущество БМК над MPW за границей) пройти со студентом основные пункты маршрута проектирования, используя готовый чип на выходе в качестве мотиватора. Проект «нарисовать схему и топологию сдвигового регистра» на 2 мкм ничем не хуже, чем на 180 нм, серьезно. Разве что два металла было бы круто в первом случае иметь, а не один.

0

Ты пишешь о кастом дизайне, а автор статьи о сетап-холдах. Думаю, если цель обучения — заказной маршрут, то ты прав. Но если речь только о цифре, то учить надо другим вещам — STA (прекрасно подойдет ПЛИС) и работе с BEOL (прекрасно подойдет и пикад, т.е. элементарный тул для печатных плат). Т.е. цифровая матчасть прекрасно изучается и без проектирования эсик/БМК. Ну а аналог, здесь ты прав, без работы с реальной технологией никак.

0

Вы бы факты проверяли, прежде чем писать такое.

1. Разумеется, библиотеки для проектирования передаются проектирующей организации.

2. У каждого решения свой рынок, не надо безжалостно топить за МК там, где они вообще никому не нужны. По вашим словам я делаю вывод, что вы просто не знакомы с тем рынком, которому вариативность — до лампочки, а люди имеют привычку многократно проверять свои изделия перед запуском в серию(которая может идти потом десятки лет).

3. Считать деньги(свои/чужие) это обязательное занятие, тем более в разговорах про деньги. Вы поленились найти цены на европрактис? Первая ссылка в гугле. Самый дешевый вариант(0.7мкм, ON semi) — 270баксов за 1мм2. Даже если взять кристалл размером, допустим, 3х3 (а с меньшим размером без спец. оборудования уже не поработаешь), то это 9*270*курс=150к рублей за _один_ тип кристалла(30 образцов). Итого в 10 раз дороже варианта с отечественными БМК.