Если вы изучили начала цифровой схемотехники и компьютерной архитектуры по книжке Харрис & Харрис и потом вознамерились пойти собеседоваться на позицию проектировщика микросхем в Apple или NVidia, то вы интервью не пройдете. Посколько вы наверняка получите вопрос про реализацию в хардвере очередей FIFO, а это в Харрис & Харрис не описано.

Хуже того, даже если вы возьмете книжку Digital Design by William Dally & Curtis Harting, которую используют для обучения студентов в Стенфорде, и прочтете ее от корки до корки, то у вас все равно мало шансов, потому что, хотя FIFO там и есть, но в очень базисной форме, а контроль потока данных заканчивается на скид-буферах.

А что же хотят электронные компании?

Даже Dally & Harting - это уровень ~2000-года, а в современной электронной индустрии юный инженер должен владеть кучей трюков, в которые входят не только разнообразные, в том числе извращенные, виды FIFO (на D-триггерах и на SRAM, с однопортовой SRAM или двухпортовой, на одном тактовом сигнале или двух, с несколькими головами или несколькими хвостами, хранящие данные в памяти в виде связанного списка, разделяющие общую память для нескольких FIFO, FIFO с возможностью undo push итд) - но и комбинации этих FIFO с кредитными счетчиками.

Последнее называется credit-based flow control, оно необходимо для построения высокопроизводительных CPU, GPU и сетевых микросхем и применяется для интерфейса конвейерных блоков внутри микросхемы как обобщение того, к чему только прикасался Dally & Harting.

В принципе, этой кухней может овладеть даже способный школьник олимпиадного типа, не говоря уже о студентах. И не только этим, но и другими микроархитектурными штучками - арбитрами, контроллерами банков памяти итд. Проблема в том, что это ноу-хау плохо представлено в учебниках, хотя его можно накопать в патентах, статьях в интернете, на гитхабе (хотя там бывают чудовищно неправильные реализации) и на докладах на международных конференциях.

Чтобы решить эту проблему в России и дать некоторый импульс развитию российских микроэлектронных проектов, которые страдают от недостатка квалифицированных кадров, инициативная группа инженеров и представителей academia решила организовать серию докладов на выставке ChipEXPO-2021, которая пройдет 14-16 сентября в Сколково.

Вот полная программа и регистрация на Секцию 1 (упражнения с FPGA для студентов и продвинутых школьников): http://www.chipexpo.ru/shkola-sinteza-cifrovyh-shem-na-verilog

Регистрация на две другие секции (Секция 2: Микроархитектура, верификация и физическое проектирование микросхем и Секция 3: Продвинутые и экспериментальные методы автоматизации проектирования микросхем): http://www.chipexpo.ru/programm

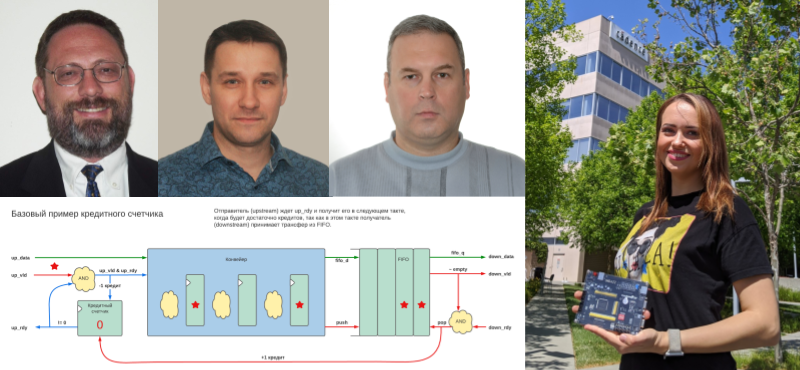

На семинаре будет например доклад от Дэна Гисселквиста, который, согласно блогу компании Symbiotic EDA, разработывал FIFO для ВВС США, а сейчас ведет блог ZipCPU.com и агитирует за использование методов формальной верификации:

А про комбинацию FIFO с кредитными счетчиками расскажет Дмитрий Смехов, инженер-разработчик ПЛИС, компании IRQ, ИнСис и Inline Group. Дмитрий занимается high-frequency trading - быстрой торговлей на бирже с помощью вычислений FPGA. Его доклад называется "Как организовать конвейер для обработки потока данных с максимальной пропускной способностью, минимальным размером памяти и без чрезмерных временных задержек: двойные буфера, очереди и кредитные счетчики".

Дмитрий на снимке в начале поста правее, рядом с девушкой Наташей, которая стоит с FPGA платой рядом с штаб-квартирой компании Cadence. Cadence, Synopsys и Mentor Graphics (ныне Siemens EDA) - триада ведущих разработчиков программ для проектировщиков микросхем.

Да, так вот Дмитрий Смехов начнет с краткого пересказа материала из учебника, который используют в Стенфорде, а потом перейдет к тому, чему в Стенфорде не учат.

А конкретно про FIFO расскажет Сергей Иванец, декан факультета электронных и информационных технологий Черниговского национального технологического университета (Сергей на изображении в начале второй слева, после Дэна Гисселквиста).

Сергей также будет вести второй день практических занятий на платах с микросхемами реконфигурируемой логики FPGA. Эта часть семинара на ChipEXPO будет доступна не только начинающих профессионалам, но и младшим студентам и даже продвинутым школьникам. Сергей будет показывать, как подсоединять к FPGA плате дисплей и рисовать на нем всякие картинки:

В самом Сколково организаторы ChipEXPO, в кооперации с московским вузом МИРЭА поставят штук 20 компьютеров с установленными на них Intel FPGA Quartus и принесут десятка три FPGA плат, но мы все-таки рекомендуем приносить свои ноутбуки и установить на них все заранее. Как это сделать объяснил Сергей Иванец на видео:

Главное отличие секции практических упражнений с FPGA этого года от школы 2020 года - это работа со звуком. Каждый участник получит микрофон и усилитель, и сделает серию экспериментов по распознаванию и генерации звуков.

Вы спросите: "Вы хотите учить школьников и первокурсников DSP и Фурье-преобразованию?" Нет, оказывается, ноты можно распознавать просто подсчетом тактов между пересечением уровня звука среднего значения, так называемым методом zero-crossing. Правда звук для этого должен быть близок к идеальной синусоиде.

Какой же инструмент генерирует звук такой чистоты? Это флейта! На наше мероприятие приедет флейтистка Мария Беличенко, которая сыграет короткие мелодии типа Yesterday Битлз или лирическую песню из сериала Бандитский Петербург, и конечные автоматы на верилоге, спроектированные участниками семинара, будут отличать одну мелодию от другой.

Примеры которые используются в этой части семинара работают со всеми версиями Quartus начиная с 13.0sp1. Желательно конечно использовать последнюю из бесплатных (Lite) версий, но текущая бесплатная версия Quartus Prime Lite Edition 20.1.1 не работает сразу после скачивания ни на текущей версии Windows 10, ни на текущей версии Linux Ubuntu 20.04 LTS. Для Windows у нее истекла дата сертификата драйвера, а для Linux она использует устаревшую библиотеку.

Обе проблемы можно решить: для Windows - c помощью скачивания patch, а для Linux - с помощью "sudo ln -sf /lib/x86_64-linux-gnu/libudev.so.1 /lib/x86_64-linux-gnu/libudev.so.0".

Если вы находитесь не в Москве и хотите поучаствовать в семинаре удаленно, и у вас нет FPGA платы, есть некий резерв FPGA плат, которые будут рассылаться по почте, со следующими ограничениями:

Получатель должен быть или школьником, или преподавателем вуза или школы или кружка, которому интересно внедрить упражения с реконфигурируемой логикой в свою деятельность. Насчет студентов и особенно работающих инженеров мы полагаем, что они могут купить FPGA платы сами - на AliExpress или через российских дистрибуторов.

Получатель должен показать сертификат, что он прошел три небольших онлайн-курса от Роснано «От транзистора до микросхемы», «Логическая сторона цифровой схемотехники» и «Физическая сторона цифровой схемотехники».

Деньги на платы, перевод и трансляцию мероприятия дали: Cadence Design Systems, Siemens EDA / МЕГРАТЕК (Megratec - Mentor Graphics Technologies), Наносемантика, Alchemical Music Box, Максим Маслов (сооснователь Eltechs) и Юрий Панчул.

Сертификат нужен по двум причинам:

Чтобы практический семинар принес пользу, необходимо, чтобы участник четко понимал концепции логического элемента, D-триггера и синтеза языков описания аппаратуры. Все это не программирование. Это проектирование аппаратных структур, несмотря на то, что код на Verilog-е незнакомому с ним человеку выглядит как программа. Все это сразу в голову не ложится - если просто сесть и начать с ним играться как с ардуино, то человек скоро упрется в непонимание что происходит. Поэтому нужно теоретическое предисловие.

Курсы связывают упражнения на FPGA с проектированием высокопроизводительных микросхем в большой индустрии, в которой проектируются микросхемы для айфонов и тесл. Это важно для мотивации, профориентации и перспективы.

Помимо базовой школы по FPGA и секции "что не учат в вузах но спрашивают на собеседования в электронные компании", на семинарах на ChipEXPO еще будут тьюториалы по современным методам функциональной верификации (шикарная ниша для бывших программистов на Java, которым захотелось двинуться в железо - в SystemVerilog есть объектно-ориентированные библиотеки и фреймворки.

Также на ChipEXPO будут:

Эдмунд Хуменбергер, евангелист открытых маршрутов проектирования, которые может быть когда нибудь станут такой же альтернативой Synopsys и Cadence, какой стал Линукс для Windows;

Стив Хувер, основатель стартапа, который сделал язык, автоматизирующий построение конвейера, чтобы вам приходилось меньше разбираться с этим клубком сигналов в коде на Verilog или VHDL;

Роберт Оуэн, известный консультант по образовательным программам (Texas Instruments, ARM, Xilinx) который в этот раз будет от Imagination Technologies - компании, которая в свое время спроектировала GPU внутри ранних Apple iPhone.

И презентации от компаний Cadence Design Systems и Siemens EDA / Mentor Graphics, которые входят в топ-3 разработчиков программного обеспечения для проектировщиков микросхем и поддержали это мероприятие.

Вот так!