В 2015 году скачивания первого русского издания учебника Харрис & Харрис завалили сайт британской компании Imagination Technologies. Книгу стали использовать в МФТИ, ВШЭ МИЭМ, МГУ, МИЭТ, ИТМО и других вузах. С тех пор вышло еще два издания - для ARM и для MIPS, и вот в январе 2022 года выходит новое - для RISC-V - и оно уже доступно для предзаказа.

"Цифровая схемотехника и архитектура компьютера: RISC-V" вероятно станет стандартным учебником в российских вузах, как и источником информации для тех, кто хочет попроектировать процессоры на ПЛИС. Ничего лучшего на рынке нет. Паттерсон-Хеннесси не привязан к курсам по языкам описания аппаратуры и не обсуждает тайминг цифровой логики, а Таненбаум устарел.

Кроме этого, архитектура RISC-V становится билетом в будущее для российских процессорных компаний - Ядро купило Syntacore, Байкал Электроникс инвестировал в CloudBear, Миландр выпустил микроконтроллер с архитектурой RISC-V.

Если же вы не хотите работать в российских компаниях, а хотите пройти интервью на проектировщика чипа в Apple, Intel, NVidia, то и в таком случае учебник Харрисов - это самый эффективный способ начать этот путь.

Об авторах

Дэвид Харрис учился в MIT как раз тогда, когда произошла революция в маршруте проектирования конца 1980-х - начала 1990-х годов. Вооруженный новыми методологиями Дэвид пошел работать в Intel над процессором Pentium II. После этого Дэвид защитил диссертацию в Стенфорде и стал преподавателем в частном университете Колледж Харви-Мадд в южной Калифорнии.

Колледж Харви-Мадд не особо известен широкой публике, но он находится среди топ-университетов по заработным платам выпускников, а также проценту выпускников, защищающих впоследствие диссертации. Еще Харви-Мадд известен проектами в области роботехники, которые они делают вместе с NASA. Иными словами, это практики высшего калибра.

Дэвид Харрис и его коллега Сара Харрис (они не родственники, а просто однофамильцы) в 2008 году написали первый вариант учебника, в котором в лаконичной, технически корректной и имеющей смысл форме изложили материал, который обычно входил в несколько учебников: цифровая логика, языки описания аппаратуры Verilog и VHDL, архитектура и микроархитектура компьютера, а также использование готовых чипов. Студенты получили возможность, используя только один учебник, начать с нуля, дойти до конструирования собственного небольшого процессора, а потом сравнить его с промышленным микроконтроллером.

Идея перевести учебник Харрисов на русский язык возникла на Красной Площади в 2013 году. Ее предложил сотрудник МИФИ Иван Графский. Учебник настолько хорошо вписался в нужды российских университетов, что перевод его первой версии сделали "колхозом", состоящим из группы энтузиастов: преподавателей российских и украинских университетов, русских сотрудников компаний в Silicon Valley (AMD, Synopsys, Apple, NVidia ...) и российских компаний (НИИСИ, МЦСТ, Модуль ...).

Нынешний перевод использует и материалы предыдущих переводов.

Первая глава подразумевает, что читатель не знает вообще ничего, только читать, писать, и может быть закон Ома. В первой главе вводятся двоичные числа и уровни напряжения (какое напряжение соотвествует нулю, а какое единице). Потом учебник рассказывает про транзисторы и как строить из транзисторов логические элементы - как в частном случае (NAND), так и в общем - любую логическую функцию.

Во второй главе идет речь про комбинационные схемы, в третьей - про последовательностные, схемы, которые имеют состояние. Тут же вводятся конечные автоматы и возникают жизненные примеры и упражнения:

Одновременно с логикой вводится тайминг и его исправление, а также определение максимальной тактовой частоты, на которой может работать схема:

В четвертой главе вводятся языки описания аппаратуры Verilog и VHDL. В ней есть шпаргалка, как избежать несинтезируемого кода (multiple drivers) и гонок (race conditions), которые возникают при использовании блокирующих присваиваний к элементам состояния.

Пример ошибки с race condition: always @ (posedge clk) a = b; always @ (posedge clk) c = a; В таком коде результат зависит от того, какой из always-блоков симулятор эвалюирует первым. Такие ошибки также приводят к различным результатам симуляции схемы до и после синтеза. Ошибки такого рода часто делались в 1990-е, после чего была сформулирована методология, которая кратко выражена в шпаргалке ниже. Если вы видите методичку с подобным кодом - преподавателю нужно ее исправить. В компаниях race conditions иногда приводят к очень тяжело отлаживаемым ошибкам и необходимости перевыпустить чип на фабрике, что обходится в миллионы долларов - за такой косяк можно потерять работу.

В пятой главе описываются разного рода арифметические блоки и блоки памяти - кирпичики, из которых строится проектирование на уровне регистровых передач и микроархитектура. А также описывается устройство ячейки реконфигурируемой логики ПЛИС / FPGA:

Причем, что интересно, книга описывает ячейку ровно того Intel FPGA / Altera Cyclone IV, которые стоит на платах Omdazz, которые мы используем на Сколковской Школе Синтеза Цифровых Схем. Эту плату держит в руках девушка Наташа рядом с штаб-квартирой компании Cadence Desigtn Systems - одного из трех лидирующих производителей софтвера для разработчиков микросхем:

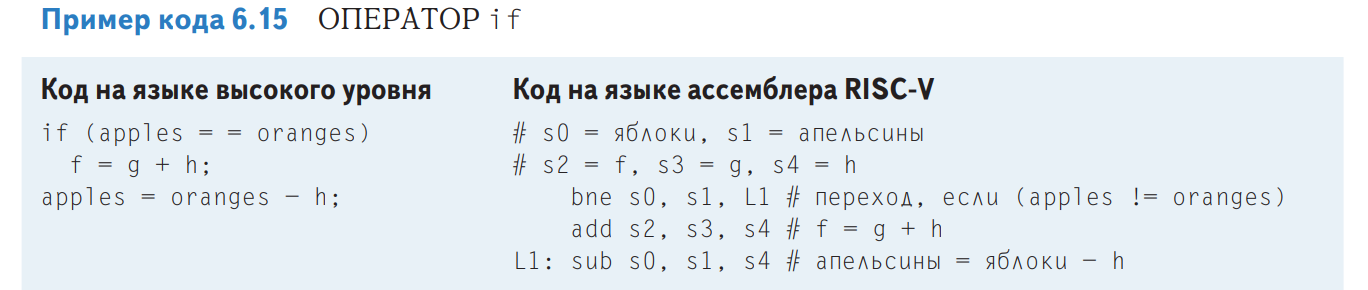

В шестой главе описывается архитектура, вид процессор с точки зрения программиста (не путать с микроархитектурой). В архитектуру входит система команд и видимые программисту регистры. В Харрис & Харрис также показывается как код на языке высокого уровня компилируется в ассемблер:

В седьмой главе описывается микроархитектура, вид процессор с точки зрения проектировщика железа (проектировщика железа). Сначала вводится процессор с однотактовой микроархитектурой, реализующей архитектуру RISC-V. Он описывается в виде микроархитектурных диаграм и приводится его код на Verilog и VHDL. Потом микроархитектура усложняется:

1. Для повышения максимальной тактовой частоты процессор делается многотактовым. К сожалению, это не повышает производительность процессора, так как инструкции начнут выполняться по несколько тактов.

2. Затем из стадий выполнения инструкций строится конвейер. Теперь каждая инструкция выполняется несколько тактов, но новая инструкция начинает выполнение, не дожидаясь окончания предыдущих. Тем самым у процессора растет производительность.

3. Помимо многотактовой и конвейерной версии в конце главы на пальцах описываются методы, которые применяются при проектировании высокопроизводительных процессоров: предсказание переходов, суперскаляр и многопоточность.

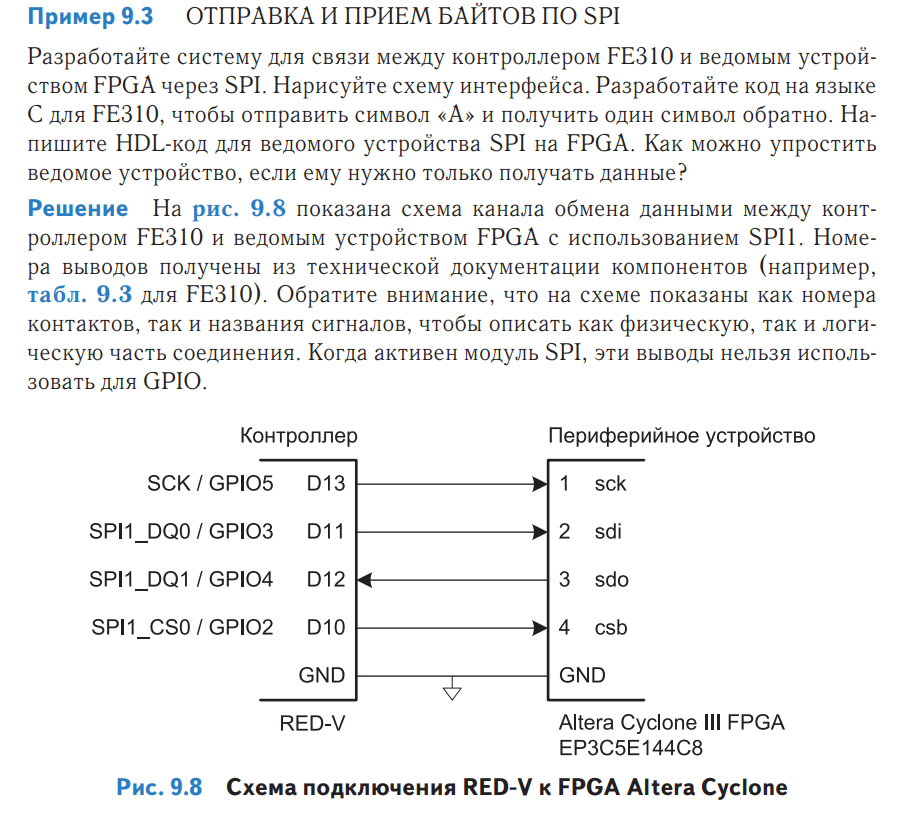

В восьмой главе описываются кэши и аппаратная реализация поддержки виртуальной памяти. Затем в девятой главе расписывается работа с готовым RISC-V процессором от SiFive и в частности есть такое занятное упражнение по сопряжению этого готового процессора с ведомым устройством на FPGA плате, схему которого разрабатывает студент:

.

Это очень полезное упражнение, потому что на Сколковскую Школу мы принесли несколько вот таких джойстиков с SPI интерфейсами, которые будем интегрировать с схемой на FPGA плате, частью которой является процессор schoolRISCV, сделанный на основе книги Харрисов, но schoolRISCV еще проще чем процессор в книге.

Вообще слайды из Харрисов будут использоваться на мероприятии в Сколково в субботу 25 декабря 2021, которое выглядит так:

Занятие на Сколковской Школе Синтеза Цифровых Схем 25 декабря будет называться "Микроархитектура конвейерного процессора и интеграция процессора с периферией".

Несмотря на такое сухое название, его бОльшая часть будет весьма творческим, причем творческим по взрослому: мы скомбинируем процессорное ядро schoolRISCV, добавим к нему графический сопроцесор со спрайтами, и будем менять одновременно процессор, видеопроцессор, связывающую логику (все это на языке описания аппаратуры Verilog) и писать программу игры на ассемблере RISC-V.

На такой платформе уже можно творить шедевры и мы ждем неожиданных идей (потом есть идея организовать соревнование по таким играм).

Записаться можно по емейлу info@chipexpo.ru

См. подробности и как проехать

В первый час занятия преподаватель МИЭТ Александр Силантьев покажет как можно развить микроархитектуру учебного однотактового процессора schoolRISCV

После этого Дмитрий Смехов, инженер-разработчик ПЛИС, компании IRQ, ИнСис и Inline Group, покажет пример совместного проектирования программ и аппаратуры, hardware-software co-design. Дмитрий покажет, как реализовать программное управление в графической игре, которую мы разбирали на занятии 11 декабря. Для этого Дмитрий заменит аппаратный конечный автомат на комбинацию из процессорного ядра schoolRISCV с работающей на нем программой.

Дмитрий будет выступать дистанционно, в Сколково ему будут помогать в офлайне Михаил Коробков, fpga-systems.ru, и Семен Москоленко, МИРЭА.

Теперь приготавливаемся к лонгриду.

Почему RISC-V?

Лицензируемые ядра RISC-процессоров изменили индустрию в конце 1990-х - начале 2000-х годов, когда ARM стал сердцем систем на кристалле внутри сотовых телефонов от Nokia и Ericsson, а MIPS стали использовать в телевизорах Sony, игровых приставках и даже роботах. К ARM и MIPS присоединились несколько конкурентов, в частности ARC и Tensilica, которые образовали так называемую индустрию полупроводниковой интеллектуальной собственности, semiconductor IP, общим размеров в несколько миллиардов долларов.

Помимо разработчиков центральных процессоров в эту индустрию вошли Imagination Technologies - компания, которая спроектировала графический процессор PowerVR для ранних Apple iPhone, затем разработчик процессора для обработки сигналов CEVA, и уже в наше время компании, которые выпускают ускорители вычислений нейросетей.

ARM и MIPS получали доход двумя способами:

Продажей лицензии на процессорные ядра - фактически на использование сотни тысяч строк на верилоге, написанных инженерами ARM и MIPS, внутри систем на кристалле заказчика. Примерами таких компаний стали Microchip, который лицензировал ядро MIPS M4K для микроконтроллеров PIC32, и ST Microelectronics, которые лицензировали ядра ARM Cortex M для линейки микроконтроллеров STM32.

Вторым способом получения дохода была продажа так называемой архитектурной лицензии, права на создание процессора собственной микроархитектуры. Инженеры компании-покупателя архитектурной лицензии создавали собственную микроархитектуру и могли писать код на верилоге сами, но их ядро делалось совместимым по архитектуре (системе команд) с ARM или MIPS. Последним примером такого лицензиата является компания Apple, которая создала свое ARM-совместимое ядро для системы на кристалле Apple M1.

Хотя разделение компаний на разработчиков IP-блоков и разработчиков систем на кристалле помогло развить индустрию в 1990-2000-е годы, не все в этой схеме было идеальным:

Во-первых, многие компании были недовольны условиями и политикой лицензирования как ядер, так и архитектуры. Особенно сильное негативное впечатление на индустрию произвел судебный процесс MIPS против Lexra в 1999 году, в результате которого пионер IP-лицензирования компания Lexra погибла из-за довольно мелкого нарушения патента на редко используемые инструкции невыравненного обмена с памятью. ( см. напр. )

Во-вторых, контроль архитектуры со стороны коммерческих компаний не нравился университетским исследователям. Хотя MIPS активно использовался в учебниках, а ARM давал гранты университетам, но ученым не нравилась перспектива получения писем от корпоративных юристов из-за какого-нибудь созданного ими экспериментального процессора.

Наконец, во всех RISC-архитектурах скопились разные черты, которые когда-то казались хорошими идеями, но стали тормозом прогресса при усложнении процессоров, повышении частоты, введении микроархитектуры с внеочередным выполнением команд, переменной длины инструкций и предсказателями перехода. У SPARС такой чертой были регистровые окна, у MIPS - слоты отложенного ветвления, у ARM - условное выполнение инструкций. Нужна была ревизия мира RISC-процессоров.

И этой ревизией стал RISC-V - архитектора, созданная в 2010 году группой того же Дэвида Паттерсона из Университета Калифорнии в Беркли, который написал два учебника и стоял у истоков архитектуры SPARC. Группа RISC-V не только синтезировала опыт процессорных компаний за предыдущие 30 лет, но и вступила в партнерства с Linux Foundation и многими крупными компаниями - Google, AMD, Western Digital.

Когда вы используете архитектуру RISC-V для проектирования своего процессора, вам не нужно платить за архитектурную лицензию. При этом сами вы можете получать за свой процессор деньги: продавать его как IP-блок, систему на кристалле, или производить на его основе чипы. Вы также можете решить сделать бесплатный процессор с открытым кодом на верилоге для исследователей - это тоже поощряется сообществом вокруг архитектуры RISC-V.

Сейчас RISC-V может сыграть большую роль в становлении российской электроники. Российские компании CloudBEAR (в которую инвестировал Байкал Электроникс) и Syntacore (приобретенная компанией Ядро) работают над процессорами собственной микроархитектуры, совместимыми по системе команд с архитектурой RISC-V. Это идеальная комбинация, которая позволяет разрабатывать свои процессоры и конкурировать по производительности, энергопотреблению и набору расширений с производителями на мировом рынке - одновременно сохраняя программную совместимость со всеми программами, которые создаются для экосистемы RISC-V во всем мире. К таким программам относятся компиляторы, операционные системы и прикладные программы по всему спектру - от программ для миниатюрных чипов для интернета вещей - до мобильных устройств, автомобильной электроники, десктопов и суперкомпьютеров.

Подводя итог

Предыдущие издания учебника Харрисов уже помогли исправить серьезный дисбаланс в преподавании цифровой электроники в России, который возник еще в 1990-е годы. Книга также стала отправной точкой для создания курса лабораторных работ на ПЛИС под эгидой ВШЭ МИЭМ, онлайн-курсов от РОСНАНО и семинаров на ChipEXPO в Сколково. Новое же издание учебника Харрисов выходит как раз тогда, когда в России разворачиваются амбицизные проекты по созданию высокопроизводительных процессорных ядер, которые совместимы с открытой международной архитектурой RISC-V, и при этом спроектированы в России.

Все причастные к переводу и изданию ожидают, что читатели этой книги станут топ-проектировщиками и бизнес-лидерами российcкой электронной промышленности, и помогут ей занять место в мире, которое соотвествует российским традициям достижений в математике, физике, атомных и космических технологиях.

Если вы дочитали до этого места - вот промокод на скидку 25% на покупку книги: Harris_bonus_2022