Since the New Year we had 7 Verilog meetups at HackerDojo. We discussed the modern way of designing digital circuits using hardware description languages, the exercises on FPGA boards and the topic of microarchitecture. For the last two sessions we went over the most basic CPU core that can be used as a baseline for further exercises.

Now, in order to make progress toward the goal of creating new educational materials, it is essential for the regular participants to solve all the homework exercises (see the details in the post below) in parallel with studying the recommended materials.

The next steps are:

1) We are going to do weekly Zoom calls on Sundays, starting March 24, 2024 at 11 am California time (summer time). The link. During this call we are going to discuss the SystemVerilog Homework and the individual projects.

2) Once we develop more materials, we are going to organize a Show-and-Tell session in Hacker Dojo, for a wider audience. During the session several participants from the core team will present demos on various FPGA boards and explain to the curious how FPGA and ASIC work.

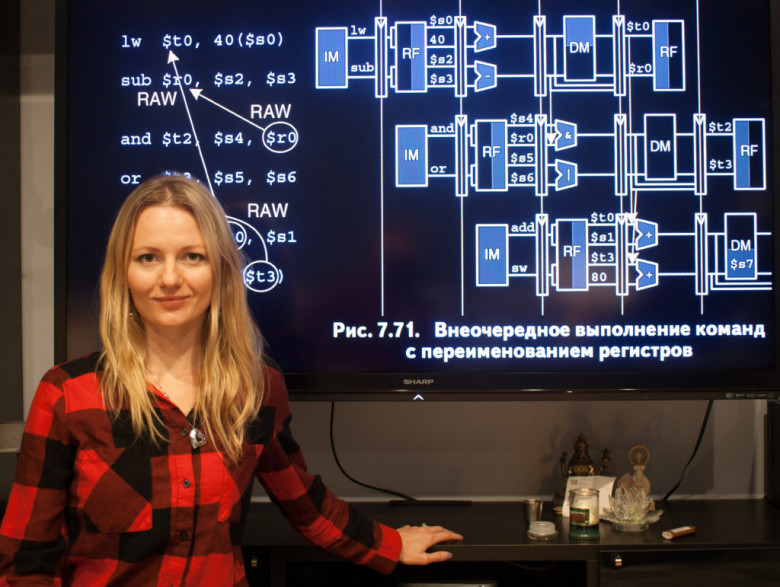

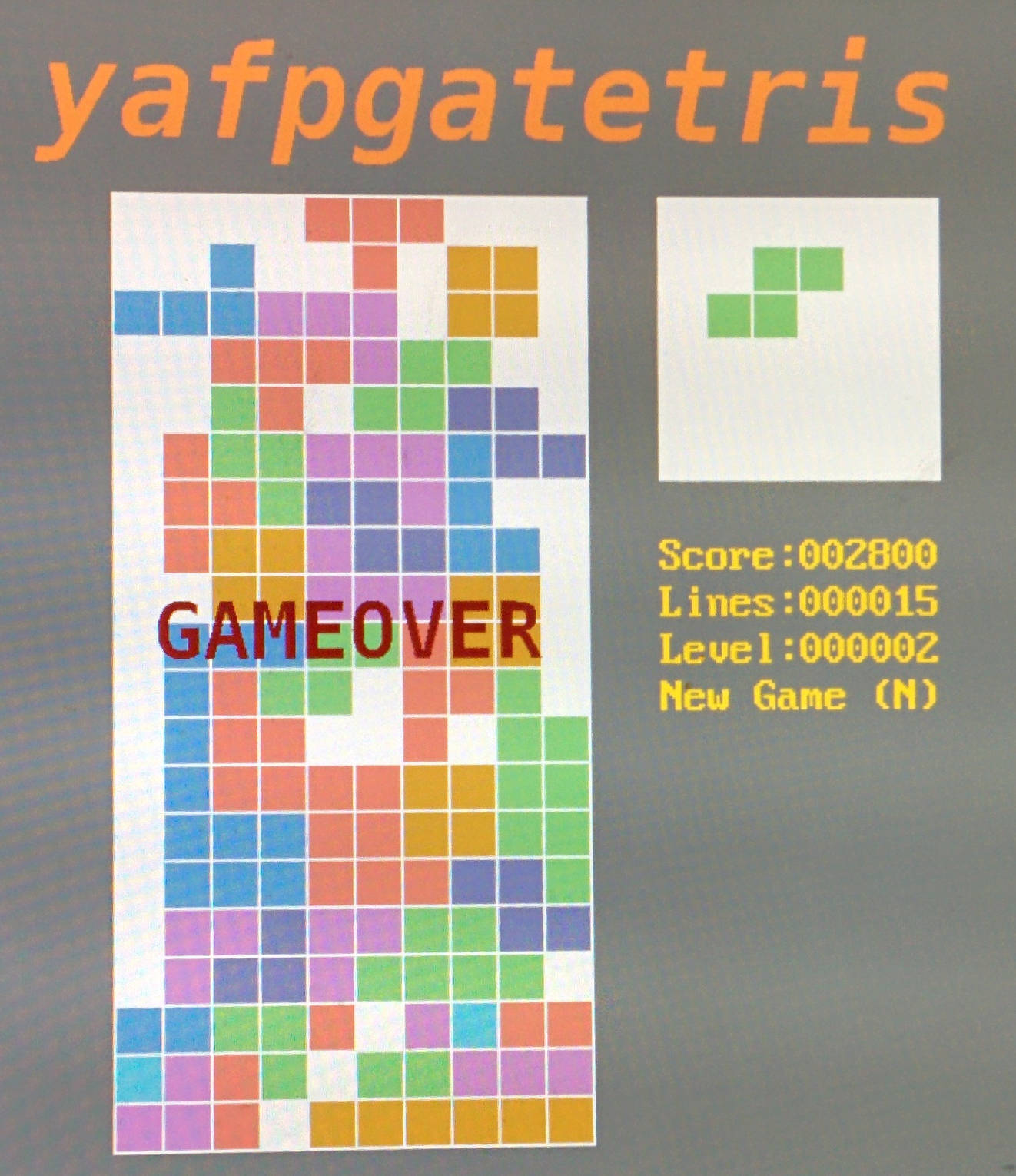

На этих долгих новогодних выходных я задался вопросом: насколько легко написать какую-то простенькую игрушку на FPGA с выводом на дисплей и управлением с клавиатуры. Так родилась еще одна реализация тетриса на

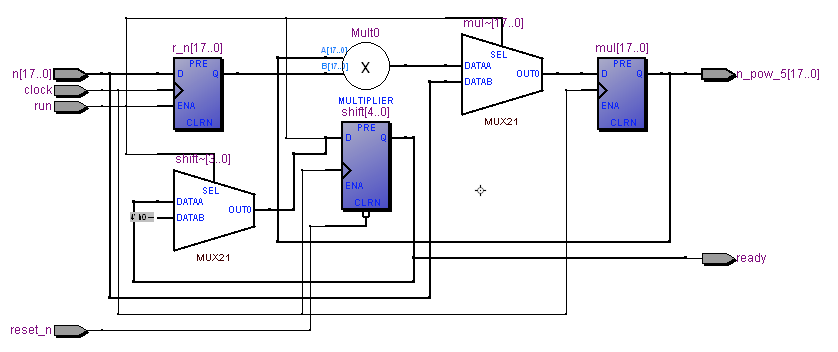

На этих долгих новогодних выходных я задался вопросом: насколько легко написать какую-то простенькую игрушку на FPGA с выводом на дисплей и управлением с клавиатуры. Так родилась еще одна реализация тетриса на  Каким образом студент или университетский исследователь может не просто спроектировать микросхему, но и получить ее в свои руки с фабрики? Ведь начальный взнос за фабричное производство микросхем для коммерческих целей как правило превышает миллион долларов? К счастью, такой путь существует за гораздо меньшие деньги — через организацию, которая называется Europractice. Я записал видео интервью с ее директором Carl Das.

Каким образом студент или университетский исследователь может не просто спроектировать микросхему, но и получить ее в свои руки с фабрики? Ведь начальный взнос за фабричное производство микросхем для коммерческих целей как правило превышает миллион долларов? К счастью, такой путь существует за гораздо меньшие деньги — через организацию, которая называется Europractice. Я записал видео интервью с ее директором Carl Das.