Ссылка на русскую версию / link to Russian version

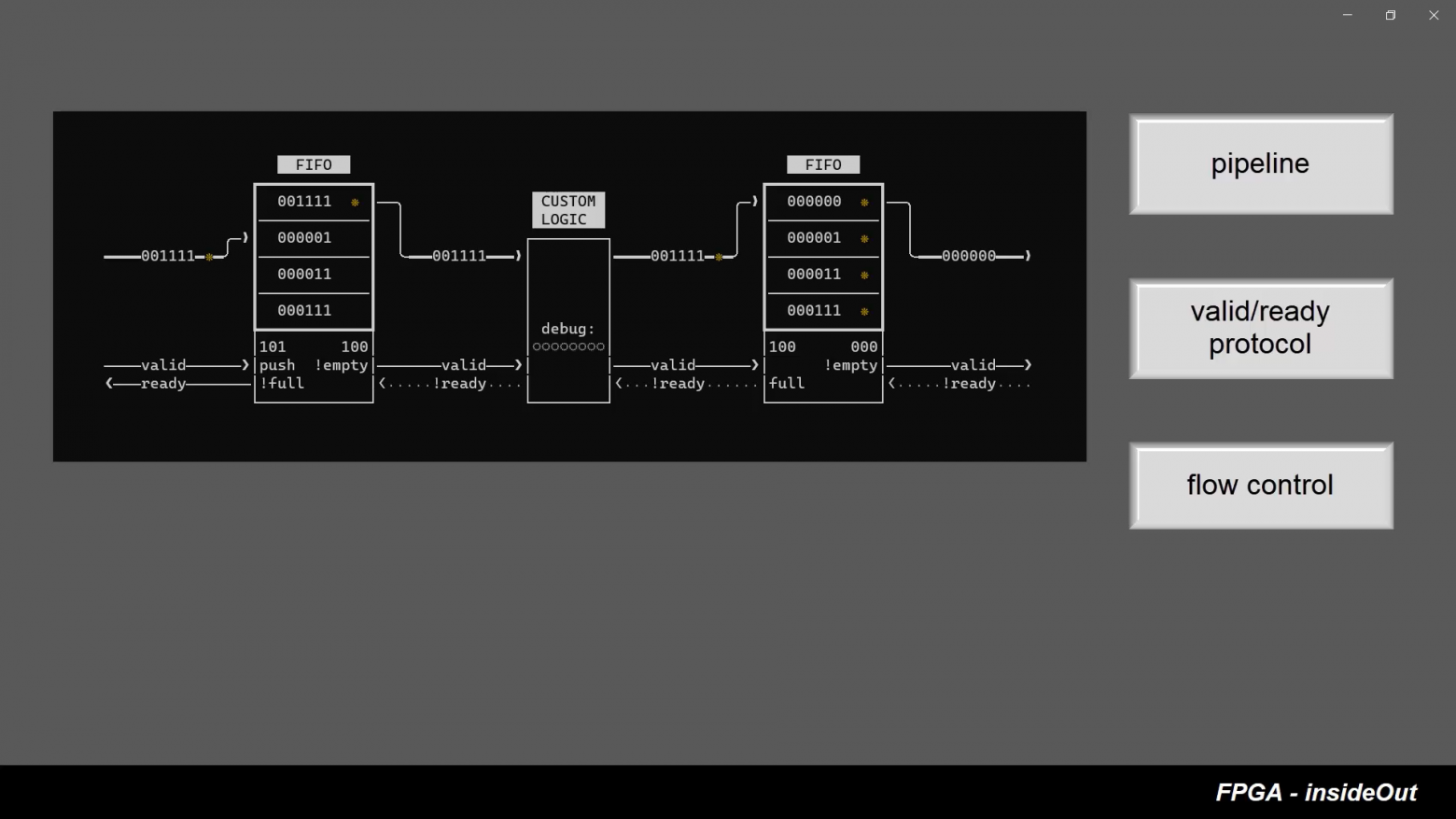

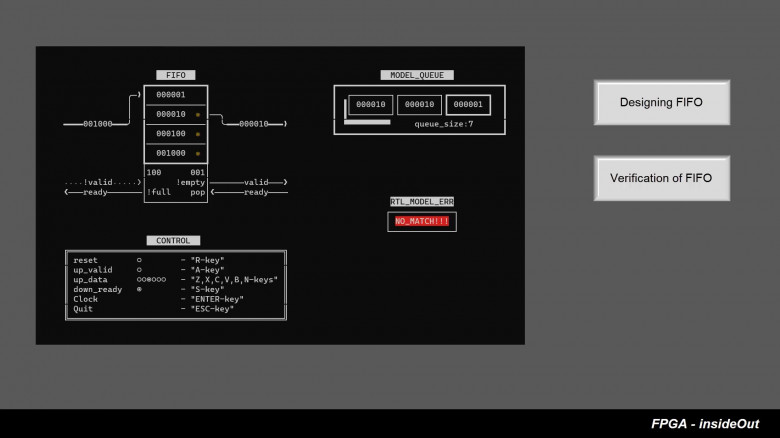

FIFO is a key concept in hardware design. Understanding of FIFO is necessary for understanding the valid/ready protocol, which in turn is necessary for organisation of flow-control within a design.

Unfortunately, there are very few books on this topic, and to be fair, microarchitectural concepts are quite difficult to master from books, since understanding of these concepts are coming with practice. In other words it is more about developing hardware intuition.

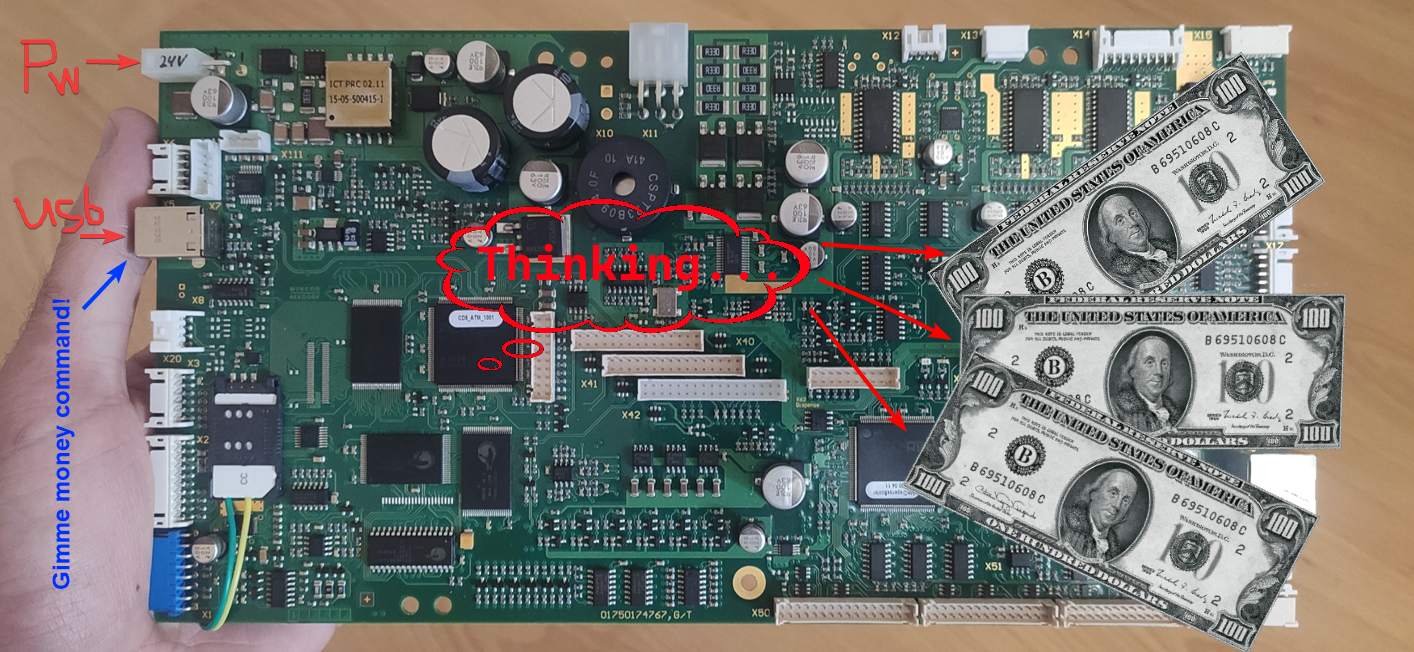

The idea of the HDL training tool is that it can help develop a hardware intuition, providing the opportunity to explore ready-made scenarios in a step-by-step interactive way. The tool also provides detailed visualization of a simulated scenario.

Since the tool is a front-end for the HDL simulator, the real, synthesized SystemVerilog is executed on the simulator itself, which can be viewed and even modified.

So, the video of exploring FIFO on the training tool is here: