1)

где a*b*...*c — это импликанта, состоящая из одной или более переменных. g+h+...+i — это возможно пустое множество импликант, состоящих из одной переменной. x*f — это импликанта из 2 переменных, наличие которой в минимальной форме не обязательно. Все переменные, кроме x, могут входить в формулу как в прямом, так и в инверсном виде, в зависимости от расстановки знаков соответствующих событий. Все переменные входят в формулу в качестве аргументов строго по одному разу.

Прежде чем идти дальше, подробнее рассмотрим такое явление как декомпозиция. Интересует прежде всего декомпозиция, которая сохраняет самосинхронность. При декомпозиции логической функции НЕ-И-ИЛИ в качестве нового элемента можно выделить:

а) одну или более импликант,

б) несколько сигналов (переменных) одной импликанты,

в) один входной инвертор.

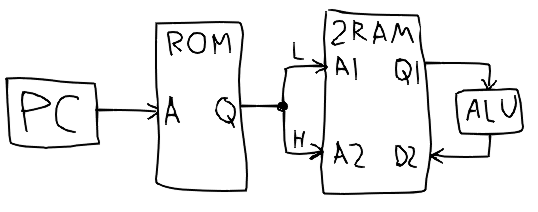

В статье описан очередной примитивный процессор и ассемблер для него.

В статье описан очередной примитивный процессор и ассемблер для него.