Как мы участвовали в InnovateFPGA 2018 и снова не победили

Программируемые логические интегральные схемы

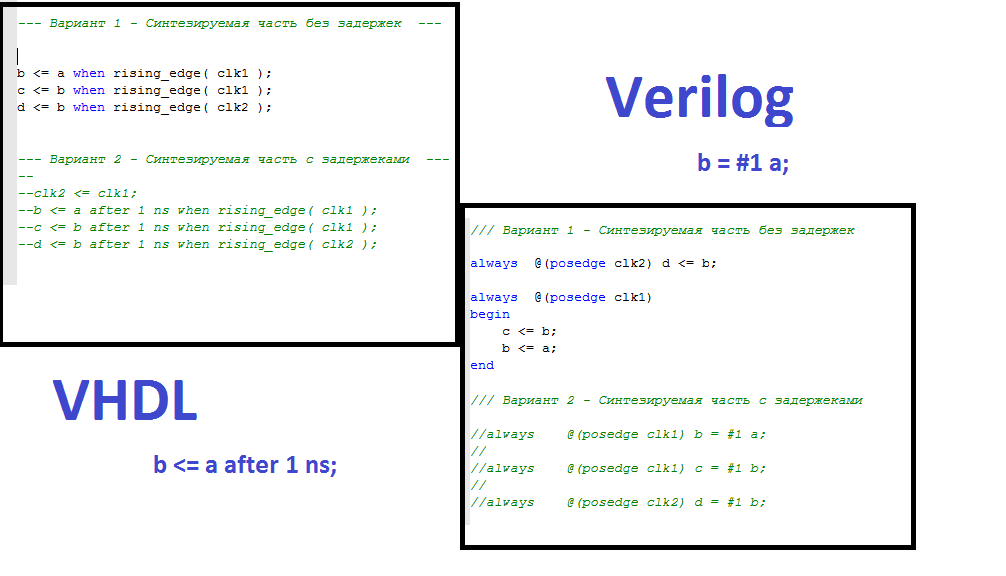

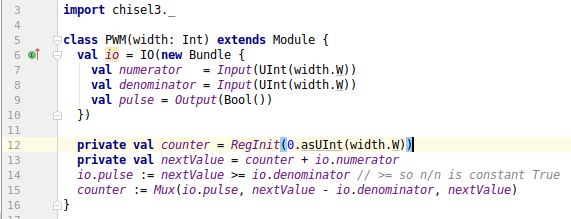

С развитием микроэлектроники, rtl дизайны становились все больше и больше. Реюзабилити кода на verilog доставляет массу неудобств, даже с использованием generate, макросов и фишек system verilog. Chisel же, дает возможность применить всю мощь объектного и функционального программирования к разработке rtl, что является достаточно долгожданным шагом, который может наполнить свежим воздухом легкие разработчиков ASIC и FPGA.

В этой статье будет дан краткий обзор основного функционала и рассмотрены некоторые юзкейсы использования, также поговорим о недостатках этого языка. В дальнейшем, если тема будет интересна, продолжим статью в более детальных туториалах.

Всем нам известна проблема курицы и яйца: работодатели не хотят брать на работу выпускников без опыта работы, но где же в таком случае выпускникам получить опыт работы? В микроэлектронике эта проблема стоит особо остро ввиду требуемого огромного количества специфического опыта. Наши ВУЗы с советских времен знамениты широчайшей теоретической подготовкой, которая должна помочь выпускнику в любой сложной ситуации в жизни. Однако, современная индустрия требует практического опыта. Добавим сюда еще отсутствие мотивации, приводящее к тому, что по специальности работает процентов 15% выпускников, и получим жесточайший кадровый голод в отрасли, которая очень требовательна к качеству кадров. А ведь если бы каждый студент мог "поморгать лампочкой" со своего собственного кристалла ситуация могла бы развиваться совсем иначе.

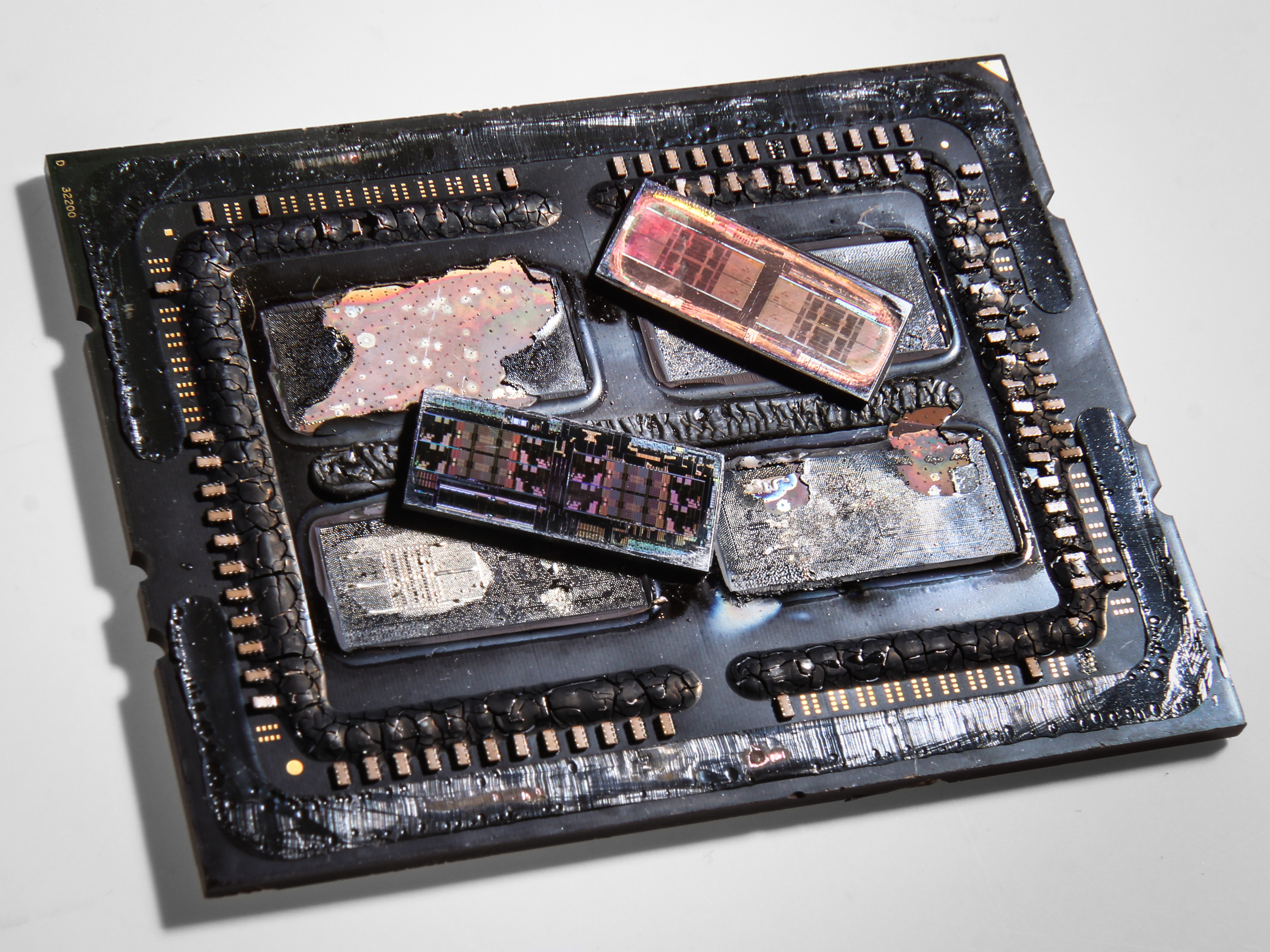

Рисунок 1. КДПВ

Что же мешает таким грандам подготовки кадров отечественной микроэлектроники, как, например, МИФИ и МИЭТ, поступать аналогично своим зарубежным коллегам (например, MIT или UZH), а именно — давать возможность студентами-дипломникам выпускать свои собственные кристаллы? Можно, конечно, предположить, что выпуск собственного кристалла занятие крайне долгое, сложное и дорогое, а потому для института — дорого, а для студента — непосильно. Однако, это не так. Давайте же взглянем на одну из доступных технологий на отечественном рынке микроэлектроники, знакомство с которой позволит студенту стать значительно более привлекательным в плане будущего трудоустройства, а предложение которой для студента — позволит университету значительно поднять свой рейтинг в глазах абитуриентов и работодателей.

Долгое время я мечтал научиться работать с FPGA, присматривался. Потом купил отладочную плату, написал пару hello world-ов и положил плату в ящик, поскольку было непонятно, что с ней делать. Потом пришла идея: а давайте напишем генератор композитного видеосигнала для древнего ЭЛТ-телевизора. Идея, конечно, забавная, но я же Verilog толком не знаю, а так его ещё и вспоминать придётся, да и не настолько этот генератор мне нужен… И вот недавно захотелось посмотреть в сторону RISC-V софт-процессоров. Нужно с чего-то начать, а код Rocket Chip (это одна из реализаций) написан на Chisel — это такой DSL для Scala. Тут я внезапно вспомнил, что два года профессионально разрабатываю на Scala и понял: время пришло...

Долгое время я мечтал научиться работать с FPGA, присматривался. Потом купил отладочную плату, написал пару hello world-ов и положил плату в ящик, поскольку было непонятно, что с ней делать. Потом пришла идея: а давайте напишем генератор композитного видеосигнала для древнего ЭЛТ-телевизора. Идея, конечно, забавная, но я же Verilog толком не знаю, а так его ещё и вспоминать придётся, да и не настолько этот генератор мне нужен… И вот недавно захотелось посмотреть в сторону RISC-V софт-процессоров. Нужно с чего-то начать, а код Rocket Chip (это одна из реализаций) написан на Chisel — это такой DSL для Scala. Тут я внезапно вспомнил, что два года профессионально разрабатываю на Scala и понял: время пришло...

Так что, если хотите почитать историю из жизни кусачек, цифрового мультиметра и осциллографа, который осознал себя, то добро пожаловать под кат.

module R0 #(parameter ADDR_WIDTH = 2, DATA_WIDTH = 4)

(

input clk, //тактовый сигнал

input [ADDR_WIDTH-1:0] adr, //адрес

input [DATA_WIDTH-1:0] data_in, //порт ввода данных

output [DATA_WIDTH-1:0] RAM_out //порт вывода данных

);

reg [DATA_WIDTH-1:0] mem [2**ADDR_WIDTH-1:0]; //объявляем массив mem

always @(posedge clk) //при поступлении тактового сигнала clk

mem [adr] <= data_in; //загружаем данные в ОЗУ из data_in

assign RAM_out = mem[adr]; //назначаем RAM_out портом вывода данных

endmodule

История про высокий порог входа, забеги по граблям и уверенность в завтрашем дне, а также про оптику, схемотехнику и немного про FPGA. На КДПВ — то, что получилось, работает и используется в production, а ниже — рассказ про процесс создания этого "чуда враждебной техники".

В одно хмурое зимнее утро декабря 2007 года маркетологи небольшой компании, занимающейся разработкой электроники, решили, что пора таки сделать свой OTDR.

Всем привет!

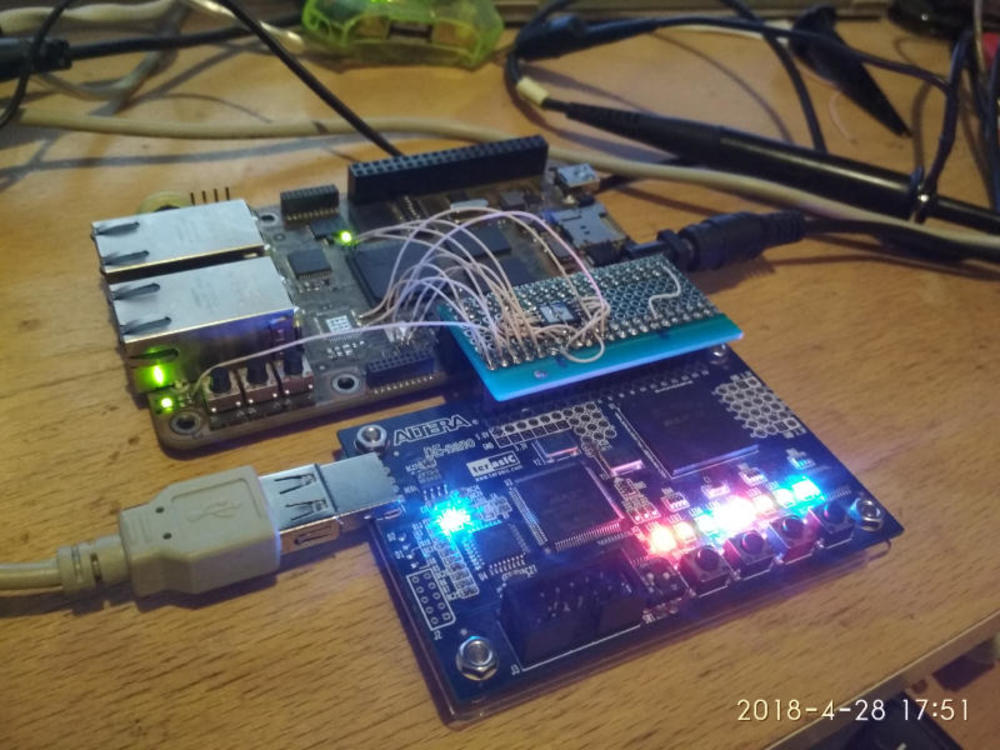

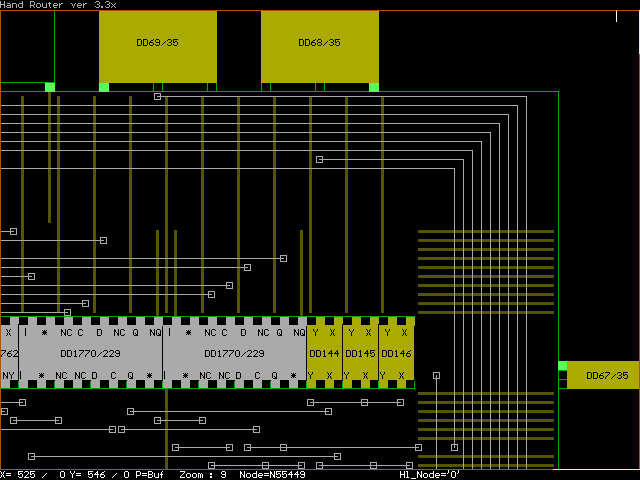

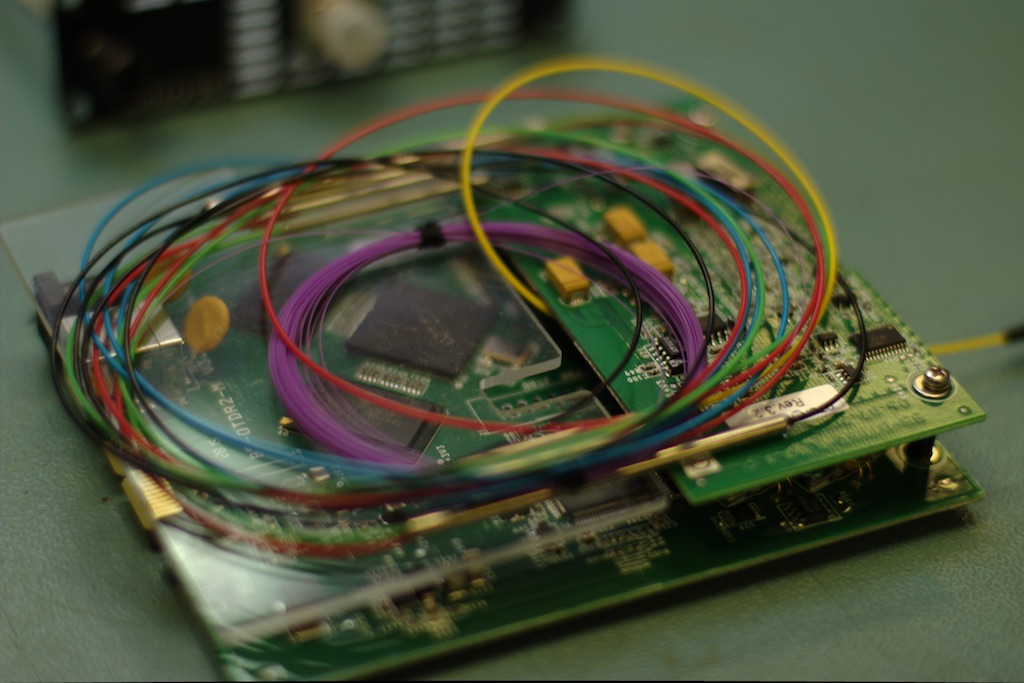

Недавно возникла задача — ускорить загрузку FPGA. От появления питания до рабочего состояния у нас есть не более 100 мс. Поскольку чип не самый новый (Altera Cyclone IV GX), просто подключить к нему быструю флешку типа EPCQ не получается. И мы решили задействовать режим FPP (Fast Passive Parallel), поставив снаружи CPLD Intel MAXV с FPL (Flash Parallel Loader). При старте CPLD загружает данные из флешки и формирует сигналы FPP на своих выходах.

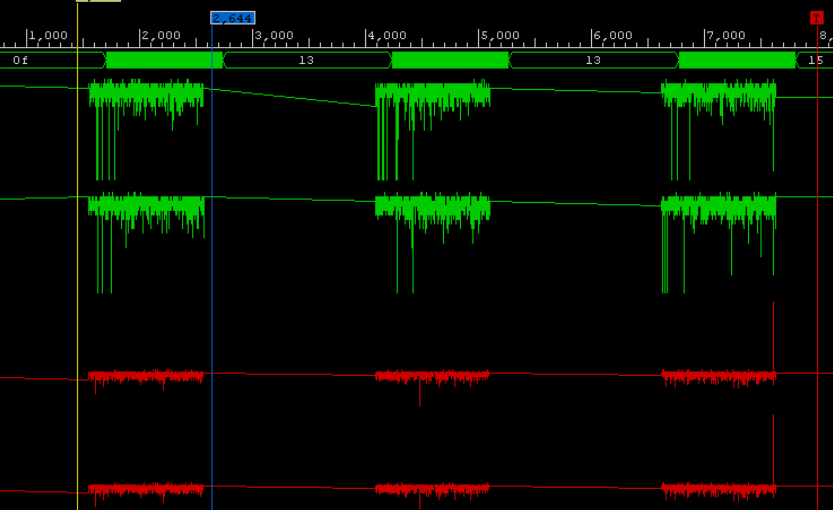

Однако, перед тем, как совершить задуманное, собрали DIY-макет из того, что было под рукой, и взялись поэкспериментировать "на кошках". К сожалению, из-за соплей на плате пришлось снизить рабочие частоты, но суть работы FPP от этого не изменилась, зато отладка упростилась. О том, что получилось, и о том, как конфигурируется FPGA, я и решил написать в этой статье. Кому интересно, добро пожаловать под кат.