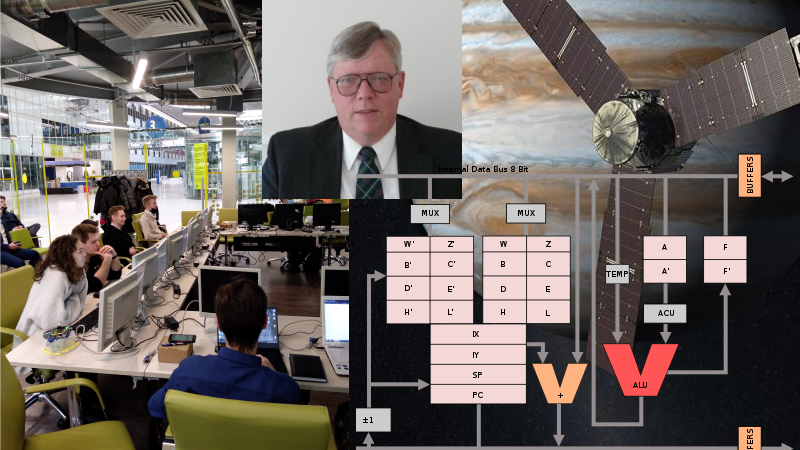

Мы с коллегами из МИЭТ, Ядро Микропроцессоры / Syntacore, МИРЭА, ВШЭ МИЭМ, МГУ, Иннополиса, ЧНТУ, Самарского университета, Siemens EDA и с поддержкой от Cadence Design Systems - проводим, начиная с 30 октября, курс на 13 суббот под названием "Сколковская Школа Синтеза Цифровых Схем". Это сильно расширенная версия трехдневной школы на ChipEXPO, которая прошла на ура в сентябре.

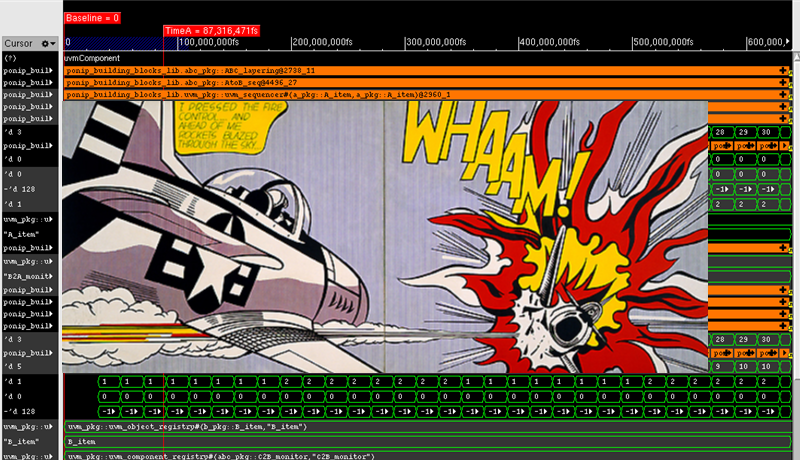

Суть школы - знакомство с маршрутом проектирования RTL2GDSII, который применяют проектировщики чипов в Apple, Intel итд, используя в качестве тренажера лабы на микросхемах реконфигурируемой логики FPGA, как это делают например в MIT в курсе 6.111. Помимо лаб на FPGA в курсе будет туториал по ASIC flow используя софтвер от Cadence, после которого, если мы договоримся, будет экскурсия на фабрику микросхем в Зеленограде.

Число регистраций снова в несколько раз превысило число посадочных мест в Сколково, поэтому большая часть участников вероятно будет проходить школу удаленно, как и зарегистрировавшиеся вне Москвы, в том числе в Белоруссии, Украине, Азербайджане, Казахстане итд - среди зарегистрировашихся есть даже русские живущие в Германии.