Трансляция 22-го предновогоднего выпуска подкаста linkmeup оказалась взрывной, а последующая публикация

10-й части СДСМ закрепила успех. Был аншлаг и по количеству слушателей и по количеству новых участников

группы вк и по качеству комментариев в джаббере.

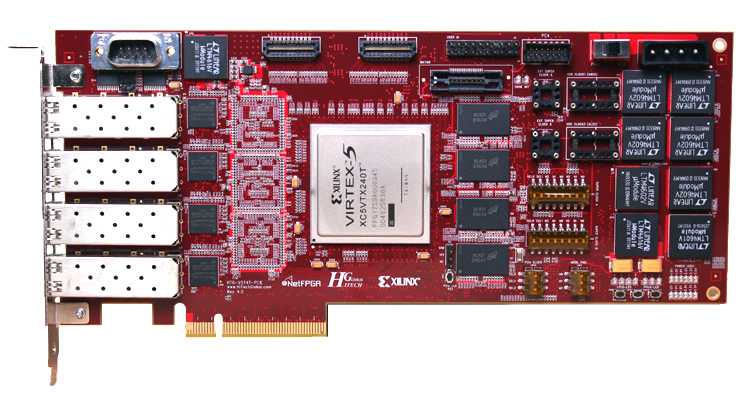

И тому есть причина — тема выпуска — Измерение качества каналов и разработка ПО для чипов FPGA для обработки 100 Гб/с без потерь.

В гостях у нас сотрудники

НТЦ Метротек:

Павел Курочкин (директор по разработке ПО) и

Иван Шевчук (инженер-разработчик FPGA).

В подкасте мы обсуждаем:

- Линейки оборудования Метротек — измерительное оборудование, коммутаторы, специальные разработки.

- Методология измерения каналов связи и в частности Ethernet: двусторонние и односторонние задержки, джиттер, пропускная способность, BERT.

- Стандарты измерения: RFC2544 и Y.1564, OAM, TWAMP/OWAMP.

- Чипы FPGA. Для чего используются, чем отличаются от ASIC.

- Разработка FPGA для обработки трафика Ethernet на скорости 100 Гб/с. Проблемы, решения, принципиальные схемы.

Кроме того, в 22-м выпуске мы начинаем рубрику «История связи». Вести её будет

Дмитрий Булыгин. В первой части рассказ об открытии электричества и самых первых прототипах телеграфа.

Хранилище подкастов rpod.ru почил в бозе вместе со своим RSS, поэтому старая лента iTunes больше неактуальна.

Вы можете подписаться на продолжение и добавить в свой плеер

RSS с

podfm.ru.

Скачать все выпуски подкаста вы можете с помощью

BT Sync (код: BYENRHD5UNKD5ZDIYFSB63WG2PEY2GIUN) или с

яндекс-диска.

Хронометраж:

0:00:00 — 0:27:47: Вступление и новости.

0:27:47 — 0:40:40: Рубрика «История связи» от Дмитрия Булыгина.

0:40:40 — 0:50:56: НТЦ Метротек. История, разработки. Павел Курочкин.

0:50:56 — 1:54:20: Измерение параметров каналов связи. Павел Курочкин.

1:54:20 — 2:11:30: Линейки оборудования Метротек и положение на рынке. Павел Курочкин.

2:11:30 — 3:02:16: Разработка ПО для чипов FPGA. Иван Шевчук.

Всем привет! Одно из видений

Всем привет! Одно из видений