В субботу 13 ноября с 12.00 по Москве пройдет следующая сессия Сколковской школы синтеза цифровых схем, в режиме онлайн. По плану на ней должны были быть упражнения на FPGA плате с последовательностной логикой. Однако мы решили изменить план и переставить на эту дату занятие по архитектуре RISC-V. Это занятие было изначально запланировано 11 декабря. Занятие по последовательностной логике будет передвинуто на 20 ноября. Почему мы решили так сделать - см. обьяснение через три абзаца.

Занятие по RISC-V проведет проектировщик российского микропроцессорного ядра Никита Поляков из компании Syntacore. В Syntacore Никита перешел из компании МЦСТ где он проектировал процессор Эльбрус.

Занятие будет состоять из лекции с одновременными упражнениями на симуляторе RARS. RARS моделирует процессор на уровне архитектуры (системы команд, видимых программисту), в отличие от симулятора Icarus Verilog, который мы обсуждали в предыдущей заметке и который моделирует на уровне регистровых передач / микроархитектуры (внутреннего устройства схемы процессора). Разработчику процессора нужно уметь пользоваться симуляторами обеих типов.

У RARS есть три кнопки - запустить, ассемблировать и выполнить шаг. В конце занятия вы будете уметь программировать на ассемблере, даже если раньше этого никогда не делали. В этой заметке мы расскажем, как установить симулятор и запустить простую программу на ассемблере. Потом в следующей заметке я напишу, что такого особенного есть в архитектуре RISC-V и почему мы выбрали для семинара именно ее, а не ARM, x86/64, MIPS, AVR, SPARC, Эльбрус, Z80, 6502, PDP-11 или еще что-нибудь другое.

Но прежде всего:

Почему мы решили изменить расписание?

Изначально:

Мы планировали довольно камерное действо в комнате в сколковском технопарке на 25 человек, для чего мы купили 25 плат и 25 комплектов периферийных устройств.

Одновременно мы планировали логичную последовательность: введение в простейшие схемы - схемы посложнее - процессор - взрослый маршрут для ASIC - схемы на уровне собеседования в компанию.

Что произошло:

Мы получили 310 заявок.

Несмотря на то,что в дополнение к 25 платам мы заказали еще больше 100 плат, эти платы еще идут из Китая и большинство из них не прибудут к 13 ноября, но зато скорее всего прибудут к 20 ноября.

При этом у нас на руках около 80 емейлов от участников с сертификатами роснановского курса и более 10 решений первой серии упражнений на верилоге. Мы вышлем и раздадим в Москве платы всем, у кого нет платы и кто выполнил эти пререквизиты (роснано или две серии упражнений на верилоге), но мы не успеем это сделать до 13 ноября.

Перенос занятия на архитектуре RISC-V на 13 ноября - это решение, потому что:

Это занятие делается целиком на симуляторе RARS и не требует FPGA платы.

Это занятие также не требует знания верилога - все происходит на уровне системы команд, ассемблера, архитектуры - того, как процессор выглядит с точки зрения программиста.

Потом в декабре у нас будет вторая часть про процессоры - микроархитектура, как процессор устроен изнутри. Она уже потребует синтеза процессора на FPGA плате.

Конечно у этого решения есть недостатки:

Между занятием по архитектуре и занятием по микроархитектуре пройдет 4 недели, а знание второго необходимо для знания первого. Ну мы попробуем во время второго занятия знания по первому слегка освежить. Кроме этого, понять идею ассемблера - это как научиться кататься на велосипеде - раз выучились, можете повторить всю жизнь. Особенно такого простого как RISC-V.

Другой недостаток - этим занятием мы прерываем последовательнсть про Verilog. Для компенсации этого недостатка в первый час занятия 13 ноября будет выступать не Никита Поляков, а Александр Силантьев из МИЭТ, который проведет разбор задачек, которые мы предложили вашему вниманию неделю назад.

У вас может сразу возникнуть вопрос: а где этот RISC-V используется? Вообще на архитектуре RISC-V можно строить процессорные ядра разных классов, от микроконтроллеров до десктопов (что сейчас начинает разрабатывать российская компания Syntacore) и до суперкомпьютера, но больше всего RISC-V сейчас используется во встроенных приложениях. У меня нет под рукой хорошей фотки встроенного приложения с RISC-V, но вот фотка с встроенным приложением на основе архитектуры MIPS, из которой в RISC-V пришли многие идеи (также в нее пришли идеи из RISC-I / II / SPARC, ARM и других архитектур, от суперкомпьютеров до DSP). Слева от девушки Ирины - японский робот-собачка с вариантом встроенного микропроцессора MIPS R4000:

RARS написан на Java. Если у вас нет Java runtine, вот инструкция как его поставить для Linux, Windows и MacOS. Особенно просто для Linux:

sudo apt-get --yes install default-jre

Сам RARS - это просто один jar файл, который скачивается здесь. Вы можете также использовать копию RARS из текущего пакета упражнений для школы:

ChipEXPO 2021 Digital Design School package v2.3

Ссылка через bit.ly - https://bit.ly/chipexpo2021dds23

Прямая ссылка

Внутри пакета RARS находится в директории ce2020labs/day_3/arch/risc_v_lab/. Он называется rars.jar. Если он не запускается в проводнике (например файл ассоциирован с архиватором, а не джавой), запустите его в командное строке:

java -jar rars.jar

Или кликните в проводнике под Windows на пакетный файл ce2020labs\day_3\arch\risc_v_lab\rars.bat . Или под Linux на ce2020labs/day_3/arch/risc_v_lab/rars.sh .

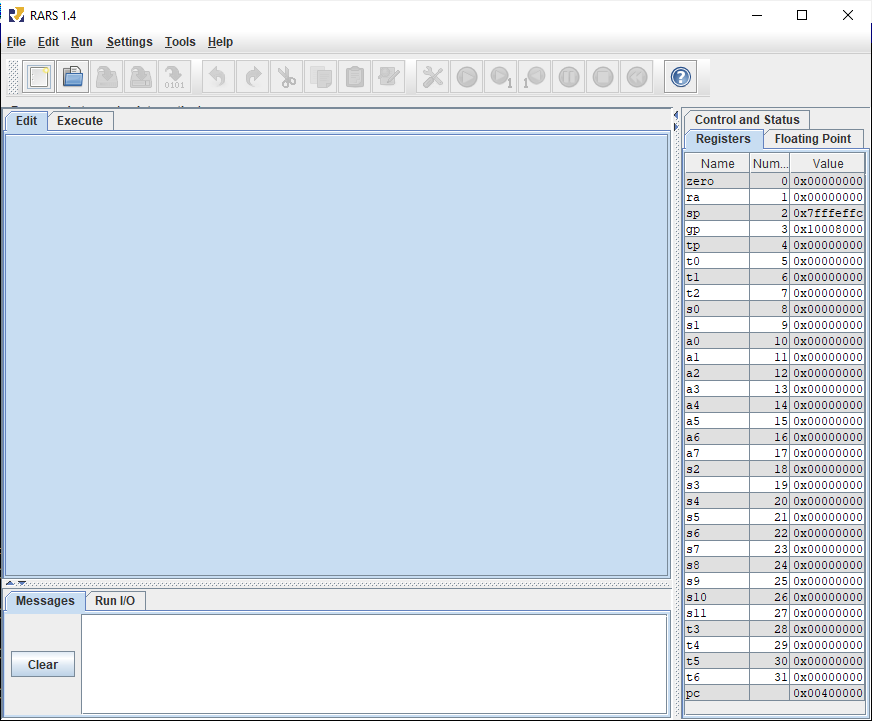

После запуска вы увидите вот такое окно:

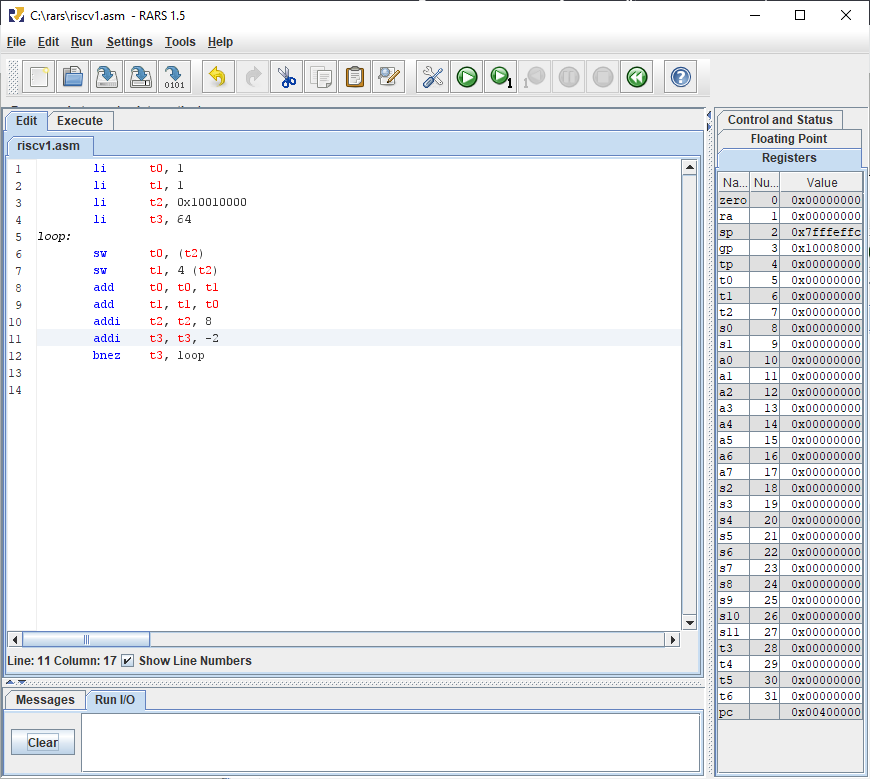

Нажмите Ctrl+N или кликните мышкой на File | New и введите какую-нибудь программу на ассемблере RISC-V, например вот такую программку для расписывания памяти в цикле числами Фибоначчи. Вас научит писать такие программки Никита Поляков на семинаре:

li t0, 1 li t1, 1 li t2, 0x10010000 li t3, 64 loop: sw t0, (t2) sw t1, 4 (t2) add t0, t0, t1 add t1, t1, t0 addi t2, t2, 8 addi t3, t3, -2 bnez t3, loop

Нажмите кнопку F3 или Run | Assembler. Программа превратится в машинный код, инструкции процессора RISC-V:

Теперь нажмите F7 или Run | Step. Программа пройдет один шаг, одну инструкцию, и загрузит константу 1 в регистр t0 / регистр 5 (выделено зеленым). После этого она станет на следующую инструкцию (выделено желтым):

Вы можете сделать еще несколько шагов и посмотреть, как программа начинает записывать числа в память (внизу, выделено синим):

Теперь нажмите на F5 или Run | Go. Программа выполнится до конца - запишет 64 числа Фибоначчи в память. В реальном процессоре программа будет продолжаться и дальше (скакать по инструкциям в памяти после нашего кода), но RARS замечает конец и останавливается:

Вот и все. Напишите собственную программу сложения 2 + 2, посетите семинар в субботу и можете считать себя ассемблерным программистом, причем на самой хайповой архитектуре современности. Никита Поляков, помимо простых арифметических операций, циклов и ветвлений, еще собирается рассказать о механизме вызова функций через стек (напишите на ассемблере Хайнойские башни если вы это поймете), а также как различные конструкции языка Си транслируются в ассемблер.

А на одном из следующих занятий другой проектировщик российского RISC-V ядра компании Syntacore, Станислав Жельнио, покажет вам как спроектировать собственный вариант микропроцессора подмножества архитектуры RISC-V и реализовать его в железе на плате реконфигурируемой логики ПЛИС / FPGA.

Если вы еще ничего не слышали о Сколковской школе синтеза цифровых схем, вот вебсайт и регистрация. Там же ссылка на первое занятие по верилогу, если вы его пропустили.