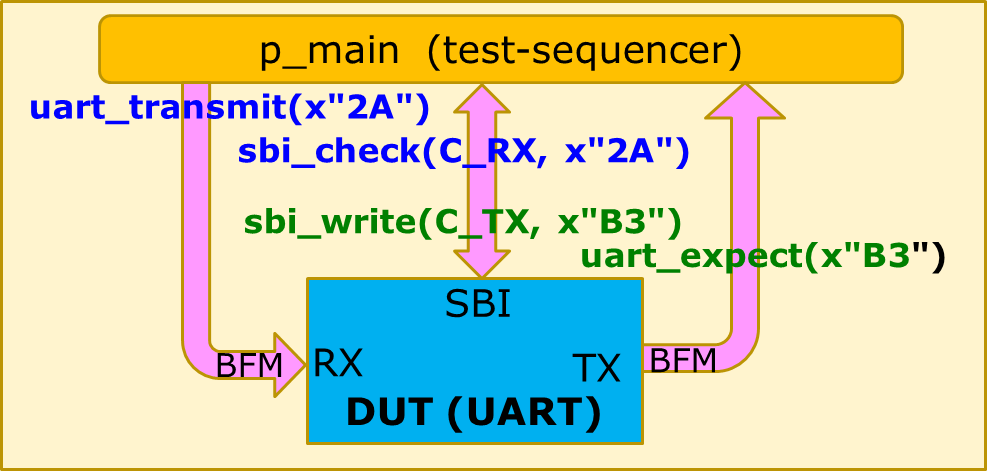

Верификация один из самых ответственных и трудоёмких этапов разработки на ПЛИС. Однако, затрачиваемые на неё усилия могут быть значительно ниже при правильно разработанном тестовом окружении testbench. UVVM — Universal VHDL Verification Methodology — один из инструментов, помогающих построить корректное тестовое окружение на языке VHDL. Порог освоения UVVM достаточно прост даже для начинающих разработчиков FPGA.

31.03.2020

|

На этом тренинге вы узнаете, что такое Hyper-Pipelining, чем он отличается от обычной конвейерной обработки и как внедрить Hyper-Pipelining в свой проект с помощью инструмента анализа Fast Forward, входящего в состав программного обеспечения Intel Quartus Prime Pro.

30.03.2020

|

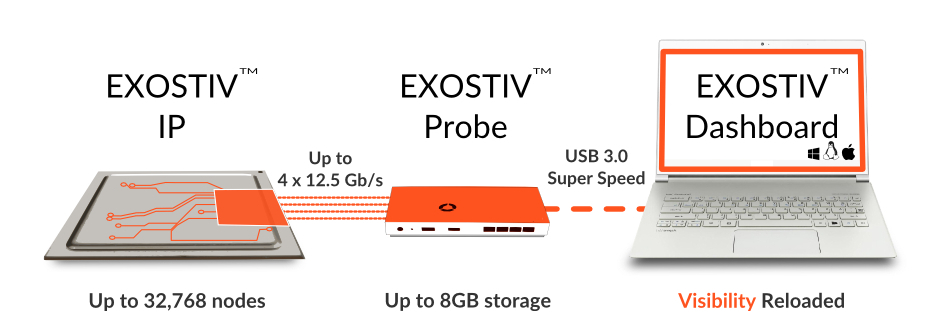

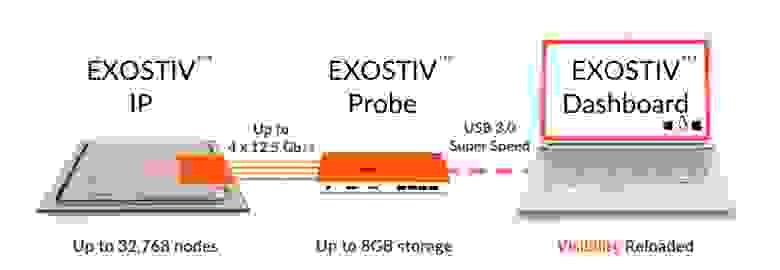

Компания Exostiv приглашает на вебинар, посвящённый продвинутым решениям отладки проектов для ПЛИС и ASIC.

Решения компании Exostiv направлены на мониторинг состояния сигналов внутри ПЛИС по аналогии с SignalTap/ILA (подробнее рассказывалось здесь). В рамках вебинара будут продемонстрированы особенности и преимущества использования отладочных комплектов Exostiv по сравнению с классическими JTAG-отладчиками.

30.03.2020

|

На портале сообщества Pynq появилась сообщение о том, что теперь образ и функционал Pynq доступен для карт ускорителей Xilinx Alveo. Теперь применять наработки Pynq можно не только с платформами на базе Zynq и Zynq UltraScale+, но и с платформами на базе x86+Alveo.

29.03.2020

|

Рады сообщить, что вышло новое обновление Sigasi Studio 4.7. Разработчики Sigasi постоянно работают над улучшением IDE, добавляя в каждой версии всё более широкую поддержку языков VHDL, Verilog, SystemVerilog.

29.03.2020

|

Компания proFPGA сообщила о запуске новой платформы для прототипирования и верификации, построенной на базе Xilinx Virtex Ultrascale+ XCVU37P с поддержкой высокоскоростной памяти HBM.

28.03.2020

|

Компании Analog Devices и Arrow Electronics совместно с компанией Trenz Electronic GmbH представили сразу несколько бюджетных платформ для сбора и анализа данных, предназначенных для ускорения разработок изделий измерительной техники.

28.03.2020

|

Selaheddin Hetalani — Инженер по применению в компании OneSpin Solutions рассказывает о проблемах разработок на FPGA и акцентирует внимание на том, как время разработки и работы над проектом может быть уменьшено за счёт применения методов формальной верификации.

28.03.2020

|

Компания Bitware объявила о проведении вебинара по тематике применения технологии FPGA/ПЛИС для решения серверных задач.

28.03.2020

|

Согласно январской записи в блоге VMware, был расширен набор поддерживаемых аппаратных ускорителей в гипервизоре vSphere, включена поддержка карт программируемых ускорителей Intel с FPGA Intel Arria 10 GX (Intel PAC с Intel Arria 10 GX FPGA)

26.03.2020

|

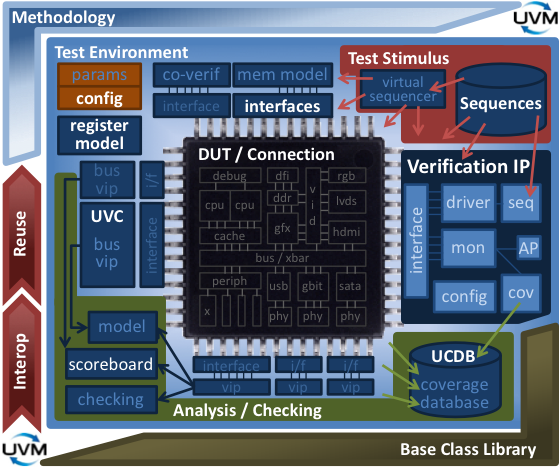

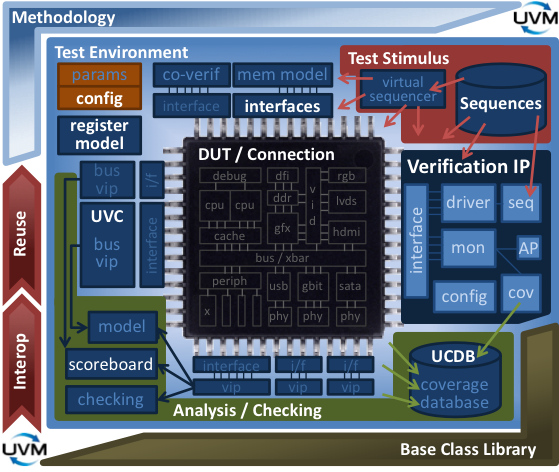

Ведущий вебинара, Крис Спир, представляет руководство по работе с UVM (универсальной методологии верификации). Он даст рекомендации по разработке тестовых транзакций и классов компонентов, которые будут просты в отладке и повторно применяемы. Отдельно будут рассмотрены правила разработки кода SystemVerilog для исключения распространенных ошибок.

25.03.2020

|

Компания Xilinx анонсировала выход нового отладочного комплекта ZCU216, выполненного на базе системы-на-кристалле RFSoC, сочетающего в себе многоядерный процессор АРМ + поле программируемой логики FPGA/ПЛИС + высокоскоростные АЦП и ЦАП.

25.03.2020

|

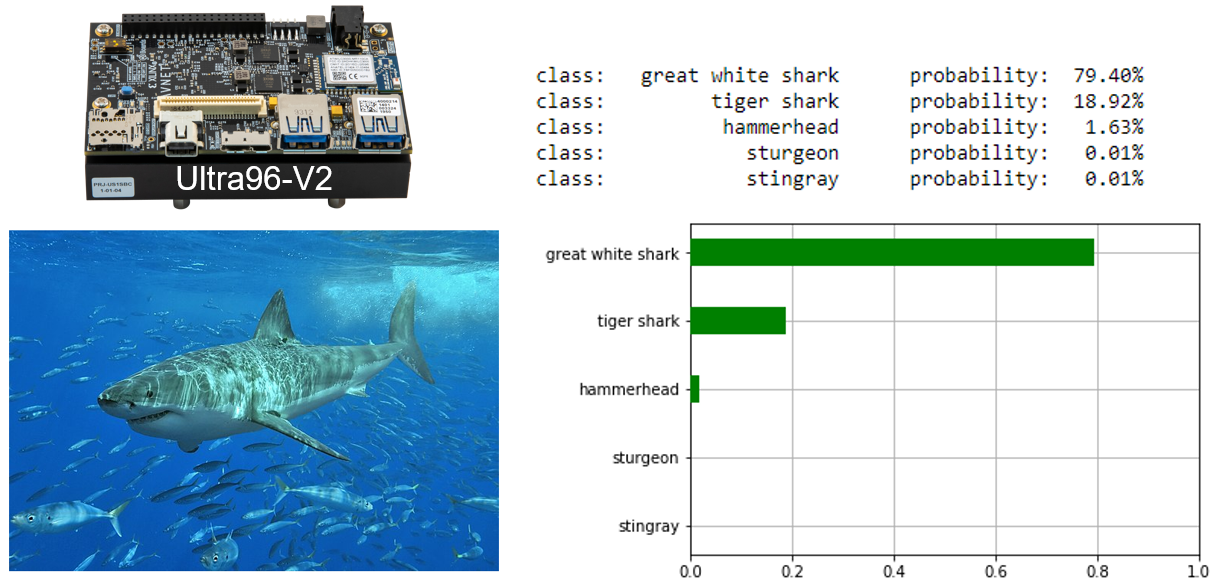

На портале element14 появилась новость о проведении вебинара. посвященного использованию специальных «накладок» для проекта pynq (pynq overlays) для работы с нейронными сетями на отладочном комплекте Ultra96-v2.

25.03.2020

|

В LinkedIn появилась небольшая заметка от одного из ведущих руководителей направления высокоуровнего синтеза в компании Xilinx — Frederic Rivoallon, рассказывающая нам о «мягкой» стороне проектирования на FPGA.

25.03.2020

|

Разместил KeisN13

Недавно компания Xilinx анонсировала новую серию своей адаптивной вычислительной платформы ACAP под названием Versal Premium Series. Анонс платформы также планировался в рамках выставки OFC2020.

|

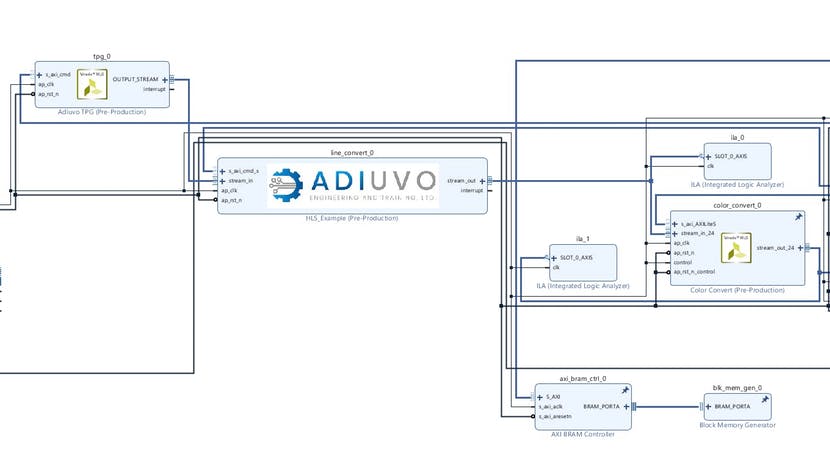

На портале hackster.io появилось новое руководство от Adam Taylor, в котором он описывает маршрут проектирования пользовательского IP ядра для видеообработки с помощью Vivado HLS.

19.03.2020

|

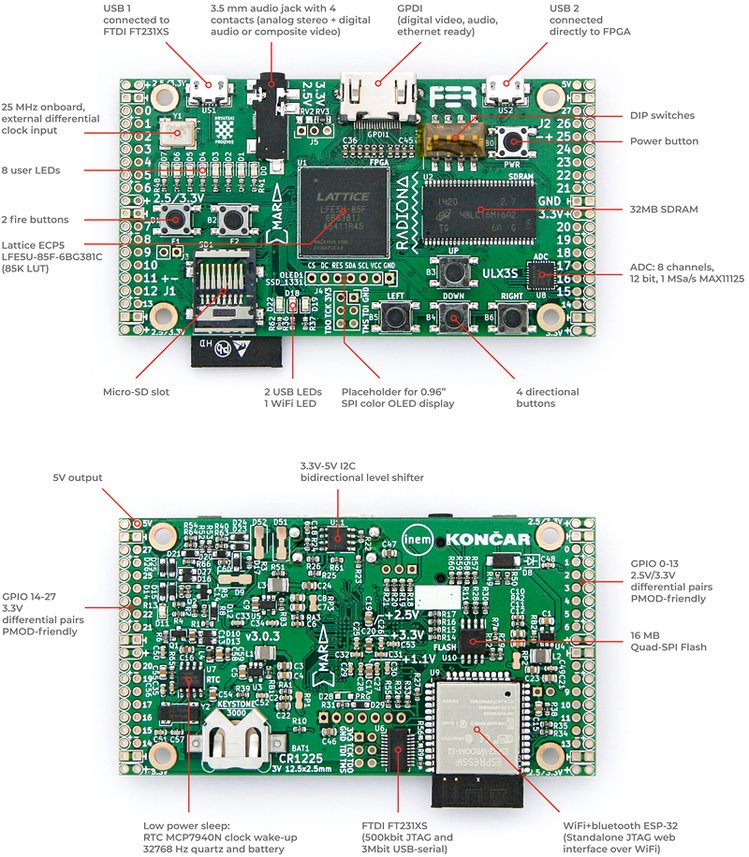

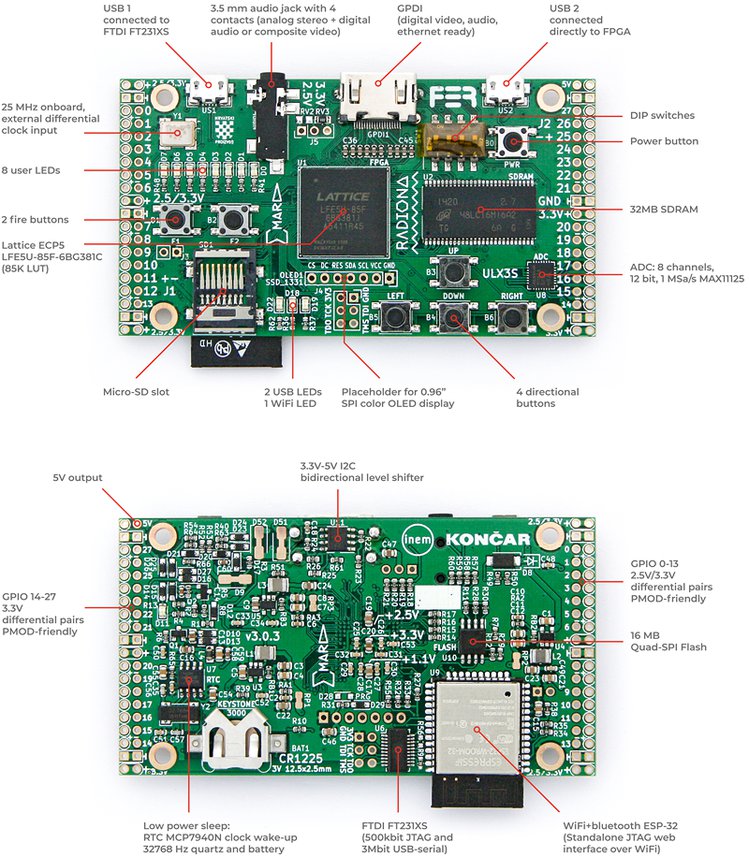

На портале Croudsupply появилась информация о новом отладочном комплекте ULX3S с открытыми исходниками, выполненного на базе ПЛИС компании Lattice. Проект уже собрал, или даже пересобрал 247% Funded!, необходимую сумму.

19.03.2020

|

Компания SICK AG представит свой новый продукт nanoScan3 — ультракомпактный лазерный сканер, имеющий соответствующий сертификат безопасности ISO 13849 PLd, Cat 3, созданный на базе СнК Zynq Z-7020. Также на вебинаре будет рассмотрен вопрос о потенциальных возможностях внедрения гетерогенных многопроцессорных систем для будущих архитектур.

18.03.2020

|

Проекты должны максимально полностью проверены на модели. Библиотека OSVVM — Open Source VHDL Verification Methodology предоставляет такую возможность и даёт разработчикам структурированный подход к верификации проектов.

17.03.2020

|

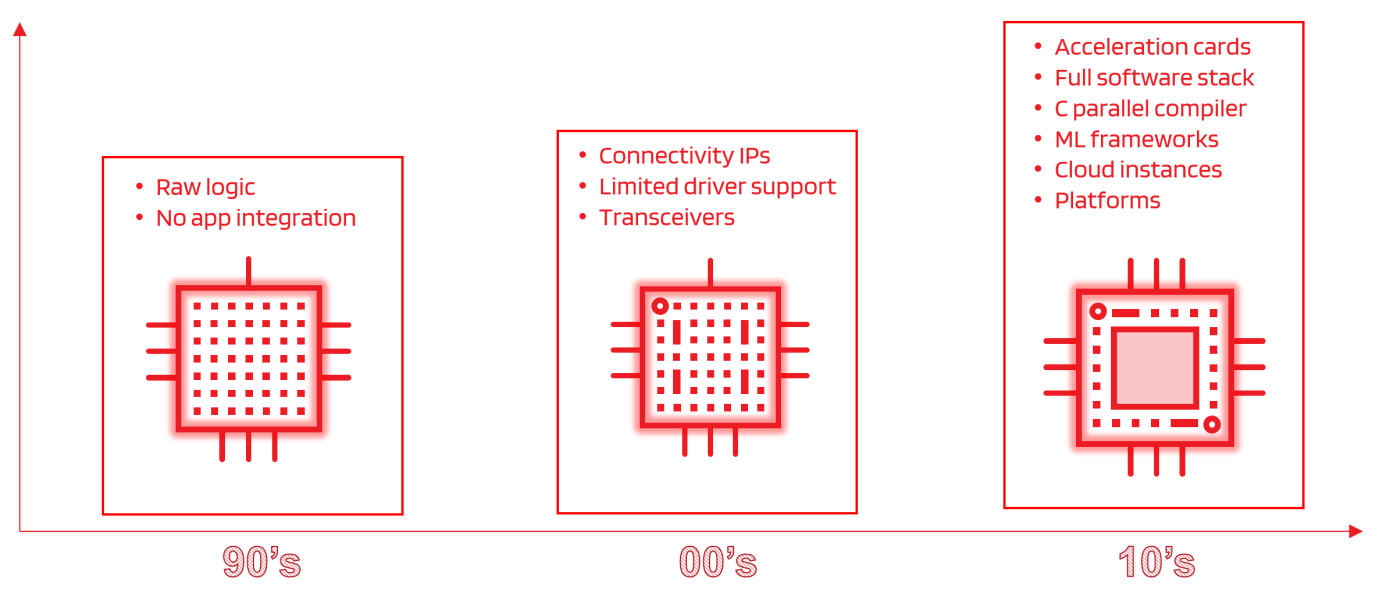

Машинное обучение и глубокое обучение сейчас везде. Новые алгоритмы, новые приложения, новые платформы и новые вычислители/движки/модели появляются каждый день. На этом вебинаре мы рассмотрим глубокое обучение акцентируя внимание на FPGA, которые ориентируются на inference свёрточных нейронных сетей.

13.03.2020

|

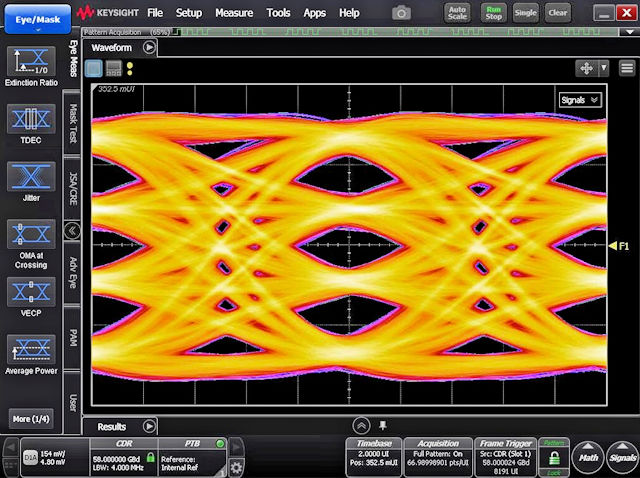

Компания Intel выпустила видеоролик, в котором продемонстрировала работу 116Гб трансиверов PAM4 в кристаллах Agilex I-Series.

12.03.2020

|

Компания Xilinx объявила о выходе очередного кристалла платформы ACAP — Versal Premium Series.

11.03.2020

|

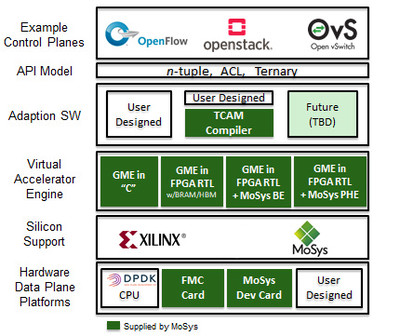

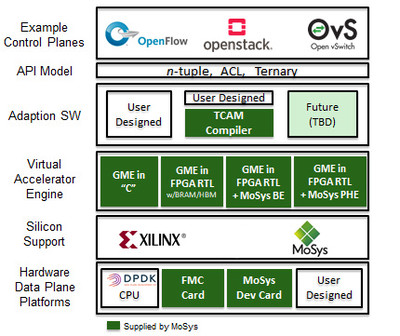

Компания MoSys анонсировала платформу Packet Classification Platform в серии своих программных ускорителей. Данная платформа позволяет использовать виртуальный ускоритель Graph Memory Engine (GME) для поиска и классификации заголовков пакетов данных, как дополнение TCAM функций. Платформа включает GME и ПО с общим API, встраивающее TCAM образы в графы.

23.02.2020

|

ArchES разработала операционную систему для ПЛИС «FinOS» специально для финтеха.

Компания обратилась в центр CENGN для проведения стресс-тестов своего проекта в рамках сетевых проектов «Network Applications».

22.02.2020

|

На вебинаре вы увидите, насколько это быстро и удобно — разрабатывать управляющую логику в помощью Stateflow — мощнейшего инструмента по созданию конечных автоматов, потоков управления и событийных систем. В Stateflow вы вместо написания кода рисуете состояния и переходы, поэтому результат выглядит как блок-схема, в которой легко разобраться и которую легко отладить, благодаря встроенной визуализации переходов между состояниями.

21.02.2020

|

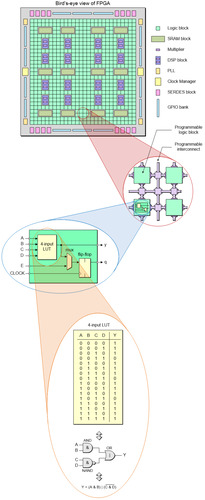

Клайв Максфилд опубликовал очередную статью по ПЛИС для разработчиков, имеющих опыт на микроконтроллерах. В статье раскрываются базовые понятия и устройство ПЛИС.

20.02.2020

|

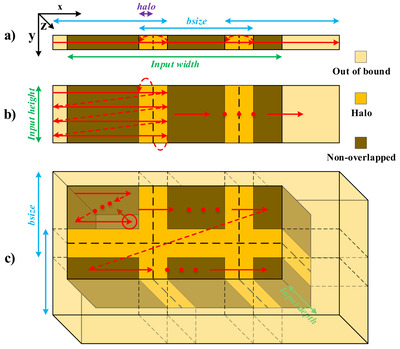

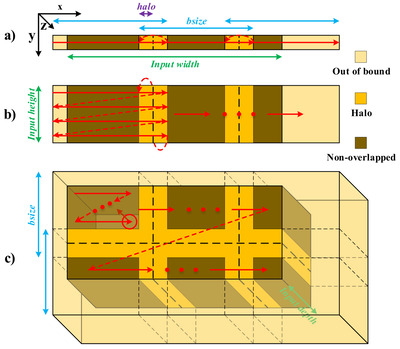

Фирма Edgecotix разработала ПО для тестов OpenCL контроллеров памяти в ПЛИС Intel. Данный набор охватывает ряд шаблонов доступа к памяти, в том числе последовательный доступ, 1D blocking и 1.5D/2.5D overlapped blocking.

20.02.2020

|

На портале LinkedIn выложен обширное руководство по реализации DMA с ядрами Xilinx.

20.02.2020

|

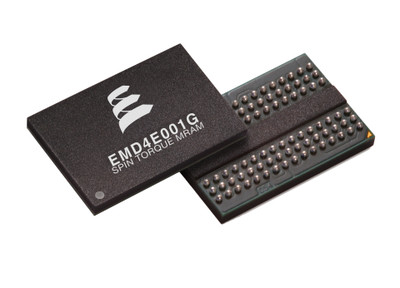

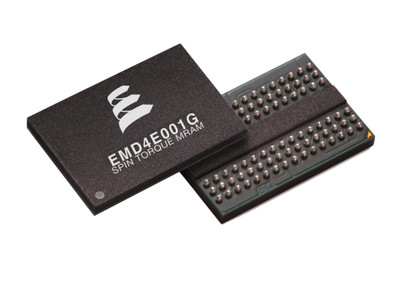

Компания Everspin Technologies (производитель магниторезистивной памяти MRAM) анонсировала полное руководство по использованию своей памяти STT-MRAM 1 Гбит в системах хранения данных, где применяются ПЛИС фирмы Xilinx, Inc.

10.02.2020

|

Реализация конвейера обработки изображений на Genesys ZU 3EG с использованием новейших IP-ядер от Xilinx.

10.02.2020

|

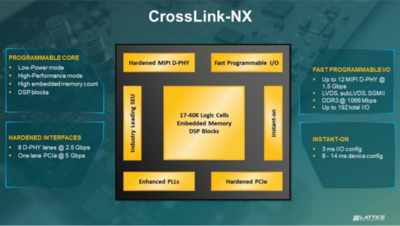

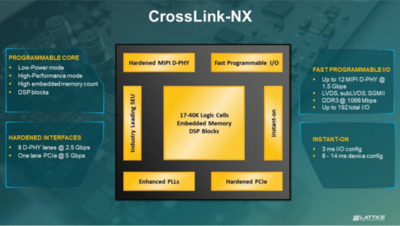

Компания Tirias Research опубликовала статью о семействе ПЛИС CrossLink-NX фирмы Lattice Semiconductor. CrossLink-NX сделан для систем обработки видео. Семейство разработано на новой платформе Lattice — Nexus на техпроцессе 28 нм FD-SOI (на полностью обеднённом кремнии-на-изоляторе). Техпроцесс позволяет значительно снизить потребление и уменьшить размеры по сравнению с аналогичными чипами на КМОП

06.02.2020

|

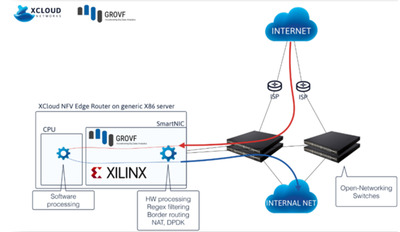

Глубокий анализ пакетов (Deep packet inspection, DPI) — набор методов по проверке и управлению сетевым трафиком. Другими словами, это способы фильтрования с целью обнаружения, сравнения, классификации, маршрутизации и блокирования пакетов с определенными данными или кодом. Данные функции отсутствуют в стандартном сетевом оборудовании.

05.02.2020

|

Плата VP460 фирмы Abaco создана для новейших разработок в области высокопроизводительных процессорных вычислений в радиолокации. VP460 поддерживает стандарт SOSA, совместимый со стандартами ВВС и ВМФ США.

05.02.2020

|

Компания Intel опубликовала новый номер журнала, «Parallel Universe №39». Статьи в этом выпуске сосредоточены на возможностях и использовании OneAPI при программировании гетерогенных систем. Журнал доступен бесплатно — без смс и регистрации.

03.02.2020

|