Как не счесть «алмазов в каменных пещерах» — так не счесть случаев, когда необходимо втиснуть какую-нибудь характеристику «непрерывного» внешнего мира в «дискретное» нутро цифровых алгоритмов или извлечь обратно. Как помнят многие — это делается с помощью аналого-цифровых (АЦП, ADC) и цифро-аналоговых (ЦАП, DAC) преобразователей. Но только более посвящённые — обратят при этом внимание на источник опорного напряжения для преобразований (ИОН, Reference), который во многом определяет стабильность и абсолютную точность полученного результата. Конечно, есть некоторое число случаев, когда можно произвести измерение или генерацию отношения двух токов или напряжений. Тогда достаточно подать большее из них на опорный вход преобразователя. Но это — именно «некоторое число».

Желающих ознакомиться с одним из принципов и одной из реализаций температурно-стабильного ИОН — приглашаю под кат. Помощь в этом — предоставит симулятор LTSPICE (несмотря на то, что человек с КДПВ сказал: «My favorite CAD is solder»). Желательно — знание закона Ома, правил Кирхгофа, принципов работы биполярного транзистора (на уровне модели Эберса-Молла) и идеального операционного усилителя.

КДПВ1: Robert Allan Pease — the czar of bandgap. «Орденские цепи» — из ИМС стабилизаторов в корпусе TO-3.

Скачать архив с примерами и подробными результатами.

Из уравнения модели биполярного транзистора Эберса-Молла Ic = S * Is * [exp(Vbe*q/[k*T]) — 1] следует, что разность напряжений база-эмиттер двух транзисторов пропорциональна отношениям токов коллекторов и их площадей (в основном — их эмиттеров) — dVbe = (k*T/q) * ln[(Ic1 * S2) / (Ic2 * S1)] и абсолютной температуре (Iсn — токи коллекторов и Sn — площади эмиттеров соответствующих транзисторов. q — заряд электрона. k — постоянная Больцмана. T — абсолютная температура. При комнатной температуре kT/q ~ 26 mV). Соединив эмиттерный переход некоего транзистора с некоторым Vbe (имеющим отрицательный температурный коэффициент примерно минус 2 мВ/°C) последовательно с неким участком цепи (имеющим падение напряжения N*dVbe с положительным коэффициентом) и выбрав соответствующее N — можно получить напряжение [почти] неизменное при колебаниях температуры. Его итоговая величина оказывается весьма близкой к потенциалу запрещённой зоны полупроводника, на основе которого изготовлены транзисторы (в пределе, при T⟶0 °K, Vbe стремится к этому значению, а N*dVbe к 0) — поэтому данный тип ИОН называется «ИОН с напряжением запрещённой зоны» или «Bandgap reference». Потенциал запрещённой зоны в SPICE модели биполярного транзистора — это параметр Eg и его коэффициенты GAP1, GAP2.

Рисунок № 1.

Закинем всё это в симулятор LTSPICE в варианте, предложенном Paul Brokaw в 1974 году («A simple three-terminal IC bandgap reference») и рассмотрим пристально. На R2 и R7 выделяются напряжения dVbe с коэффициентом, прямо пропорциональным температуре (датчик температуры — на сдачу). Масштабируя их на R2-R4 или R7-R6 (Vptat — пропорциональное абсолютной температуре) и складывая с Vbe — получаем стабильное Vref. При этом — точность выходного напряжения определяется, в основном, соотношениями площадей эмиттеров и сопротивлений резисторов, что в интегральной микроэлектронике реализуется легче, чем абсолютная точность конкретного элемента.

Слева — с разными токами коллекторов через одинаковые транзисторы. ООС будет поддерживать одинаковое напряжение на коллекторах при разных нагрузочных резисторах. Пренебрегая токами баз транзисторов:

IcQ1*R2 = dVbe1

(IcQ1+IcQ2)*R4 = Vptat1

IcQ1/IcQ2 = R1/R3

=> (1+IcQ2/IcQ1)*R4/R2 = Vptat1/dVbe1

Варьируя R4/R2 при заданных IсQ1/IсQ2 и определяемом ими dVbe1 — получаем Vptat1 с температурным коэффициентом ~ 2 мВ/°C:

Vptat1 / T = (1 + IcQ2/IcQ1) * ln(IcQ2/IcQ1) * (k/q) * (R4/R2)

Справа — с одинаковыми токами через транзисторы с разными площадями эмиттеров, Q4 имеет в m раз большую площадь (или — m параллельных элементов). ООС будет поддерживать одинаковое напряжение на коллекторах при одинаковых нагрузочных резисторах или будет использована местная ОС через токовое зеркало. В итоге — получаются разные плотности токов I/S:

IcQ4*R7 = dVbe2

(IcQ3+IcQ4)*R6 = Vptat2

IcQ3=IcQ4 (т.к. R5=R8)

=> 2*R6/R7 = Vptat2/dVbe2

В итоге: Vptat2 / T = 2 * (k/q) * ln(SQ4/SQ3) * (R6/R7)

Здесь — я предварительно подобрал Vref, R2 и R7 дающие минимальную разность напряжений коллекторов при заданных остальных резисторах. Переставляя точку с запятой (комментарий) в правом блоке чёрного текста можно менять задания для параметров (температуры, сопротивления и т.п.) расчёта рабочей точки (.op).

Рисунок № 2.

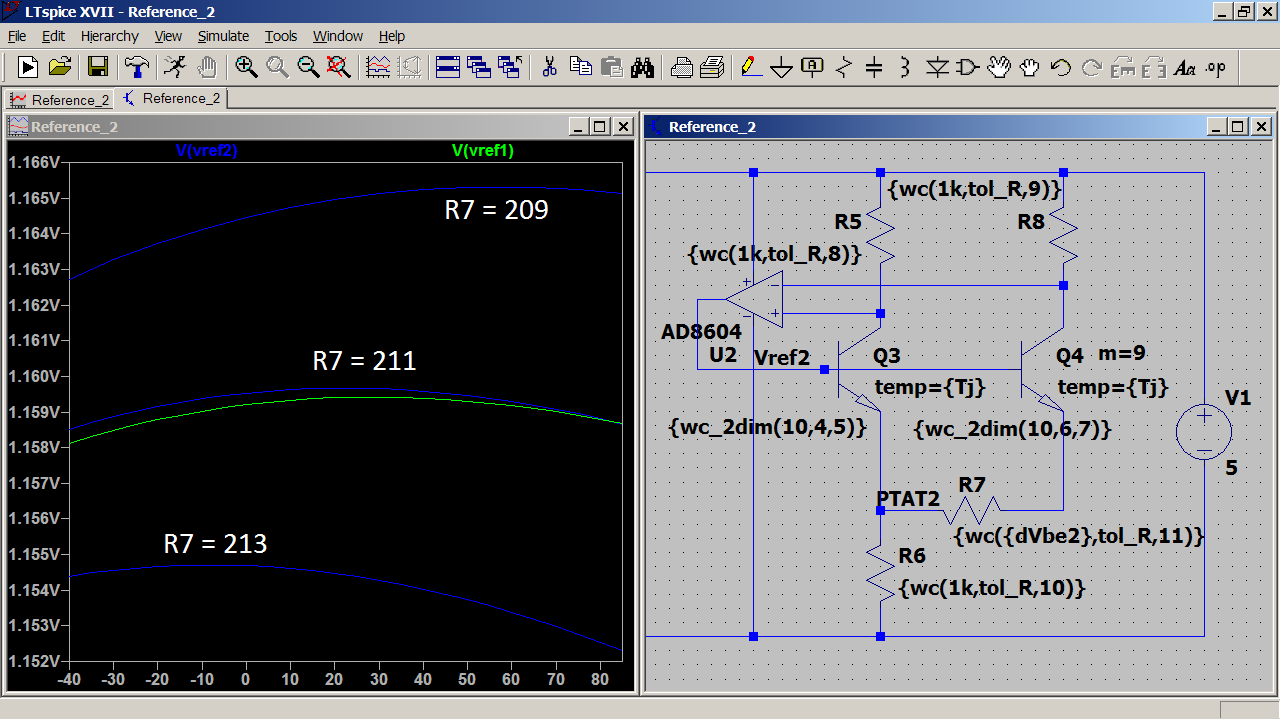

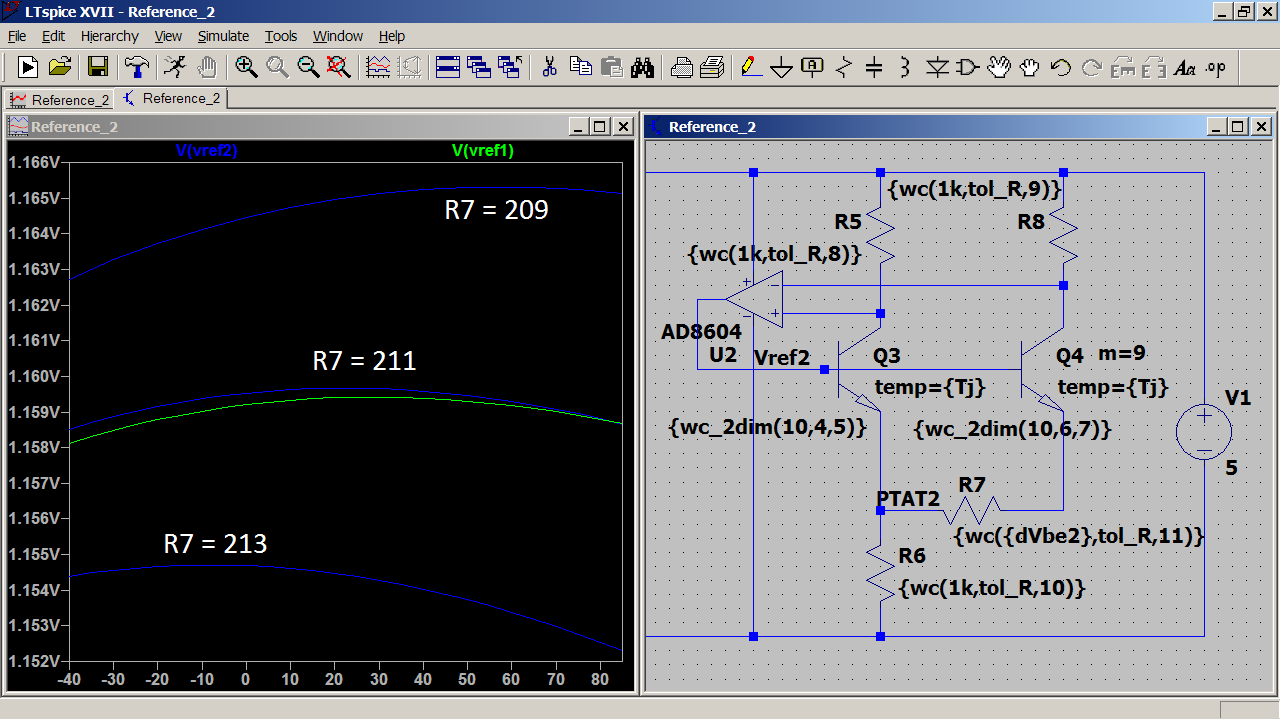

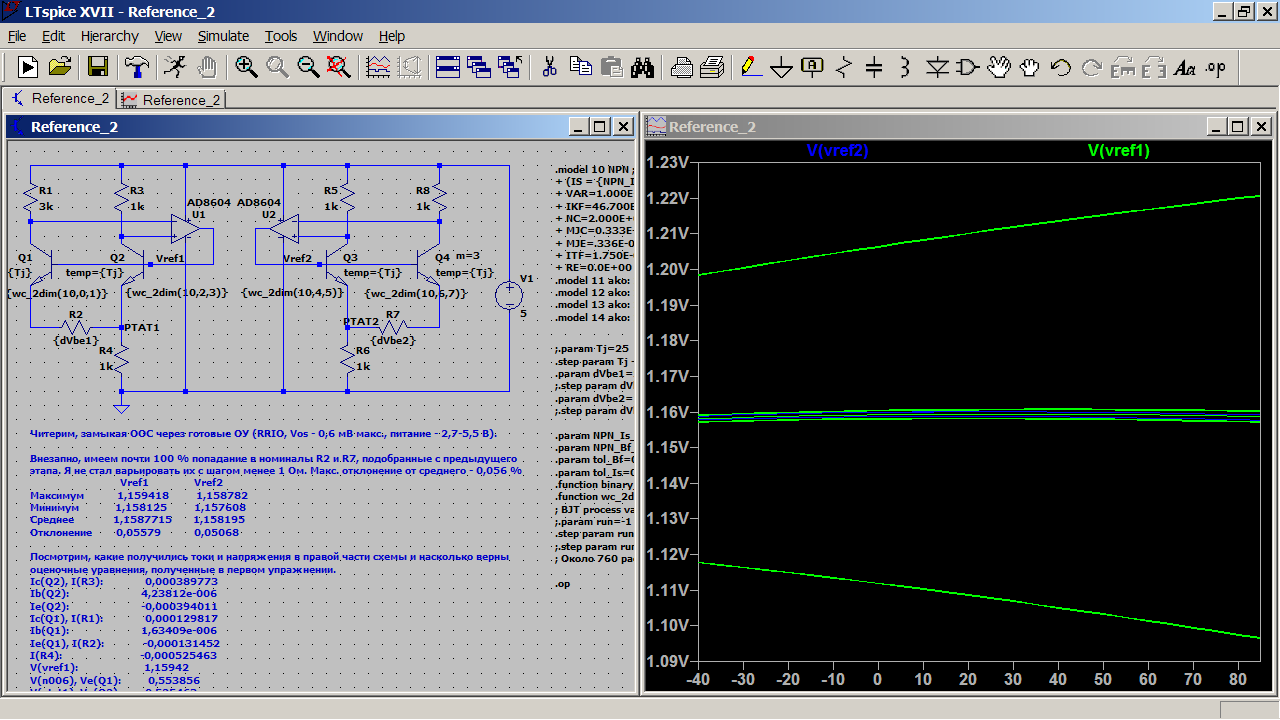

Читерим, замыкая ООС через готовые ОУ (RRIO, Vos — 0,6 мВ макс., питание — 2,7-5,5 В). Внезапно, имеем близкое к 100 % попадание в номиналы R2 и R7, подобранные с предыдущего этапа. Я не стал варьировать их с шагом менее 1 Ом (Рисунок сделан позднее, поэтому на нём Q4 имеет m=9 и другое сопротивление R7. Аутентичный рисунок — следующий). Зелёная кривая — для Q1-Q2-R2, синие — для Q3-Q4 и трёх значений R7 с шагом 2 Ом. При увеличении «сопротивления dVbe» максимум кривой напряжения смещается от больших температур к меньшим, а сама она смещается в сторону меньших напряжений. Максимальное отклонение от среднего при изменении температуры от минус 40 до 85 °C (т.н. «промышленный температурный диапазон») — 0,056 % (далее я называю это «точность», если не указаны другие условия расчёта).

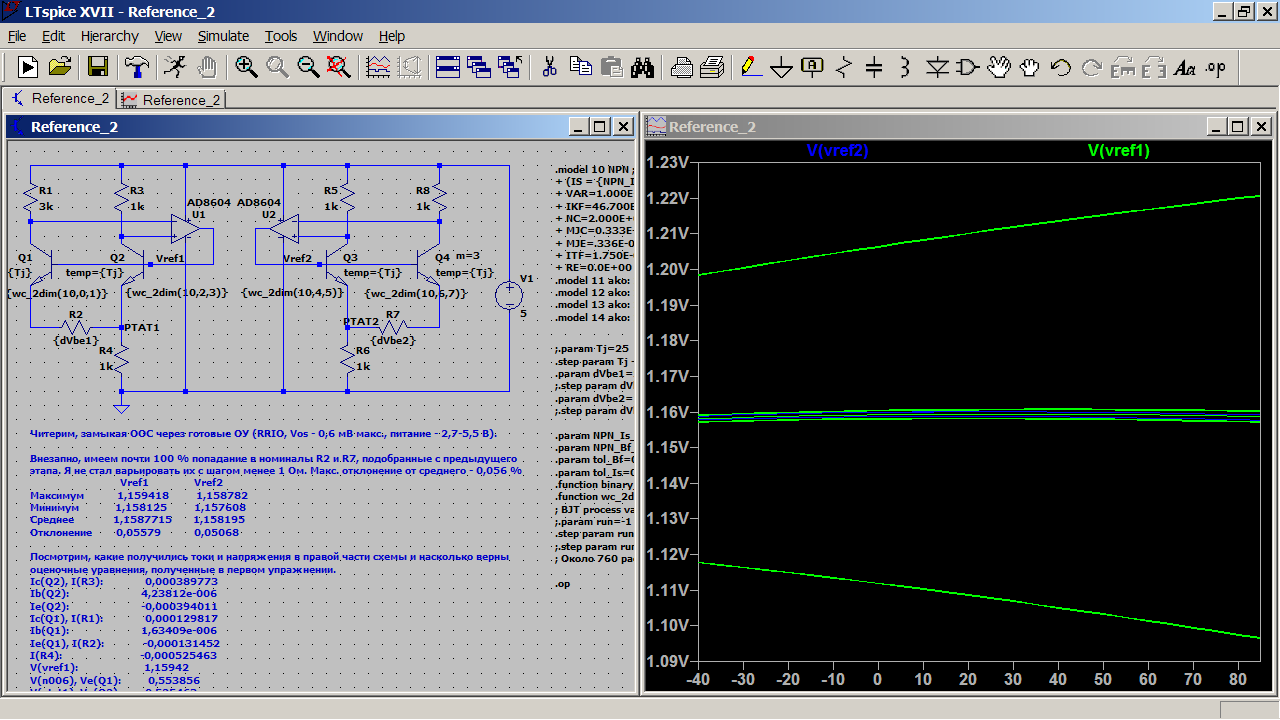

Посмотрим, какие получились токи и напряжения в левой части схемы и насколько верны оценочные уравнения, полученные ранее.

Отношение токов коллекторов — 3,0025 (что не совсем понятно — AD860x со входом на полевых транзисторах и достаточно точный), сумма — 519,59 мкА.

Отношение токов баз — 2,5936, сумма — 5,872 мкА. У транзистора Q1 проявляется падение коэффициента усиления тока при низких токах эмиттера.

Vptat1 / T = (1+IQ2/IQ1) * ln(IQ2/IQ1) * (k/q) * R4/R2 (k = 1,38*10-23 Дж/°C, q = 1,6*10-19 Кл) должен получиться с коэффициентом около 2 мВ * T. По расчёту — 1,75 мВ/°C.

Vptat2 / T = 2 * (k/q) * ln(SQ4/SQ3) * (R6/R7) — расчёт даёт 1,79 мВ/°C (другой ток через Q3).

Тут, вместо того, чтобы проверить влияние технологических разбросов, я бросился конструировать разнообразные химеры. Желающие могут ознакомиться с ними в архиве под именем «uglies». Они порой действительно страшноваты, например — токовое зеркало с разными сопротивлениями в эмиттерах (очевидно — отношение токов будет меняться при изменении их абсолютных значений). Хотя ИОН по мотивам LM317 довольно интересен в разборе принципа действия и характеристик.

В итоге — и от этого нашлась польза. Я заметил, что погоня за минимальным «ppm/°C», рассчитанным по типичному «коробочному» методу, может привести к увеличению абсолютной нестабильности. Analog Devices считает так:

Apex (Thaler) — так:

Комментарий от Хоровица и Хилла.

Здесь и далее я рассчитывал «ppm/°C» опираясь на T1 и T2 соответствующие минимальному и максимальному значениям кривой. При малых отклонениях от точки минимальной абсолютной нестабильности возможны ситуации, когда прирост разности напряжений в числителе оказывается меньше прироста разности температур в знаменателе. Пожалуй — надо было брать полный температурный диапазон и немного улучшить свои результаты?

Теперь — посмотрим на худшие случаи вариаций параметров. В LTSPICE ничего не нашёл по вариации параметров модели для отдельных экземпляров, использующих эту модель (симуляция производственного разброса параметров). Попадалось упоминание, что в PSpice A/D есть отдельный инструмент для учёта разбросов между партиями (Lot), внутри них (Dev) и оценки чувствительности к разбросам конкретного компонента схемы. Пока — только использование «худшего случая» (worst case) и номерных моделей транзисторов с директивой «ako» на базе этих данных:

https://k6jca.blogspot.com/2012/07/monte-carlo-and-worst-case-circuit.html

https://www.analog.com/en/technical-articles/ltspice-worst-case-circuit-analysis-with-minimal-simulations-runs.html

В поле выбора модели каждого транзистора — вставлена функция худшего случая по двум параметрам «wc_2dim» выбирающая модели скорректированные по наиболее «весомым» параметрам для постоянного тока:

— току насыщения Is, который определяет Vbe конкретного транзистора и, опосредованно, температурно-зависимое dVbe в парах;

— коэффициенту Bf, который примерно определяет hfe при средних значениях тока эмиттера (при больших и малых — в дело вступают поправочные коэффициенты ISE, IKF и другие).

Входными параметрами «wc_2dim» являются номер «базовой» модели транзистора и два индекса idx, сравниваемые с переменной run. Начинать номера моделей с 0 — почему-то нельзя (зарезервировано для цепи «земля»?).

Рисунок № 3.

Сперва — при разбросе коэффициента передачи тока транзисторов Q1 и Q2 в 2 % и их тока насыщения 5 % (что даёт постоянную разность Vbe в паре до 2 мВ по модулю при НКУ). Характеристики разбиваются на 4 группы по 4 штуки в каждой, 2 группы — лежат рядом с номинальной характеристикой и имеют близкие к ней ТКН, две — далеко и имеют существенно большие ТКН примерно постоянные по диапазону температур. Сохранив результаты расчёта (ПКМ на листе графика, «File — Export data as text») и обработав их в табличном процессоре видим, что точность разом ухудшается с 0,080 до 5,402 %, а ТКН (рассчитанный по «коробочному» методу для худшего из случаев) — с 15,93 до 153,71 ppm/°C. Для Q3-Q4 (при m=3) — точность падает с 0,068 до 5,517 %, а ТКН растёт с 14,49 до 161,60 ppm/°C. Разбиение позволяет предположить, что один из варьируемых параметров оказывает намного более существенное влияние — это оказывается Is и вызванная им дополнительная температурно-зависимая составляющая dVbe, которую мы не можем учесть в исходных расчётах и подборе резисторов в симуляторе. Простой, очевидный и экстенсивный путь борьбы — «утопить» dVbe, вызванный разбросом параметров, в том dVbe, который мы вызываем сами и можем контролировать.

Недостаток тут один и большой — логарифм отношения токов. Справа — увеличив отношение токов втрое (32 = 9 транзисторов Q4, Camenzind называет максимальное практическое отношение в микроэлектронике на уровне 50 [1]) мы увеличим dVbe всего вдвое (с 24 до 48 мВ). Слева — попроще, в некоторых пределах мы можем выбрать довольно большое отношение R1/R3 (не забывая о диапазоне допустимого синфазного напряжения ОУ и ЭДС шума резисторов с большими номиналами). С другой стороны — увеличение числа транзисторов должно ещё уменьшать паразитный разброс само по себе (пропорционально корню квадратному их числа). Например — прелестная пара транзисторов LM194/394, состоящая из 50 параллельных ячеек для каждого и имеющая финальный разброс 100-250 мкВ. Это довольно похоже на 2 мВ современных согласованных транзисторов (DMMT39xx), делённых на корень квадратный из 50. Но, даже с отношением токов 50, — разброс остаётся большим.

Итог для Q1-Q2 с отношением токов (параметр Left) 50 — точность падает с 0,058 до 1,681 % и ТКН растёт с 13,86 до 45,92 ppm/°C. Негусто, но уже подползаем к уровню <тыщи_их>431!

Для Q3-Q4 (при m=9) — точность падает с 0,066 до 2,859 % и ТКН растёт с 16,47 до 79,28 ppm/°C. Замечание: Тут можно было-бы симулировать каждый из 9 транзисторов Q4 отдельно (или поделить для него tol_Is на √9=3). Но оценка именно худшего случая (все в плюс или минус) — верна.

Влияние резисторов с точностью 1% (на примере правой части схемы с m=9) поменьше — точность падает с 0,066 до 2,299 % и ТКН растёт с 16,47 до 64,90 ppm/°C.

Полные вариации для Q3, Q4, R5-R8 при m=9 — точность падает с 0,066 до 5,144 % и ТКН растёт с 16,47 до 144,01 ppm/°C. Скатываемся куда-то на уровень «хуже 7805».

Рисунок № 4.

Столь же простой и экстенсивный, но более действенный путь — подстройка отношений резисторов. Для получения минимального ТКН, если нам достаточно просто термостабильного напряжения, потребуется подстройка как минимум одного резистора в парах R2-R4 и R6-R7. «Чему в истории мы тьму примеров сыщем» — начиная от «вульгарных» LM317 (https://richis-lab.de) с пережигаемыми перемычками в слое металлизации (STMicroelectronics, обратите внимание — подстройка в весьма широком диапазоне) или стабилитронами (NSC), через <их_тыщи>431, до прецизионных ИОН типа AD584 с лазерной подстройкой тонкоплёночных(?) резисторов.

В финале, если нужна ещё и заданная величина выходного напряжения, — надо подстроить и делитель в цепи ОС выходного усилителя (R48 на рисунке № 6).

Рисунок № 6.

Пример компенсации квадратичной нелинейности (Q3 — на одном кристалле с Q2, Q5). При Run=0 (R4 > 0 и Q3 работает) выходное напряжение меняется менее, чем на 452 мкВ во всём диапазоне температур. Примерно в 2-3 раза лучше «базовой» схемы. Исходные посылки — смотрите у Camenzind, fig. 7-14, 7-15 в [1], Brokaw на стр. 38-43 в [2] и Pease на стр. 2-3 в [3].

Рисунок № 8.

R1 подбирается так, чтобы максимум выходного напряжения без действия Q3 был смещён в область пониженных температур и была «удлиннённая» спадающая ветвь в области повышенных. Подбором соотношения R3 и R4 (при фиксированной сумме) — определяем момент вступления в дело Q3 при повышении температуры. Совместным подбором R2-R4 минимизируем разность максимального и минимального напряжений. Не забудьте, что в результате датчик температуры станет привирать!

Можно разбить R1 на части и подключить коллектор Q3 в точку их соединения. Тогда можно будет понизить номинал R2 (меньше шум, проще реализация в ИС). Но делать его сильно маленьким (менее 3-10 кОм) нецелесообразно, т.к. эмиттерный переход Q3 станет заметно шунтировать R4.

Моделировать разброс по параметрам цепи коррекции — как-то страшновато. Вдруг всё сломается? Кто сделает? ;-)

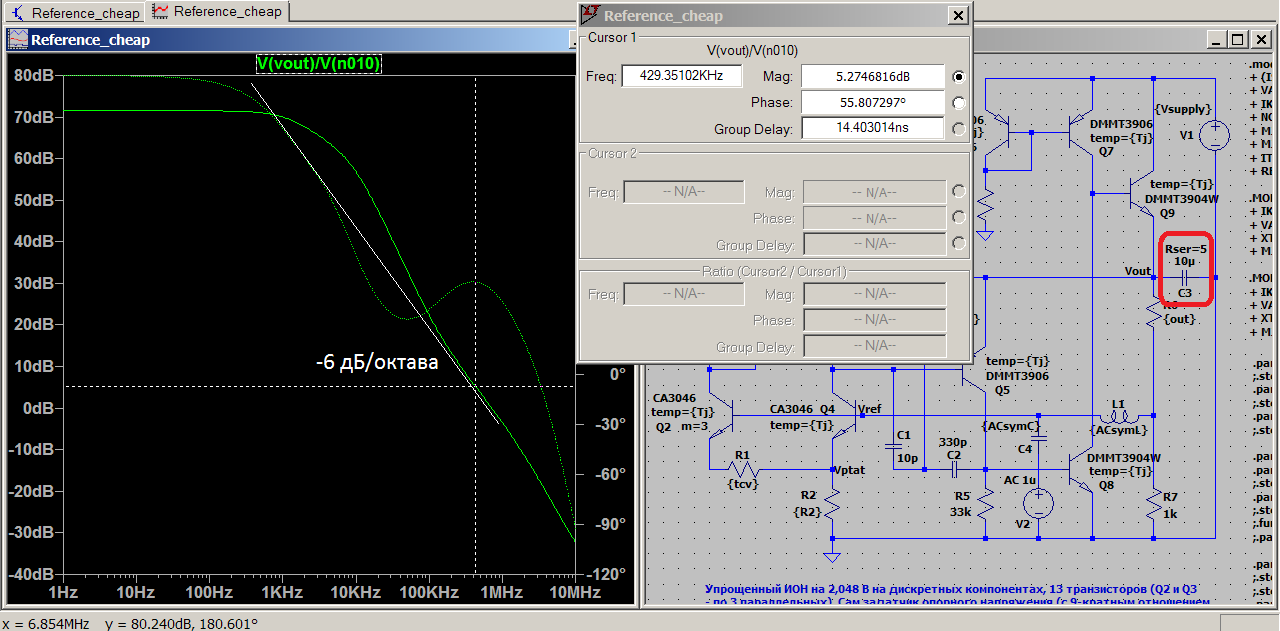

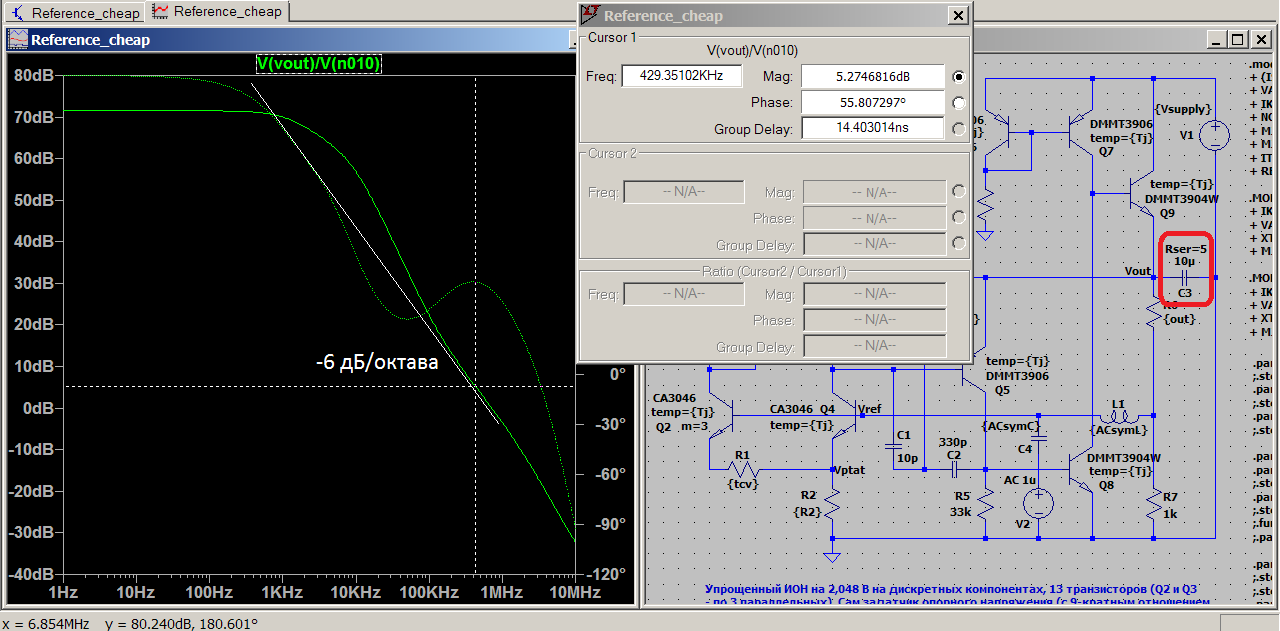

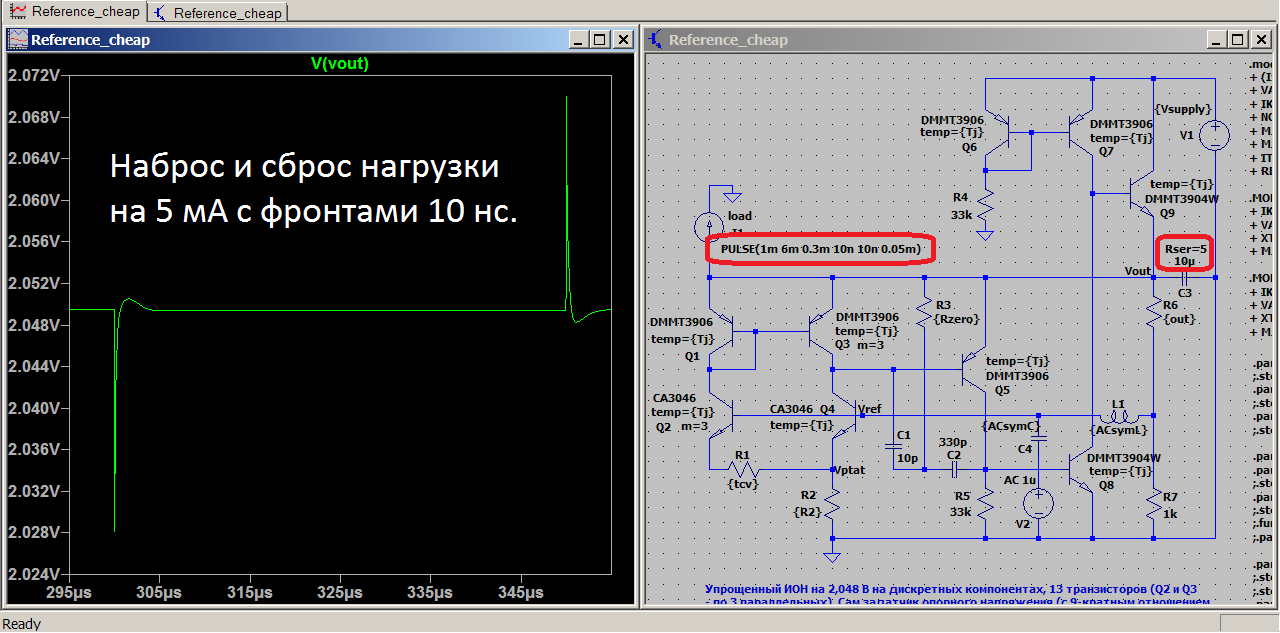

В конце, для тренировки остатков мозга и набития фрагов в обращении с LTSPICE разработал «на бумаге» упрощенный ИОН на 2,048 В на дискретных компонентах — 13 транзисторов (Q2 и Q3 — по 3 параллельных), два подборных резистора (по одному в парах R1-R2 и R6-R7). Q2 и Q4 — согласованная сборка CA3046, LM3046, TBA331 (сейчас производятся HFA3046, NTE912 или взять DMMT3904 или BCM84x или, из «наших», 198НТ1 или КТ222). Последний, пятый, транзистор в её составе попробуем оставить «про запас». Сам задатчик опорного напряжения Q1-Q4 (с 9-кратным отношением токов, раз уж всё равно надо подстраивать резисторы) является и первым каскадом усилителя ОС. Q6 и Q7 — обеспечивают запуск и формируют нагрузку для Q8. R4 и R5 — достаточны с допуском 5%. С погрешностью установки выходного напряжения от пропорциональных температуре базовых токов Q2 и Q4 борюсь очень грубой силой — увеличением тока делителя R6 и R7. Так и частотные характеристики несколько улучшаются, т.к. это нагрузка выходного каскада. L1, C4 и V2 — для анализа АФЧХ при разомнутой ОС по переменному току (задать L1 и C4 — по 1 Meg). C1, C2 и R3 формируют двухполюсную коррекцию АЧХ — в меру своего незнания пытаюсь расширить частотный диапазон, в котором доступно повышенное петлевое усиление. На LDO'шность прокачивать не стал, минимальное напряжение питания при симуляции — 4 В (вероятно — и от 3 В будет ещё прилично работать).

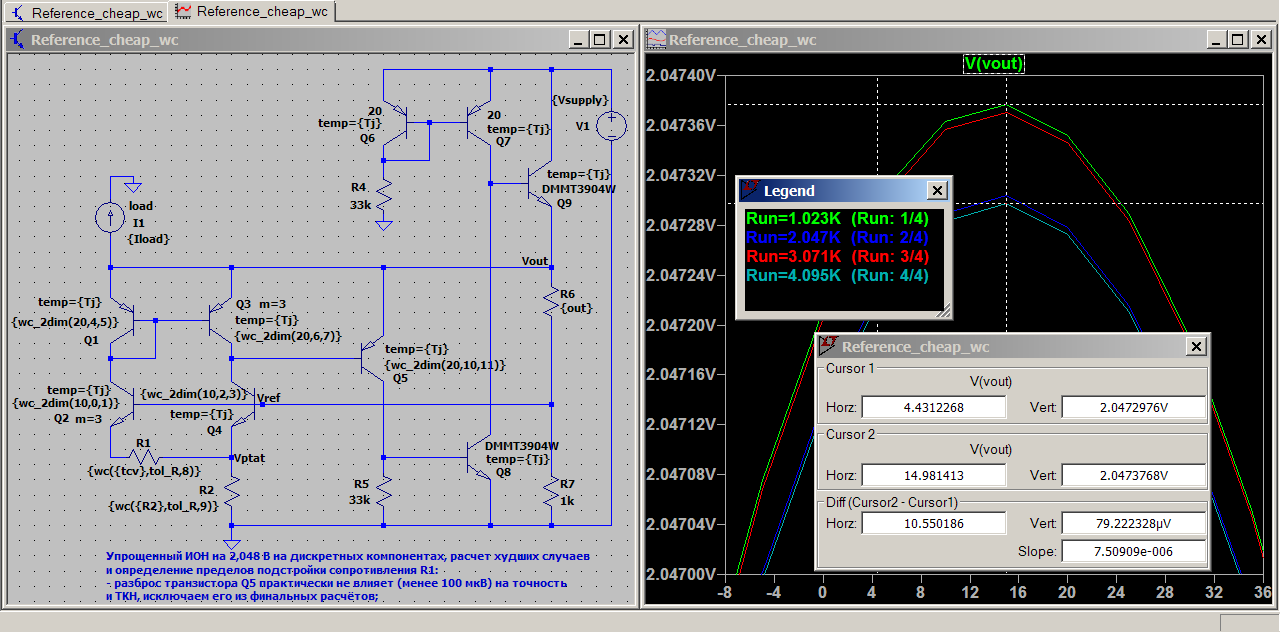

Для наглядности — всем 4 значениям R1 сопоставлены подходящие к заданному выходному напряжению значения R6. Поэтому кривые Vout расположены не так, как на рисунке № 2. При выбранном R2 = 1 кОм, минимальный ТКН (3,237 мВ в абсолютном выражении, 26,324 ppm/°C) получается при R1 = 443 Ом. Расчёт Vptat / T = 4 * (k/q) * ln(9) * (R2/R1) даёт 1,71 мВ/°C (4 это 1 плюс отношение тока эмиттера Q4 к току R1), а по результатам симуляции — 1,76 мВ/°C.

Рисунок № 9.

Рисунок № 10 — АФЧХ.

Вариации выходного напряжения:

А зачем пытаться съэкономить пятый транзистор сборки? Вот два варианта:

В заключение — закидываю и этот ИОН в «суровый прод». Расчет худших случаев и определение требуемых пределов подстройки сопротивления R1 (выгрузка результата «worst cases» в табличный процессор, определение худших run's по минимальному и максимальному среднему напряжению, подбор R1 для найденных run's):

Разбив R1 на 5 резисторов, например — 11,3+22,6+45,3+90,9+365 Ом по ряду E96, можно перекрыть весь диапазон с разрешением 4 бита (16 равноотстоящих промежуточных значений). Также можно изменить значения с учётом имеющегося сдвига 11,3+22,6+45,3+365 > 443 (ном.) и/или скорректировать веса принимая нормальное распределение погрешностей.

Вывод. К #импортозамещение — готов? ;-)

Литература, в порядке использования:

[1] Книга Hans Camenzind, «Designing analog chips»

[2] Печатная лекция A. Paul Brokaw, «How to make a bandgap voltage reference in one easy lesson»

[3] Пара избранных заметок Robert A. Pease, «The Design of Band-Gap Reference Circuits: Trials and Tribulations» и «What's All This VBE Stuff, Anyhow?»

Более-менее полное ПСС Боба — смотрите тут. В заметке «How To Make Your Own Matched Transistors» Вы можете найти базовую идею схемы для подбора парных транзисторов при необходимости и упоминание о том, что, как правило, сборки 3046 согласованы лучше, чем на 1 мВ.

И — ещё одно его фото в царском костюме, с пригоршней ИМС в ладонях:

[4] Или — попробуйте найти [3] в испохабленном «грязными ковбоями» виде на сайте www.ti.com или на их форуме e2e.ti.com

Synopsys: Simulating Brokaw bandgap reference in LTSPICE, BJT DC parameters variation in LTSPICE.

Желающих ознакомиться с одним из принципов и одной из реализаций температурно-стабильного ИОН — приглашаю под кат. Помощь в этом — предоставит симулятор LTSPICE (несмотря на то, что человек с КДПВ сказал: «My favorite CAD is solder»). Желательно — знание закона Ома, правил Кирхгофа, принципов работы биполярного транзистора (на уровне модели Эберса-Молла) и идеального операционного усилителя.

КДПВ1: Robert Allan Pease — the czar of bandgap. «Орденские цепи» — из ИМС стабилизаторов в корпусе TO-3.

Лирическое отступление

Как-то и сам я, осваивая 2-е переводное издание «Искусства схемотехники», макетировал подобную схему IRL. Наподобие Figure 9.91 из третьего издания в переводе teap0t, только с простым источником тока. При помещении транзисторной сборки 198НТ1 в кипяток, стрелка АВО-5М смещалась менее, чем на свою ширину.

КДПВ2: Бендер «Сгибатель» Родригез смотрит порножурнал (S1E10?).

КДПВ2: Бендер «Сгибатель» Родригез смотрит порножурнал (S1E10?).

Скачать архив с примерами и подробными результатами.

Из уравнения модели биполярного транзистора Эберса-Молла Ic = S * Is * [exp(Vbe*q/[k*T]) — 1] следует, что разность напряжений база-эмиттер двух транзисторов пропорциональна отношениям токов коллекторов и их площадей (в основном — их эмиттеров) — dVbe = (k*T/q) * ln[(Ic1 * S2) / (Ic2 * S1)] и абсолютной температуре (Iсn — токи коллекторов и Sn — площади эмиттеров соответствующих транзисторов. q — заряд электрона. k — постоянная Больцмана. T — абсолютная температура. При комнатной температуре kT/q ~ 26 mV). Соединив эмиттерный переход некоего транзистора с некоторым Vbe (имеющим отрицательный температурный коэффициент примерно минус 2 мВ/°C) последовательно с неким участком цепи (имеющим падение напряжения N*dVbe с положительным коэффициентом) и выбрав соответствующее N — можно получить напряжение [почти] неизменное при колебаниях температуры. Его итоговая величина оказывается весьма близкой к потенциалу запрещённой зоны полупроводника, на основе которого изготовлены транзисторы (в пределе, при T⟶0 °K, Vbe стремится к этому значению, а N*dVbe к 0) — поэтому данный тип ИОН называется «ИОН с напряжением запрещённой зоны» или «Bandgap reference». Потенциал запрещённой зоны в SPICE модели биполярного транзистора — это параметр Eg и его коэффициенты GAP1, GAP2.

Рисунок № 1.

Закинем всё это в симулятор LTSPICE в варианте, предложенном Paul Brokaw в 1974 году («A simple three-terminal IC bandgap reference») и рассмотрим пристально. На R2 и R7 выделяются напряжения dVbe с коэффициентом, прямо пропорциональным температуре (датчик температуры — на сдачу). Масштабируя их на R2-R4 или R7-R6 (Vptat — пропорциональное абсолютной температуре) и складывая с Vbe — получаем стабильное Vref. При этом — точность выходного напряжения определяется, в основном, соотношениями площадей эмиттеров и сопротивлений резисторов, что в интегральной микроэлектронике реализуется легче, чем абсолютная точность конкретного элемента.

Слева — с разными токами коллекторов через одинаковые транзисторы. ООС будет поддерживать одинаковое напряжение на коллекторах при разных нагрузочных резисторах. Пренебрегая токами баз транзисторов:

IcQ1*R2 = dVbe1

(IcQ1+IcQ2)*R4 = Vptat1

IcQ1/IcQ2 = R1/R3

=> (1+IcQ2/IcQ1)*R4/R2 = Vptat1/dVbe1

Варьируя R4/R2 при заданных IсQ1/IсQ2 и определяемом ими dVbe1 — получаем Vptat1 с температурным коэффициентом ~ 2 мВ/°C:

Vptat1 / T = (1 + IcQ2/IcQ1) * ln(IcQ2/IcQ1) * (k/q) * (R4/R2)

Справа — с одинаковыми токами через транзисторы с разными площадями эмиттеров, Q4 имеет в m раз большую площадь (или — m параллельных элементов). ООС будет поддерживать одинаковое напряжение на коллекторах при одинаковых нагрузочных резисторах или будет использована местная ОС через токовое зеркало. В итоге — получаются разные плотности токов I/S:

IcQ4*R7 = dVbe2

(IcQ3+IcQ4)*R6 = Vptat2

IcQ3=IcQ4 (т.к. R5=R8)

=> 2*R6/R7 = Vptat2/dVbe2

В итоге: Vptat2 / T = 2 * (k/q) * ln(SQ4/SQ3) * (R6/R7)

Строго, с учётом токов баз:

[1 + (IcQ2+IbQ2) / (IcQ1+IbQ1)] * R4/R2 = Vptat1/dVbe1

[1 + (IcQ3+IbQ3) / (IcQ4+IbQ4)] * R6/R7 = Vptat2/dVbe2

[1 + (IcQ3+IbQ3) / (IcQ4+IbQ4)] * R6/R7 = Vptat2/dVbe2

Здесь — я предварительно подобрал Vref, R2 и R7 дающие минимальную разность напряжений коллекторов при заданных остальных резисторах. Переставляя точку с запятой (комментарий) в правом блоке чёрного текста можно менять задания для параметров (температуры, сопротивления и т.п.) расчёта рабочей точки (.op).

Рисунок № 2.

Читерим, замыкая ООС через готовые ОУ (RRIO, Vos — 0,6 мВ макс., питание — 2,7-5,5 В). Внезапно, имеем близкое к 100 % попадание в номиналы R2 и R7, подобранные с предыдущего этапа. Я не стал варьировать их с шагом менее 1 Ом (Рисунок сделан позднее, поэтому на нём Q4 имеет m=9 и другое сопротивление R7. Аутентичный рисунок — следующий). Зелёная кривая — для Q1-Q2-R2, синие — для Q3-Q4 и трёх значений R7 с шагом 2 Ом. При увеличении «сопротивления dVbe» максимум кривой напряжения смещается от больших температур к меньшим, а сама она смещается в сторону меньших напряжений. Максимальное отклонение от среднего при изменении температуры от минус 40 до 85 °C (т.н. «промышленный температурный диапазон») — 0,056 % (далее я называю это «точность», если не указаны другие условия расчёта).

| Vref1 | Vref2 | |

|---|---|---|

| Максимум, В | 1,159418 | 1,158782 |

| Минимум, В | 1,158125 | 1,157608 |

| Среднее, В | 1,1587715 | 1,158195 |

| Отклонение, % | 0,05579 | 0,05068 |

Посмотрим, какие получились токи и напряжения в левой части схемы и насколько верны оценочные уравнения, полученные ранее.

| Параметр | Значение, В или А |

|---|---|

| Ic(Q2), I(R3) | 0,000389773 |

| Ib(Q2) | 4,23812e-006 |

| Ie(Q2) | -0,000394011 |

| Ic(Q1), I(R1) | 0,000129817 |

| Ib(Q1) | 1,63409e-006 |

| Ie(Q1), I(R2) | -0,000131452 |

| I(R4) | -0,000525463 |

| V(vref1) | 1,15942 |

| V(n006), Ve(Q1) | 0,553856 |

| V(ptat1), Ve(Q2) | 0,525463 |

Отношение токов коллекторов — 3,0025 (что не совсем понятно — AD860x со входом на полевых транзисторах и достаточно точный), сумма — 519,59 мкА.

Отношение токов баз — 2,5936, сумма — 5,872 мкА. У транзистора Q1 проявляется падение коэффициента усиления тока при низких токах эмиттера.

Vptat1 / T = (1+IQ2/IQ1) * ln(IQ2/IQ1) * (k/q) * R4/R2 (k = 1,38*10-23 Дж/°C, q = 1,6*10-19 Кл) должен получиться с коэффициентом около 2 мВ * T. По расчёту — 1,75 мВ/°C.

Vptat2 / T = 2 * (k/q) * ln(SQ4/SQ3) * (R6/R7) — расчёт даёт 1,79 мВ/°C (другой ток через Q3).

Тут, вместо того, чтобы проверить влияние технологических разбросов, я бросился конструировать разнообразные химеры. Желающие могут ознакомиться с ними в архиве под именем «uglies». Они порой действительно страшноваты, например — токовое зеркало с разными сопротивлениями в эмиттерах (очевидно — отношение токов будет меняться при изменении их абсолютных значений). Хотя ИОН по мотивам LM317 довольно интересен в разборе принципа действия и характеристик.

В итоге — и от этого нашлась польза. Я заметил, что погоня за минимальным «ppm/°C», рассчитанным по типичному «коробочному» методу, может привести к увеличению абсолютной нестабильности. Analog Devices считает так:

The change of output voltage over the operating temperature change and normalized by the output voltage at 25°C, expressed in ppm/°C. The equation follows: TCVout [ppm/°C] = 106 * [Vout(T2)−Vout(T1)] / [Vout(25°C) * (T2 − T1)]

Apex (Thaler) — так:

The temperature coefficient (TC) is determined by the box method using the following formula: TC = 106 * [Vmax−Vmin] / [Vnom * (Tmax − Tmin)]

Комментарий от Хоровица и Хилла.

Здесь и далее я рассчитывал «ppm/°C» опираясь на T1 и T2 соответствующие минимальному и максимальному значениям кривой. При малых отклонениях от точки минимальной абсолютной нестабильности возможны ситуации, когда прирост разности напряжений в числителе оказывается меньше прироста разности температур в знаменателе. Пожалуй — надо было брать полный температурный диапазон и немного улучшить свои результаты?

Теперь — посмотрим на худшие случаи вариаций параметров. В LTSPICE ничего не нашёл по вариации параметров модели для отдельных экземпляров, использующих эту модель (симуляция производственного разброса параметров). Попадалось упоминание, что в PSpice A/D есть отдельный инструмент для учёта разбросов между партиями (Lot), внутри них (Dev) и оценки чувствительности к разбросам конкретного компонента схемы. Пока — только использование «худшего случая» (worst case) и номерных моделей транзисторов с директивой «ako» на базе этих данных:

https://k6jca.blogspot.com/2012/07/monte-carlo-and-worst-case-circuit.html

https://www.analog.com/en/technical-articles/ltspice-worst-case-circuit-analysis-with-minimal-simulations-runs.html

В поле выбора модели каждого транзистора — вставлена функция худшего случая по двум параметрам «wc_2dim» выбирающая модели скорректированные по наиболее «весомым» параметрам для постоянного тока:

— току насыщения Is, который определяет Vbe конкретного транзистора и, опосредованно, температурно-зависимое dVbe в парах;

— коэффициенту Bf, который примерно определяет hfe при средних значениях тока эмиттера (при больших и малых — в дело вступают поправочные коэффициенты ISE, IKF и другие).

Входными параметрами «wc_2dim» являются номер «базовой» модели транзистора и два индекса idx, сравниваемые с переменной run. Начинать номера моделей с 0 — почему-то нельзя (зарезервировано для цепи «земля»?).

Рисунок № 3.

Сперва — при разбросе коэффициента передачи тока транзисторов Q1 и Q2 в 2 % и их тока насыщения 5 % (что даёт постоянную разность Vbe в паре до 2 мВ по модулю при НКУ). Характеристики разбиваются на 4 группы по 4 штуки в каждой, 2 группы — лежат рядом с номинальной характеристикой и имеют близкие к ней ТКН, две — далеко и имеют существенно большие ТКН примерно постоянные по диапазону температур. Сохранив результаты расчёта (ПКМ на листе графика, «File — Export data as text») и обработав их в табличном процессоре видим, что точность разом ухудшается с 0,080 до 5,402 %, а ТКН (рассчитанный по «коробочному» методу для худшего из случаев) — с 15,93 до 153,71 ppm/°C. Для Q3-Q4 (при m=3) — точность падает с 0,068 до 5,517 %, а ТКН растёт с 14,49 до 161,60 ppm/°C. Разбиение позволяет предположить, что один из варьируемых параметров оказывает намного более существенное влияние — это оказывается Is и вызванная им дополнительная температурно-зависимая составляющая dVbe, которую мы не можем учесть в исходных расчётах и подборе резисторов в симуляторе. Простой, очевидный и экстенсивный путь борьбы — «утопить» dVbe, вызванный разбросом параметров, в том dVbe, который мы вызываем сами и можем контролировать.

Недостаток тут один и большой — логарифм отношения токов. Справа — увеличив отношение токов втрое (32 = 9 транзисторов Q4, Camenzind называет максимальное практическое отношение в микроэлектронике на уровне 50 [1]) мы увеличим dVbe всего вдвое (с 24 до 48 мВ). Слева — попроще, в некоторых пределах мы можем выбрать довольно большое отношение R1/R3 (не забывая о диапазоне допустимого синфазного напряжения ОУ и ЭДС шума резисторов с большими номиналами). С другой стороны — увеличение числа транзисторов должно ещё уменьшать паразитный разброс само по себе (пропорционально корню квадратному их числа). Например — прелестная пара транзисторов LM194/394, состоящая из 50 параллельных ячеек для каждого и имеющая финальный разброс 100-250 мкВ. Это довольно похоже на 2 мВ современных согласованных транзисторов (DMMT39xx), делённых на корень квадратный из 50. Но, даже с отношением токов 50, — разброс остаётся большим.

Итог для Q1-Q2 с отношением токов (параметр Left) 50 — точность падает с 0,058 до 1,681 % и ТКН растёт с 13,86 до 45,92 ppm/°C. Негусто, но уже подползаем к уровню <тыщи_их>431!

Для Q3-Q4 (при m=9) — точность падает с 0,066 до 2,859 % и ТКН растёт с 16,47 до 79,28 ppm/°C. Замечание: Тут можно было-бы симулировать каждый из 9 транзисторов Q4 отдельно (или поделить для него tol_Is на √9=3). Но оценка именно худшего случая (все в плюс или минус) — верна.

Влияние резисторов с точностью 1% (на примере правой части схемы с m=9) поменьше — точность падает с 0,066 до 2,299 % и ТКН растёт с 16,47 до 64,90 ppm/°C.

Полные вариации для Q3, Q4, R5-R8 при m=9 — точность падает с 0,066 до 5,144 % и ТКН растёт с 16,47 до 144,01 ppm/°C. Скатываемся куда-то на уровень «хуже 7805».

Рисунок № 4.

Столь же простой и экстенсивный, но более действенный путь — подстройка отношений резисторов. Для получения минимального ТКН, если нам достаточно просто термостабильного напряжения, потребуется подстройка как минимум одного резистора в парах R2-R4 и R6-R7. «Чему в истории мы тьму примеров сыщем» — начиная от «вульгарных» LM317 (https://richis-lab.de) с пережигаемыми перемычками в слое металлизации (STMicroelectronics, обратите внимание — подстройка в весьма широком диапазоне) или стабилитронами (NSC), через <их_тыщи>431, до прецизионных ИОН типа AD584 с лазерной подстройкой тонкоплёночных(?) резисторов.

AD584 от BarsMonster

Обратите внимание, фактически R38 (между базами Q1 и Q2) — отсутствует. Место подгонки R30 — выделено стрелкой справа посередине.

Рисунок № 5.

Рисунок № 5.

В финале, если нужна ещё и заданная величина выходного напряжения, — надо подстроить и делитель в цепи ОС выходного усилителя (R48 на рисунке № 6).

Рисунок № 6.

А также:

- Не рассмотрен ТКС резисторов (от ±50-100 ppm/°C для точности 1% до ±единиц ppm/°C для более точных). Допустимо ли утверждать, что у резисторов близких номиналов, одного производителя и одной партии — сопротивления дрейфуют согласованно?

- Не рассмотрены методы обеспечения одинаковой температуры для всех ключевых элементов и минимизации температурных градиентов [ссылка в 3].

- В финале речь пойдёт о разбиении резистора на части для точной подстройки. Если делать это в «дискрете», то понадобятся запаиваемые (или перерезаемые) перемычки на плате. Можно подискутировать об их термоЭДС (для запаиваемых) или о влагопоглощении повреждённого места печатной платы (для перерезаемых). ТермоЭДС представляется мне меньшим злом, т.к. это будут два встречно включенных спая, находящихся при очень близкой температуре.

- Можно даже занырнуть в кроличью нору подфорума «Метрология» на electronix.ru — и почитать прикреплённый топик. Конвективные потоки воздуха, изгибы печатной платы и т.п.

Пример компенсации квадратичной нелинейности (Q3 — на одном кристалле с Q2, Q5). При Run=0 (R4 > 0 и Q3 работает) выходное напряжение меняется менее, чем на 452 мкВ во всём диапазоне температур. Примерно в 2-3 раза лучше «базовой» схемы. Исходные посылки — смотрите у Camenzind, fig. 7-14, 7-15 в [1], Brokaw на стр. 38-43 в [2] и Pease на стр. 2-3 в [3].

Рисунок № 8.

R1 подбирается так, чтобы максимум выходного напряжения без действия Q3 был смещён в область пониженных температур и была «удлиннённая» спадающая ветвь в области повышенных. Подбором соотношения R3 и R4 (при фиксированной сумме) — определяем момент вступления в дело Q3 при повышении температуры. Совместным подбором R2-R4 минимизируем разность максимального и минимального напряжений. Не забудьте, что в результате датчик температуры станет привирать!

Можно разбить R1 на части и подключить коллектор Q3 в точку их соединения. Тогда можно будет понизить номинал R2 (меньше шум, проще реализация в ИС). Но делать его сильно маленьким (менее 3-10 кОм) нецелесообразно, т.к. эмиттерный переход Q3 станет заметно шунтировать R4.

Моделировать разброс по параметрам цепи коррекции — как-то страшновато. Вдруг всё сломается? Кто сделает? ;-)

P.S.

Отношение токов я задал в 9 раз (ном.) и с небольшой хитростью. 3 набрал в самом формирователе опорного напряжения и 3 — в его нагрузке, токовом зеркале. Такой ход может позволить существенно уменьшить число транзисторов при необходимости. Если взять зеркало с делением токов 1:1, то в этой схеме понадобится 12 транзисторов (Q1, Q3, Q4 — по одному, Q2 — 9 штук). А так — 8. Если брать отношение токов 49 — то в стандартной схеме надо 52 транзистора, а в «хитрой» — только 16. Идея вполне очевидна. Но, если её никто ещё не придумал и не запатентовал, — то дарю её всем по CC BY-SA.

В конце, для тренировки остатков мозга и набития фрагов в обращении с LTSPICE разработал «на бумаге» упрощенный ИОН на 2,048 В на дискретных компонентах — 13 транзисторов (Q2 и Q3 — по 3 параллельных), два подборных резистора (по одному в парах R1-R2 и R6-R7). Q2 и Q4 — согласованная сборка CA3046, LM3046, TBA331 (сейчас производятся HFA3046, NTE912 или взять DMMT3904 или BCM84x или, из «наших», 198НТ1 или КТ222). Последний, пятый, транзистор в её составе попробуем оставить «про запас». Сам задатчик опорного напряжения Q1-Q4 (с 9-кратным отношением токов, раз уж всё равно надо подстраивать резисторы) является и первым каскадом усилителя ОС. Q6 и Q7 — обеспечивают запуск и формируют нагрузку для Q8. R4 и R5 — достаточны с допуском 5%. С погрешностью установки выходного напряжения от пропорциональных температуре базовых токов Q2 и Q4 борюсь очень грубой силой — увеличением тока делителя R6 и R7. Так и частотные характеристики несколько улучшаются, т.к. это нагрузка выходного каскада. L1, C4 и V2 — для анализа АФЧХ при разомнутой ОС по переменному току (задать L1 и C4 — по 1 Meg). C1, C2 и R3 формируют двухполюсную коррекцию АЧХ — в меру своего незнания пытаюсь расширить частотный диапазон, в котором доступно повышенное петлевое усиление. На LDO'шность прокачивать не стал, минимальное напряжение питания при симуляции — 4 В (вероятно — и от 3 В будет ещё прилично работать).

Для наглядности — всем 4 значениям R1 сопоставлены подходящие к заданному выходному напряжению значения R6. Поэтому кривые Vout расположены не так, как на рисунке № 2. При выбранном R2 = 1 кОм, минимальный ТКН (3,237 мВ в абсолютном выражении, 26,324 ppm/°C) получается при R1 = 443 Ом. Расчёт Vptat / T = 4 * (k/q) * ln(9) * (R2/R1) даёт 1,71 мВ/°C (4 это 1 плюс отношение тока эмиттера Q4 к току R1), а по результатам симуляции — 1,76 мВ/°C.

Рисунок № 9.

Рисунок № 10 — АФЧХ.

Вариации выходного напряжения:

- 124 мкВ на 9 В увеличения напряжения питания. Все транзисторы задатчика опорного напряжения и усилительные — работают при достаточно фиксированных напряжениях коллектор-база. Остаётся, разве что, закаскодить токовое зеркало Q6-Q7 и заменить R4 источником тока. Или — заменить их всех n-канальным полевым транзистором с p-n-переходом?

Рисунок № 11

- 54 мкВ на 10 мА тока нагрузки. Выходное сопротивление на постоянном токе — около 5,4 мОм;

Рисунок № 12

- 20-25 мВ импульсы при набросе и сбросе 5 мА нагрузки за 10 нс, возможно, великоваты? Тогда можно подкорректировать ESR и ёмкость C3, максимальный выходной ток Q9 (сопротивлениями R4, R6 и R7) и параметры C1-C2-R3.

Рисунок № 13

А зачем пытаться съэкономить пятый транзистор сборки? Вот два варианта:

- Им можно организовать термостабилизацию кристалла этого набора транзисторов. Используя пятый транзистор как нагреватель кристалла — через сигнал Vptat вывести температуру на 85-90 °С (на 45-50 при использовании в лабораторных условиях) и забыть о температурной нестабильности. Но лучше не практиковать этот фокус со сборкой в пластике (или потом никогда не выключать подогрев). Или попробовать снять остаточную температурную погрешность и учитывать её программно.

Именно эта идея, замеченная летом в одной старой книге, — сподвигла меня поизучать вопрос bandgap'ов ещё раз. Ну и свободное время — пока переболел «нонешним моровым поветрием». - С его помощью можно сделать коррекцию остаточного ТКН.

В заключение — закидываю и этот ИОН в «суровый прод». Расчет худших случаев и определение требуемых пределов подстройки сопротивления R1 (выгрузка результата «worst cases» в табличный процессор, определение худших run's по минимальному и максимальному среднему напряжению, подбор R1 для найденных run's):

- разброс от транзистора Q5 (а значит — и всего после него) практически не влияет на номинал и ТКН (менее 100 мкВ на Vout). Поэтому, исключаю его из финальных расчётов — задаю run от -1 (номинал) до 1023 (перебор по первым 10 параметрам);

Рисунок № 14

- требуемый диапазон подстройки — от 366 до 534 Ом (168 Ом).

Рисунок № 15

Разбив R1 на 5 резисторов, например — 11,3+22,6+45,3+90,9+365 Ом по ряду E96, можно перекрыть весь диапазон с разрешением 4 бита (16 равноотстоящих промежуточных значений). Также можно изменить значения с учётом имеющегося сдвига 11,3+22,6+45,3+365 > 443 (ном.) и/или скорректировать веса принимая нормальное распределение погрешностей.

Вывод. К #импортозамещение — готов? ;-)

Литература, в порядке использования:

[1] Книга Hans Camenzind, «Designing analog chips»

[2] Печатная лекция A. Paul Brokaw, «How to make a bandgap voltage reference in one easy lesson»

[3] Пара избранных заметок Robert A. Pease, «The Design of Band-Gap Reference Circuits: Trials and Tribulations» и «What's All This VBE Stuff, Anyhow?»

Более-менее полное ПСС Боба — смотрите тут. В заметке «How To Make Your Own Matched Transistors» Вы можете найти базовую идею схемы для подбора парных транзисторов при необходимости и упоминание о том, что, как правило, сборки 3046 согласованы лучше, чем на 1 мВ.

И — ещё одно его фото в царском костюме, с пригоршней ИМС в ладонях:

[4] Или — попробуйте найти [3] в испохабленном «грязными ковбоями» виде на сайте www.ti.com или на их форуме e2e.ti.com

Synopsys: Simulating Brokaw bandgap reference in LTSPICE, BJT DC parameters variation in LTSPICE.

Только зарегистрированные пользователи могут участвовать в опросе. Войдите, пожалуйста.

Редактор текстов Хабра

75%Вернуться к старому редактору!60

45%Запретить новый редактор ;-)36

20%Может и новый «допилят»?16

2.5%Только новый редактор!2

Проголосовали 80 пользователей. Воздержался 51 пользователь.