Вступление

Компания Megawin Technology Co., Ltd. была основана в Тайване в 1999 году. Первые разработки компании были в области создания встроенной flash-памяти и контроллеров ввода-вывода. С 2004 г. было запущено массовое производство 8-битных микроконтроллеров (МК). На российском рынке компания известна прежде всего своими МК серий MG82 и MG84 на ядре 80C51.

Однако сегодня наш интерес привлекли 32-разрядные микроконтроллеры Megawin Technology серии MG32F02 на базе ядра Cortex-M0, которые компания с 2019 г. массово производит и поставляет в Россию. Отличное соотношение цены и качества, богатый набор встроенных периферийных модулей делают эти микроконтроллеры серьезным конкурентом в своем классе аналогичным чипам таких мировых брендов как Microchip, STM32, NXP и пр. Особенно актуальными микроконтроллеры становятся сегодня в условиях беспрецедентных экономических санкций и фактического прекращения поставок большинства западных электронных компонентов.

Этой статьей на хабре мы открываем цикл публикаций, в котором постараемся всесторонне рассмотреть все возможности микроконтроллеров Megawin серии MG32F02. Глубоких знаний по архитектуре ARM или большого опыта разработки на Cortex-M от читателя не потребуется. В то же время предлагаемый материал будет интересен разработчикам устройств на 8-разрядных ядрах 80C51 или AVR, планирующим переход на 32-разрядные системы, где любой МК на ядре Cortex-M0 — первый кандидат на замещение 8-разрядных МК.

В первой статье цикла мы сделаем функциональный обзор микроконтроллеров серии MG32F02, рассмотрим общую структуру МК, центральный процессорный модуль, адресное пространство, подсистемы питания, сброса, тактирования и прерываний. В последующих публикациях будут рассмотрены:

разработка на основе gcc на Linux или Windows;

инструменты разработки и прошивки от производителя (программатор-отладчик MLink и среда Keil µVision IDE);

алгоритм программирования flash-памяти;

отладка кода в ОЗУ без записи и стирания flash-памяти;

периферийные устройства: GPIO, АЦП, ЦАП, компараторы, таймеры;

интерфейсы UART, I2C, SPI;

применение DMA;

аппаратная логика модуля General Purpose Logic для расчета CRC8/16/32, манипуляции битами;

конфигурируемая логика модуля Configurable Custom Logic

и многое другое.

Документация

На момент написания данной статьи какой-либо русскоязычной документации или обсуждений МК серии MG32F02 в рунете обнаружено не было. То же самое можно сказать и про информацию на английском. Основным и практически единственным источником информации остается официальная документация от Megawin Technology, доступная на китайском и английском языках. Для освоения микроконтроллеров потребуются следующие PDF-документы:

Datasheet на конкретный тип МК — общее описание возможностей МК и цоколевка (можно скачать из раздела Documents для конкретного типа МК),

User_Guide – полное описание всех МК семейства, версия на момент публикации статьи — 4.1.1 (доступен по этой ссылке),

Registers на конкретный тип МК — полный справочник по регистрам периферии (входит в общий архив User_Guide).

В связи с отсутствием русскоязычной литературы, в цикле публикаций будет приводиться необходимая техническая информация, основанная на User Guide и даташитах, а также на описаниях регистров.

Состав серии MG32F02

Серия MG32F02 включает линейку МК общего назначения MG32F02Axxx и линейку МК с USB-интерфейсом MG32F02Uxxx. Размер flash-памяти в зависимости от типа МК варьируется в пределах от 32 до 128 кбайт, размер ОЗУ — от 4 до 16 кбайт. Минимальное число выводов составляет 20 (корпус TSSOP20), максимальное — 80 (корпус LQFP80).

Максимальная тактовая частота всех МК серии MG32F02 составляет 48 МГц, что является практически типовым значением для большинства реализаций ядер Cortex-M0 и Cortex-M0+. Нельзя сказать что это много, но в то же время МК на ядре Cortex-M0(+) призваны прежде всего заменить 8-ми и 16-ти разрядные микроконтроллеры в новых разработках, и, конечно, не могут конкурировать, например, с топовыми кортексами M4-M7 линейки High Performance STM32. Однако МК от Megawin, например, могут стать достойной заменой контроллерам серий SAMD09/10/11/20/21 от Microchip, LPC800 от NXP.

МК серии MG32F02 имеют расширенный индустриальный диапазон температур эксплуатации от -40 до +105 °C. Особенностью микросхем является также широкий диапазон напряжений питания от 1,8 до 5,5 В, что сегодня встречается редко у 32-разрядных контроллеров.

На данный момент серия включает следующие типы микроконтроллеров:

MG32F02A032 — младшая модель с минимальными возможностями и числом выводов,

MG32F02A064 и MG32F02A128 — МК с максимальными функциональными возможностями,

MG32F02U064 и MG32F02U128 — аналогичные линейке MG32F02Axxx микроконтроллеры с интерфейсом USB, имеют дополнительное ОЗУ объемом 512 байт для буферов USB.

Следует также упомянуть МК MG32F02A072, MG32F02A132 и MG32F02V032, которые сняты с производства, однако описываются в общем руководстве User Guide. Данные типы МК в статье рассматриваться не будут. Основные параметры и функциональные возможности серии MG32F02 приведены в таблице.

Параметр или функциональный блок | MG32F02A032 | MG32F02A064/U064 | MG32F02A128/U128 |

|---|---|---|---|

Объем Flash | 32 кбайт | 64 кбайт | 128 кбайт |

Объем ОЗУ | 4 кбайт | 8/16 кбайт | 16/16 кбайт |

Корпус | TSSOP20, QFN32, LQFP48 | LQFP64/48 | LQFP80/64 |

Число контактов ввода-вывода | 17, 29, 44 | 59/44 | 73/59 |

Максимальное число линий внешнего прерывания | 17, 29, 44 | 59/44 | 73/59 |

Детектор снижения напряжения | LVR+BOD0/1 | LVR+BOD0/1/2 | LVR+BOD0/1/2 |

Таймеры 16 бит | 2 (TM00,TM01) | 2 (TM00,TM01) | 2 (TM00,TM01) |

Таймеры 32 бита | 3 (TM10,TM16, TM36) | 5 (TM10,TM16,TM20,TM26,TM36) | 5 (TM10,TM16,TM20,TM26,TM36) |

Число каналов захвата/сравнения/ШИМ | 4 16-разрядных или 8 8-разрядных | 8 16-разрядных или 16 8-разрядных | 8 16-разрядных или 16 8-разрядных |

Число комплементарных ШИМ-каналов | 3 | 7 | 7 |

Счетчик повторений | - | 8 бит | 8 бит |

АЦП | 12 бит, 12 каналов, 800 кс/с | 12 бит, 16 каналов, до 1,5 Мс/с | 12 бит, 16 каналов, до 1,5 Мс/с |

ЦАП | - | 12 бит, 1 канал, 1 Мс/с | 12 бит, 1 канал, 1 Мс/с |

Модуль UART | 2 расширенных (URT0,URT1) | 3 расширенных (URT0-URT2), 4 базовых (URT4-URT7) | 3 расширенных (URT0-URT2), 4 базовых (URT4-URT7) |

Модуль SPI (master/slave) | 1 | 1 | 1 |

Модуль I2C | 1 | 2 | 2 |

Контроллер внешней памяти EMB | - | шина 16/8 бит | шина 16/8 бит |

Число каналов DMA | 1 | 5 | 5 |

32-битный аппаратный делитель | нет | есть | есть |

Модуль конфигурируемой логики CCL | - | 2 | 2 |

Детектор последовательностей SDT | - | 1 | 1 |

Все микроконтроллеры также включают следующие модули:

независимый сторожевой таймер IWDT;

оконный сторожевой таймер WWDT;

32-разрядные часы реального времени RTC;

два независимых скоростных аналоговых компаратора со встроенным 6-разрядным ЦАП для задания пороговых значений;

модуль вычисления CRC типа CRC8/CRC16/CCITT16/CRC32 с фиксированным полиномом;

два модуля прерывания и модуляции сигналов OBM.

Также стоит отметить, что таймеры TM26 и TM36 включают интерфейс квадратурного энкодера.

Структурная схема микроконтроллера

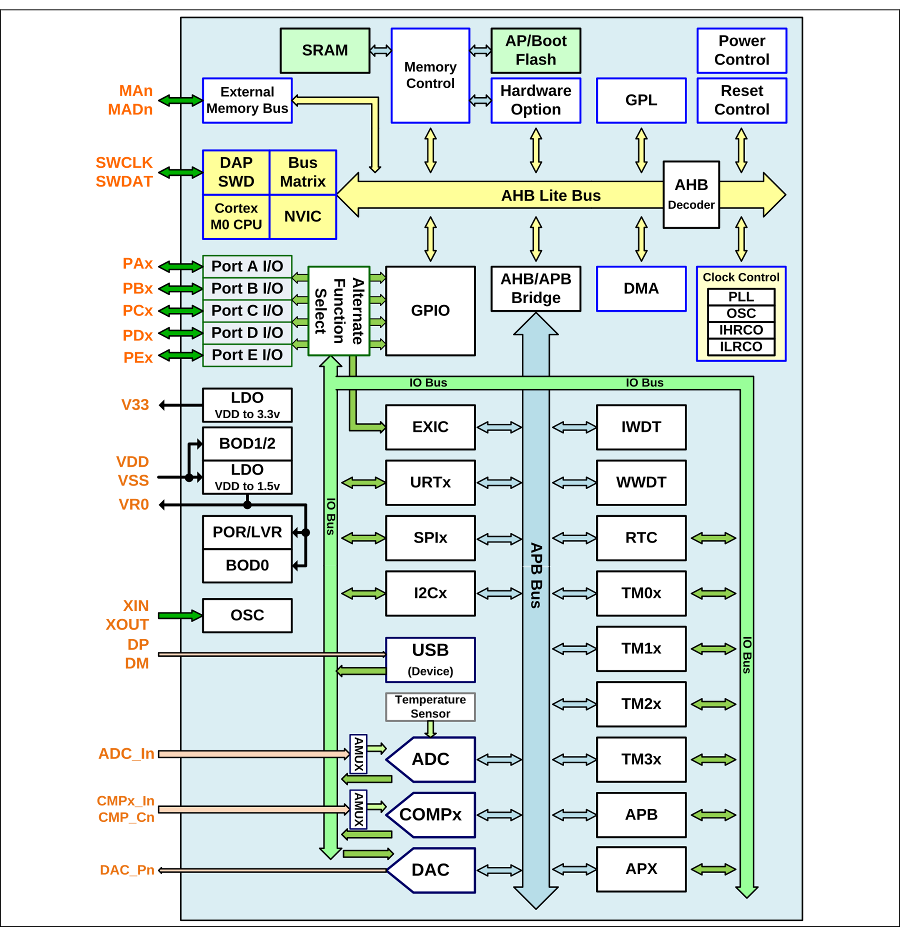

На следующем рисунке представлена структурная схема микроконтроллеров MG32F02A128/U128/A064/U064.

Центральный процессорный модуль включает:

центральное процессорное устройство (ЦПУ) Cortex-M0

CPUс поддержкой умножения целых чисел,контроллер вложенных (приоритетных) векторных прерываний

NVIC(Nested Vectored Interrupt Controller) с поддержкой 32-х внешних прерываний с четырьмя уровнями приоритета,24-разрядный системный таймер (System Tick Timer),

блок отладки и программирования DAP SWD (Debug Access Port for Serial Wire Debug) с двумя точками наблюдения и четырьмя точками остановки,

мультиплексор-коммутатор BusMatrix высокопроизводительной шины

AHB(Advanced High-Performance Bus).

К шине AHB подключены следующие узлы:

контроллер внешней памяти

EMB(External Memory Bus), позволяющий подключать к МК микросхемы статической оперативной или постоянной памяти типа NOR/NAND flash, а также ЖКИ с интерфейсом 8080;контроллер встроенной памяти Memory Control, взаимодействующий со статической оперативной памятью SRAM, flash-памятью, включая отдельную область системной конфигурации Hardware Option (префикс названий регистров контроллера —

MEM);блок логики для специальных побитовых манипуляций и вычисления CRC

GPL(General Purpose Logic);подсистема управления питанием Power Control (префикс названий регистров модуля —

PW);подсистема управления сбросом МК Reset Control (префикс названий регистров модуля —

RST);подсистема тактирования Clock Control (префикс названий регистров —

CSC(Clock Source Controller));контроллер прямого доступа к памяти

DMA(Direct Memory Access);модуль

GPIO(General Purpose IO), позволяющий программно управлять произвольными выводами портов Port A - Port E;блок выбора альтернативных функций выводов микроконтроллера

AFS(Alternate Function Select), связанный с GPIO;мост AHB/APB Bridge для связи шины AHB c шиной периферийных устройств

APB(Advanced Peripheral Bus).

К шине APB подключены следующие узлы:

контроллер внешних прерываний

EXIC(External Interrupt Controller), позволяющий использовать произвольные выводы МК для сигналов внешний прерываний;независимый сторожевой таймер

IWDT(Independent WatchDog Timer);оконный сторожевой таймер

WWDT(Window WatchDog Timer);32-разрядные часы реального времени

RTC(Real Time Clock);таймеры TM0x-TM3x;

последовательные интерфейсы: асинхронные

URTx, трехпроводныеSPIxи двухпроводныеI2Cx(x— номер интерфейса);интерфейс

USB(для линейки MG32F02Uxxx);аналого-цифровой преобразователь

ADCс температурным сенсором;аналоговые компараторы COMPx (префикс названий регистров —

CMP);цифро-аналоговый преобразователь

DAC;дополнительные функциональные модули (на схеме обозначены как

APX): модули конфигурируемой логикиCCL(Configurable Custom Logic), двухвходовый модуль выделения последовательностейSDT(Sequential State Detector), интерфейс управления адресуемыми RGB-светодиодамиASB(ARGB Serial Bus).

В микроконтроллерах также имеются следующие узлы:

генератор с внешним резонатором

OSC;LDO-регулятор напряжения для питания внутренней логики МК на 1,5 В (1,8 В для MG32F02A032);

детекторы снижения напряжения питания

BOD0,BOD1иBOD2.

Микроконтроллер MG32F02A032 отличается отсутствием следующих блоков:

контроллер подключения внешней памяти (External Memory Bus, EMB),

порт E (Port E),

цифро-аналоговый преобразователь (DAC),

устройства шины APX,

таймеры T2x, T3x,

температурный сенсор в модуле АЦП,

дополнительные функциональные модули

APX.

Центральный процессорный модуль

На следующем рисунке представлена структура центрального процессорного модуля микроконтроллеров серии MG32F02.

Ядро Cortex-M0 представляет собой архитектуру ARMv6-M, включающую только набор инструкций Thumb. Коды всех инструкций Thumb имеют длину 16 бит, при этом позволяют оперировать 32-битными данными и использовать все доступные 32-разрядные регистры ядра ARM. В принципе, размер инструкций сокращен с 32 до 16 бит за счёт:

исключения возможности непосредственного использования старшей половины регистров R8-R15 в большинстве арифметических и логических операций (номер регистра кодируется в этих инструкциях тремя битами), но они остаются доступны в операциях пересылки,

исключения машинных инструкций с тремя регистрами.

Отметим, что ядро Cortex-M0 не включает блок защиты памяти MPU (Memory Protection Unit).

Ядро имеет аппаратную поддержку умножения целых 32-разрядных чисел за один машинный цикл (инструкция MUL). Аппаратная возможность деления целых 32-разрядных чисел предоставляется в МК через отдельный периферийный блок Divider в модуле GPL (кроме MG32F02A032). Операции с вещественными числами аппаратно не поддерживаются.

Более подробно о ядре Cortex-M0 можно почерпнуть информацию из книги Джозефа Ю

"The Definitive Guide to ARM ® Cortex ® -M0 and Cortex-M0+ Processors. Second Edition", а также из официальной документации ARM:

"Пробуждение" ядра по какому-либо прерыванию и выход из спящего режима осуществляется контроллером пробуждения WIC (Wake-up Interrupt Controller), который всегда находится во включенном состоянии.

Режим отладки МК через интерфейс SWD реализован через блок отладки DAP согласно спецификации ARM Cortex-M0. Таким образом, для отладки данных МК может применяться любой SWD-совместимый программатор или отладчик и стандартное ПО.

Более подробно функционирование процессорного модуля будет рассматриваться по ходу изложения материала.

Организация адресного пространства

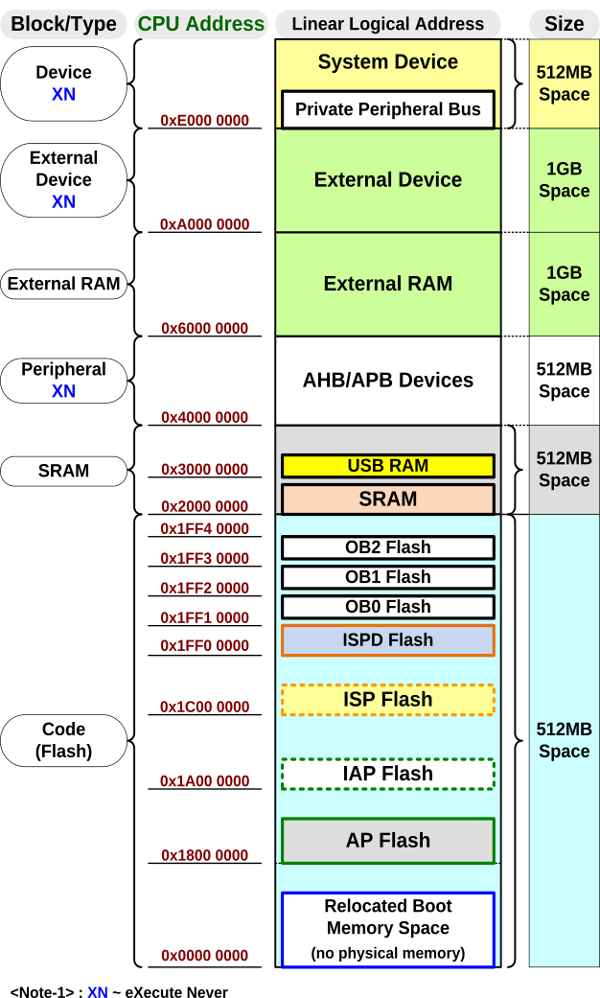

На следующем рисунке представлена организация адресного пространства микроконтроллеров серии MG32F02.

Первые 132 кбайт адресного пространства (адреса 0x00000000-0x00020FFF) жестко не привязаны к какой-либо физической памяти. В зависимости от значения поля BOOT_MS конфигурационных ячеек OB0 (см. ниже) эта область отображается во flash-память или в SRAM. В любом случае первые 192 байта этой области должны содержать таблицу векторов прерываний (48 слов по 4 байта), начальный адрес которой не может быть изменен в архитектуре Cortex-M0.

Физическая flash-память адресуется в пределах первых 512 Мбайт адресного пространства (адреса 0x180000000-0x1FFFFFFF). Вся flash-память логически разделена на следующие секции:

основной машинный код программы МК AP (Application Program) (начальный адрес 0x18000000),

область хранения постоянных данных основной программы IAP (In-Application-Programming data) (начальный адрес 0x1A000000),

машинный код программного загрузчика ISP (In-System-Program), другими словами, область бутлоадера (начальный адрес 0x1C000000),

область хранения постоянных данных загрузчика ISPD (In-System-Programming data) (начальный адрес 0x1FF00000),

системные конфигурационные ячейки OB0-0B2 (hardware Option Byte) — области памяти по 32 байта.

Области AP, IAP и ISP разделяют основное пространство flash-памяти. В это пространство не входят области ISPD и OBx. Настройка областей выполняется путем изменения системных конфигурационных ячеек OB0. Размер секции IAP задается в поле IAP_SIZE, размер секции ISP — в поле ISP_SIZE ячеек OB0 в единицах по 1024 байт для MG32F02A032 и в единицах по 512 байт для остальных МК.

По-умолчанию, область IAP не выделяется, а для ISP выделяется 2 кбайт. Соответственно доступная область AP уменьшается на это значение. Размер страницы flash-памяти составляет 1 кбайт для MG32F02A032 и 512 байт для остальных МК. Ячейки памяти OBx могут быть изменены только с помощью внешнего программатора.

Для встроенной оперативной памяти SRAM отводится 512 Мбайт адресного пространства, начиная с адреса 0x20000000. Для внешней оперативной памяти (RAM) отводится пространство размером 1 Гбайт, начиная с адреса 0x60000000.

Все регистры периферийных модулей шин AHB и APB расположены в области размером 512 Мбайт начиная с адреса 0x40000000. Конкретные базовые адреса модулей и смещения для регистров можно найти в официальном документе Registers по конкретному типу МК.

Область памяти размером 1 Гбайт начиная с адреса 0xA0000000 зарезервирована для внешних периферийных устройств.

Самая верхняя область, начиная с адреса 0xE0000000, предназначена для системных регистров ядра Cortex-M0, имеющих в названии префикс CPU.

Все области памяти, за исключением тех, которые помечены XN, могут использоваться для исполнения машинного кода. Таким образом, можно запускать программы из ОЗУ (встроенного или внешнего), что удобно для отладки небольших фрагментов кода, поскольку загрузка данных в ОЗУ выполняется через интерфейс SWD значительно быстрее, чем программирование flash-памяти, и при этом не расходуется её ресурс.

За большинство функций управления памятью отвечает контроллер памяти Internal Memory Controller (префикс названий регистров — MEM). Например, настройками его регистров определяется возможность исполнения кода или возможность записи в той или иной области flash-памяти. Для стирания или записи flash-памяти используется определенная последовательность действий по модификации управляющих регистров группы MEM.

Питание МК

Все микроконтроллеры требуют один источник питания напряжением от 1,8 В до 5,5 В. Для питания внутренней логики на кристалле имеется встроенный LDO-регулятор напряжения на 1,8 В для MG32F02A032 и 1,5 В — для остальных МК. Для нормальной работы LDO-регулятора требуется подключение к его выходу (вывод VR0 МК) параллельно двух внешних конденсаторов: электролитического и керамического емкостью 4,7 мкФ и 0,1 мкФ соответственно. В версиях МК с USB имеется еще один LDO-регулятор с выходным напряжением 3,3 В, к которому также требуется подключение конденсатора 4,7 мкФ (вывод V33).

Все МК имеют три основных режима работы:

основной режим работы ON,

спящий режим SLEEP,

режим остановки STOP.

Поддерживается режим "пробуждения" от следующих источников: выводы GPIO, сторожевой таймер IWDT, часы RTC, аналоговый компаратор, модуль I2C, модули BODx, а также от модуля USB.

Для перевода МК в режимы SLEEP или STOP используются машинные инструкции WFE (ожидать прерывания или события) или WFI (ожидать прерывания). В зависимости от значения поля SLEEPDEEP регистра CPU_SCR МК переходит в тот или иной режим энергосбережения согласно таблице.

Режим МК | Режим ЦПУ | Значение | Описание |

|---|---|---|---|

ON | run | x | Нормальный режим работы |

SLEEP | sleep | 0 | ЦПУ в спящем режиме, остальные модули работают согласно настройкам |

STOP | deep sleep | 1 | все модули отключены, за исключением IWDT, RTC, и CMP |

Условия "пробуждения" зависят от машинной инструкции и приведены в таблице. В любом случае должны быть разрешены прерывания.

Инструкция | Условие пробуждения |

|---|---|

WFE | Внешнее прерывание, прерывание отладки, сброс ЦПУ в спящем режиме, произошло событие до обработки инструкции WFE. |

WFI | Внешнее прерывание, прерывание отладки, сброс ЦПУ в спящем режиме. |

Возможность работы какого-либо встроенного периферийного модуля в режиме SLEEP определяется разрешением его тактирования в этом режиме (см. ниже).

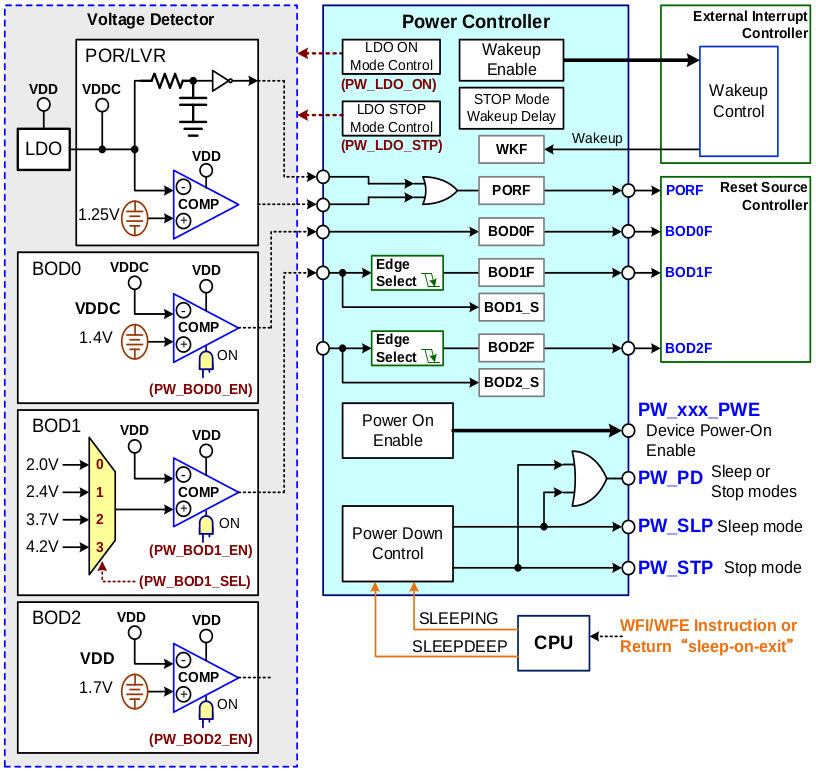

На следующем рисунке представлена функциональная схема контроллера питания.

Контроль напряжения питания внутренней логики VDDC (на выходе основного LDO) выполняют блоки POR (Power-On Reset) и LVR (Low-Voltage Reset), управляя сбросом МК при включении питания и снижении напряжения питания соответственно.

В МК присутствуют также детекторы снижения напряжения BOD0, BOD1 и BOD2 (Brown-Out Detector) (последнего нет в MG32F02A032), активизируемые независимо друг от друга установкой полей PW_BODx_EN в регистре PW_CR0. Блок BOD0 предназначен для контроля напряжения питания flash-памяти и имеет фиксированный порог 1,7 В для MG32F02A032 и 1,4 В для остальных МК. Блок BOD1 предназначен для общего контроля напряжения и имеет настраиваемый порог из ряда 2,0; 2,4; 3,7 и 4,2 В. Блок BOD2 аналогичен предыдущему блоку, но имеет фиксированный порог 1,7 В. Блоки BOD1 и BOD2 могут быть настроены на генерацию события по спаду, по нарастанию или по обоим фронтам. Каждый из блоков устанавливает соответствующие статусы событий в полях PW_PORF, PW_BODxF и PW_BODxS в регистре статуса PW_STA. Каждый из блоков может быть настроен в качестве источника сброса (см. далее).

Возможность пробуждения МК из режима STOP при наступлении событий в периферийных модулях определяется соответствующими битами регистров PW_WKSTP0 и PW_WKSTP1.

Контроллер питания может вырабатывать сигнал прерывания INT_PW в случае срабатывания одного из блоков BOD0-BOD2, а также в случае появления события пробуждения от контроллера WIC. Разрешение прерывания по каждому из событий задается соответствующими битами регистра PW_INT.

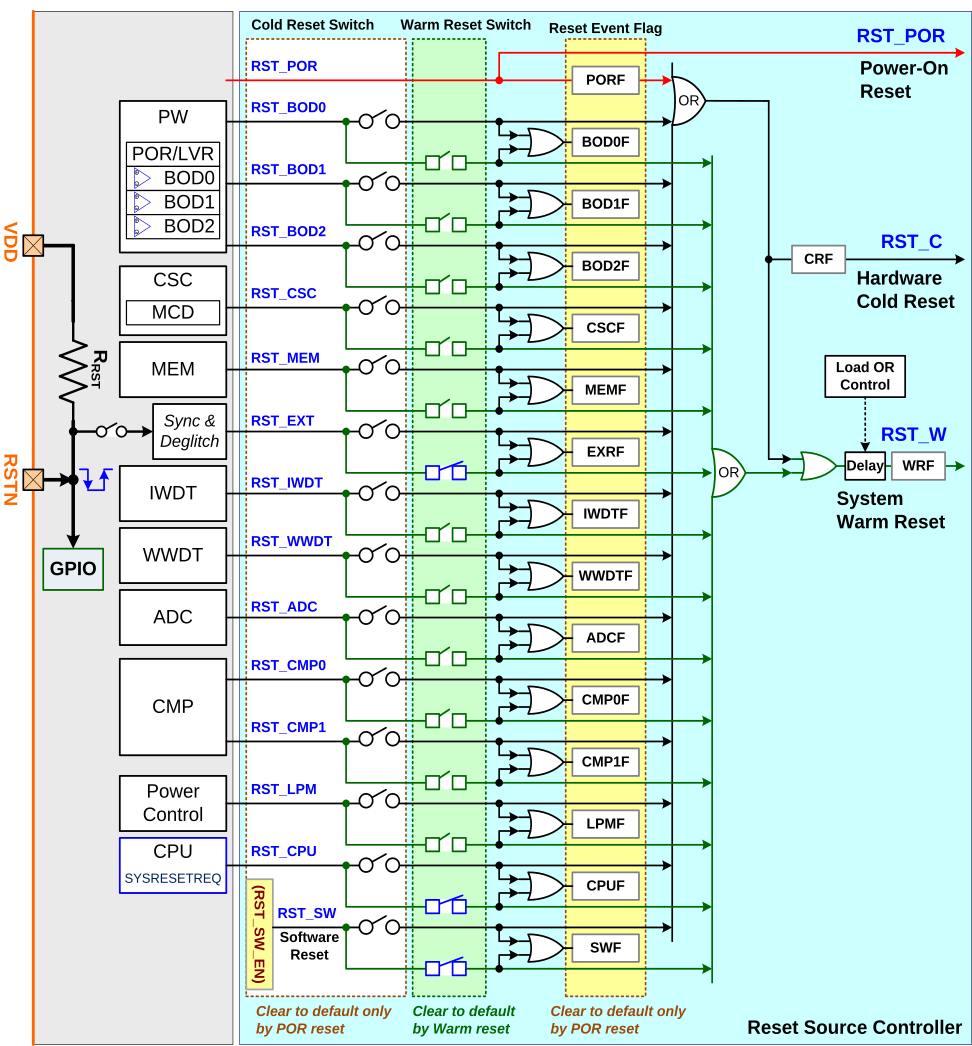

Подсистема сброса

В МК за сброс отвечает отдельный модуль Reset Source Controller, работающий совместно с контроллером питания и подсистемой тактирования.

Различают сброс отдельных периферийных модулей или же сброс МК в целом.

На следующем рисунке показана функциональная схема подсистемы сброса МК MG32F02A128/U128/A064/U064.

Имеются следующие ситуации сброса МК:

сброс при включении питания POR (Power-On Reset), имеет максимальный приоритет;

"холодный" сброс (Cold Reset), имеет средний приоритет;

"горячий" сброс (Warm Reset), имеет низший приоритет.

POR-сброс приводит к генерации "холодного" сброса, который, в свою очередь, вызывает "горячий" сброс. Таким образом, "горячий" сброс выполняется в любом случае.

POR-сброс возникает при включении МК после достижения необходимого уровня напряжения питания.

"Холодный" сброс происходит при возникновении событий в модулях BODx, сторожевых таймерах IWDR, WWDT, и другой периферии, если имеются соответствующие настройки. "Холодный" сброс вызывает считывание конфигурационных ячеек OBx и загрузку их значений в регистры аппаратной конфигурации CFG_ORx (Option Register), а также блокирует запись в регистры настройки периферии, которые требуют для своей модификации специальной разблокировки.

"Горячий" сброс вызывает сброс всех периферийных модулей, сброс всех флагов в регистрах их состояний, а также возвращает все их настройки в значения по-умолчанию.

Возможность "холодного" или "горячего" сброса от каждого из периферийных модулей определяется значениями соответствующих полей регистров RST_CE и RST_WE. Причину сброса при старте программы МК можно узнать через регистр статуса RST_STA. Тип сброса ("холодный" или "горячий") можно узнать через поля RST_CRF и RST_WRF.

Программно можно инициировать "горячий" сброс отдельного периферийного модуля путем установки соответствующего бита RST_XXX_EN в регистрах RST_AHB, RST_APB0 или RST_APB1 в зависимости от шины, на которой расположен модуль.

Подсистема тактирования

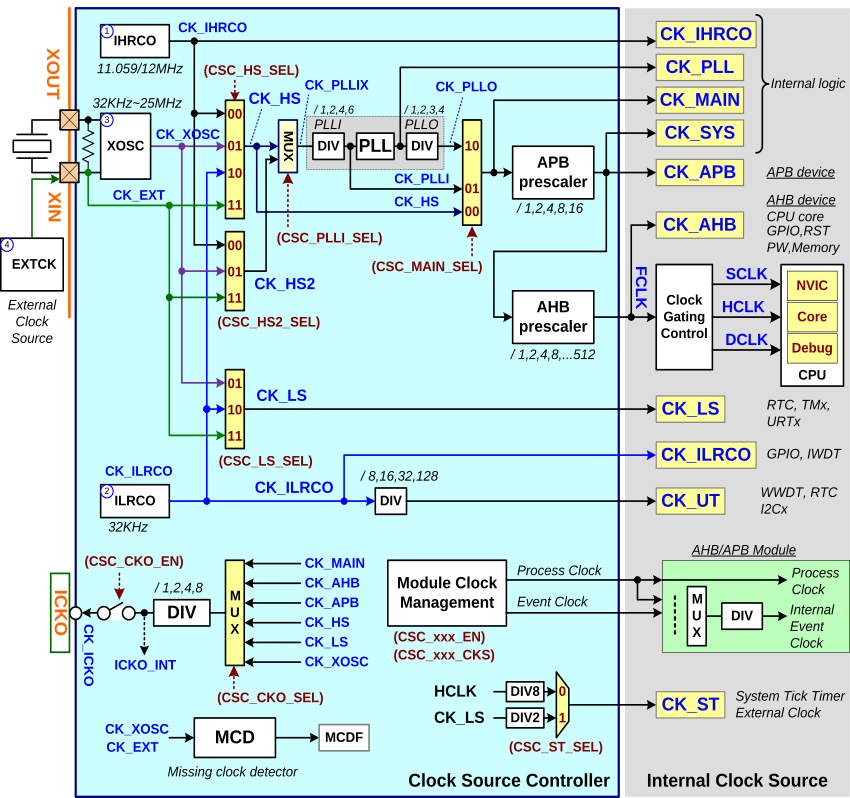

На следующем рисунке показана общая схема тактирования МК MG32F02A128/U128/A064/U064.

В МК для тактирования могут быть использованы следующие источники:

встроенный низкочастотный RC-генератор ILRCO (Internal Low-frequency RC Oscillator),

встроенный высокочастотный RC-генератор IHRCO (Internal High-frequency RC Oscillator),

встроенный кварцевый генератор XOSC,

вход для внешнего генератора EXTCK (External Input Clock).

Встроенный генератор ILRCO вырабатывает импульсы CK_ILRCO с частотой 32 кГц и может быть использован, например, для тактирования часов реального времени RTC, таймеров IWDT, WWDT, GPIO или интерфейса I2C. Заявленная в Datasheet точность генератора составляет 4 % при температуре +25 °C.

Встроенный генератор IHRCO в зависимости от значения поля CSC_IHRCO_SEL регистра CSC_CR0 может генерировать импульсы CK_IHRCO частотой 12,0000 МГц или 11,0592 МГц. Выбор частоты 11,0592 МГц удобен при использовании модуля UART, когда нужно получить точные стандартные значения скорости обмена данными 115200 бод или ниже (коэффициент деления 96). При включении питания по-умолчанию тактирование МК осуществляется от данного генератора с частотой 12,0000 МГц. Заявленная точность генератора составляет 1 % при температуре +25 °C, а ток потребления — 350 мкА.

Встроенный кварцевый генератор XOSC может работать на низкой частоте 32 кГц (удобно для подключения часового кварцевого резонатора номиналом 32768 Гц), либо на высокой частоте от 4 до 25 МГц. Резонатор подключается к выводам XIN (PC13) и XOUT (PC14) порта C, отдельных выводов для резонатора в МК не предусмотрено. Кварцевый генератор формирует сигнал CK_XOSC.

Внешний тактовый вход EXTCK допускает подключение генератора частотой до 36 МГц (используется вывод XIN), который формирует сигнал CK_EXT.

Любой из указанных четырех источников с помощью мультиплексора может быть использован для получения сигнала CK_HS (High Speed clock), который используется для последующего формирования сигналов тактирования различных узлов. Активный вход мультиплексора определяется значением поля CSC_HS_SEL регистра управления тактированием CSC_CR0. При "горячем" сбросе МК это значение может соответствовать либо CK_IHRCO, либо CK_ILRCO и считывается из поля CFG_HS_SEL регистра CFG_OR05, в который оно загружается из ячеек аппаратной конфигурации OB0.

Сигнал CK_HS подается далее на вход блока умножения частоты на основе ФАПЧ PLL (Phase-Locked Loop). В МК MG32F02A032 сигнал подается напрямую, в остальных МК — через дополнительный мультиплексор (сигнал CK_PLLIX).

Параллельно с CK_HS формируется также сигнал CK_HS2 (кроме MG32F02A032) из одного из высокочастотных источников, задаваемых полем CSC_HS2_SEL регистра CSC_CR0. Сигнал может использоваться для модуля USB.

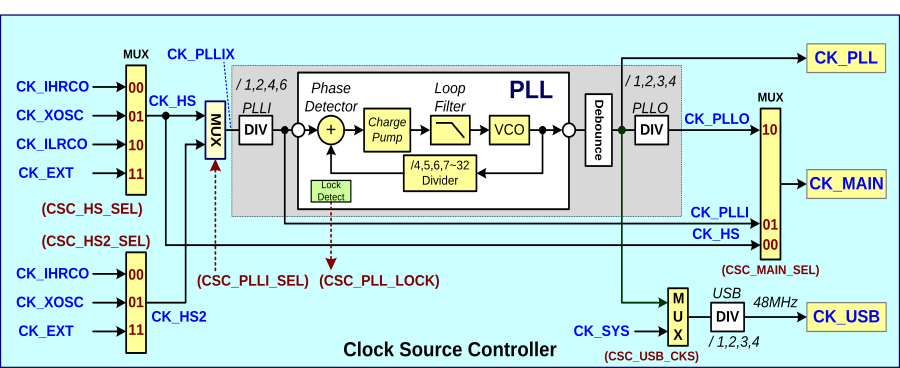

На следующем рисунке показана функциональная схема блока PLL МК MG32F02A128/U128/A064/U064.

Блок PLL включается путем установки бита CSC_PLL_EN регистра CSC_CR0. Частота входного сигнала для блока PLL должна быть в пределах 5-7 МГц для MG32F02A032 и в пределах 4-8 МГц для остальных МК. Если входная частота сигнала CK_HS (CK_HS2) выше указанных допустимых значений, необходимо задействовать входной делитель PLLI

и задать коэффициент деления из множества 1, 2, 4 и 6 в поле CSC_PLLI_DIV регистра CSC_DIV.

В МК реализовано два типа умножения частоты. Настройка блока PLL осуществляется через регистр CSC_PLL. Если значение бита CSC_PLL_MDS регистра равно 0, блок может умножать частоту в 16 или 24 раза согласно установкам в поле CSC_PLL_MUL.

Если значение бита CSC_PLL_MDS регистра равно 1, блок может умножать частоту с коэффициентом в диапазоне 4-32 согласно установкам в поле CSC_PLL_MULX. В этом случае частота выходного сигнала CK_PLL будет определяться выражением

F(CK_PLL) = F(CK_PLLI) * (CSC_PLL_MULX + 1)

Частота сигнала CK_PLL может достигать 144 МГц для MG32F02A032 и 180 МГц для остальных МК. Сигнал CK_PLL также подается на выходной делитель PLLO, выходной сигнал которого CK_PLLO вместе с сигналами CK_PLLI и CK_HS подается на следующий мультиплексор, формирующий конечный тактовый сигнал CK_MAIN. Коэффициент делителя PLLO может быть равным 1, 2, 3 или 4 и задается в поле CSC_PLLO_DIV регистра CSC_DIV. Активный вход мультиплексора определяется значением поля CSC_MAIN_SEL регистра CSC_CR0.

Основной тактовый сигнал CK_MAIN подается далее на предделитель APB Prescaler для формирования тактового сигнала CK_APB шины APB (а также системного сигнала CK_SYS). Коэффициент деления предделителя может принимать значения 1, 2, 4, 8 или 16 и определяется полем CSC_APB_DIV регистра CSC_DIV.

Тактовый сигнал CK_AHB шины AHB получается делением частоты сигнала CK_APB предделителем AHB Prescaler. Коэффициент деления предделителя может принимать значения 1, 2, 4, ..., 512 и определяется полем CSC_AHB_DIV регистра CSC_DIV.

Сигналы CK_IHRCO, CK_PLL, CK_MAIN и CK_SYS используются во внутренней логике МК. Сигнал CK_AHB используется для тактирования центрального процессорного модуля, включая ЦПУ, NVIC, блок отладки DAP SWD, контроллера питания, памяти.

Сигналы CK_ILRCO, CK_XOSC и CK_EXT подаются на мультиплексор для формирования низкочастотного сигнала тактирования CK_LS (Low Speed clock). Активный вход данного мультиплексора определяется значением поля CSC_LS_SEL регистра CSC_CR0. Сигнал CL_LS может использоваться для тактирования модуля RTC, таймеров TMx, последовательных асинхронных интерфейсов URTx.

Сигнал CK_ILRCO, проходя через дополнительный делитель частоты, формирует еще один тактирующий сигнал CK_UT, предназначенный для модулей WWDT, RTC, I2Cx. Коэффициент деления может принимать значения 8, 16, 32 или 128 и задается полем CSC_UT_DIV регистра CSC_DIV.

Сигнал тактирования CK_ST для стандартного 24-разрядного системного таймера процессорного модуля System Tick Timer формируется либо из тактового сигнала ЦПУ HCLK путем деления частоты на 8, либо из сигнала CK_LS с делением частоты на 2. Источник сигнала CK_ST определяется битом CSC_ST_SEL регистра CSC_CR0.

В МК имеется возможность вывода некоторых сигналов тактирования на внешний вывод МК ICKO, соответствующий выводу PC0 (без альтернативного варианта). Данный выходной сигнал CK_ICKO формируется на выходе делителя, на вход которого можно подключить следующие сигналы: CK_MAIN, CK_AHB, CK_APB, CK_HS, CK_LS, CK_XOSC. Выбор сигнала определяется значением поля CSC_CKO_SEL, а коэффициент деления (1, 2, 4 или 8) задается полем CSC_CKO_DIV регистра CSC_CKO. Разрешение коммутации сигнала на внешний вывод определяется битом CSC_CKO_EN.

Подсистема тактирования также включает детектор пропадания тактовых сигналов CK_XOSC и CK_EXT MCD (Missing Clock Detector). Детектор включен по-умолчанию и может быть отключен установкой бита CSC_MCD_DIS в регистре CSC_CR0. Интервал времени определения колебаний задается в поле CSC_MCD_SEL регистра CSC_CR0.

Регистр статуса CSC_STA подсистемы тактирования содержит поля, позволяющие определить статус первичных источников сигналов тактирования ("источник готов, частота стабильная"), а также состояния некоторых мультиплексоров, определяющих источники для вторичных сигналов.

Тактирование каждого встроенного периферийного модуля в режиме SLEEP может быть разрешено отдельно установкой соответствующих полей в регистрах CSC_SLP0 и CSC_SLP1.

Подсистема тактирования может вырабатывать сигнал прерывания INT_CSC при его разрешении в случае пропадания одного из используемых тактовых сигналов от источников XOSC, ILRCO, IHRCO, PLL. Разрешение прерывания от конкретных источников определяется соответствующими битами регистра CSC_INT.

Подсистема тактирования вырабатывает сигнал сброса RST_CSC в случае обнаружения пропадания сигналов CK_XOSC и CK_EXT детектором MCD.

Прерывания

Ядро Cortex-M0 включает развитую поддержку прерываний на основе контроллера вложенных (приоритетных) векторных прерываний NVIC. В архитектуре ARM прерывание является частным случаем исключения (exception). Исключения обрабатываются отдельными подпрограммами обработки, и, как правило, асинхронно по отношению к выполнению основной программы (задачи). Подпрограммы обработки часто именуются ISR (Interrupt Service Routine) или просто хендлерами (handler).

Каждая ISR имеет свой стартовый адрес, или вектор, который хранится в таблице векторов (прерываний). При наступлении исключения (прерывания) в регистр PC (Program Counter) загружается его вектор из таблицы, в результате чего управление передается ISR. В общее число поддерживаемых исключений входит 32 внешних прерывания от периферийных устройств IRQ#x (Interrupt Request). Каждое исключение имеет свой номер (от 1 до 47), который определяет смещение своего вектора в таблице векторов (в 32-битных словах). В следующей таблице приведены все поддерживаемые в МК исключения и прерывания.

Номер исключения | Название | Приоритет | Описание |

|---|---|---|---|

1 | Reset | -3 | Исключение "Сброс" |

2 | NMI | -2 | Немаскируемое прерывание (Non Maskable Interrupt) |

3 | HardFault | -1 | Аппаратное исключение, вызванное ошибкой в программе (неверный код инструкции, неверный адрес обращения и т.д.) |

4-10 | - | - | Зарезервированные номера |

11 | SVCall | настраиваемый | Системный вызов по машинной инструкции |

12-13 | - | - | Зарезервированные номера |

14 | PendSV | настраиваемый | Системный вызов с возможностью отложения |

15 | SysTick | настраиваемый | Прерывание таймера System Tick Timer |

16 | WWDT (IRQ#0) | настраиваемый | Прерывание от модуля WWDT |

17 | SYS (IRQ#1) | настраиваемый | Общесистемное прерывание |

18 | (IRQ#2) | - | Зарезервировано |

19 | EXINT0 (IRQ#3) | настраиваемый | Внешнее прерывание EXINT0 (порт PA) |

20 | EXINT1 (IRQ#4) | настраиваемый | Внешнее прерывание EXINT1 (порт PB) |

21 | EXINT2 (IRQ#5) | настраиваемый | Внешнее прерывание EXINT2 (порт PC) |

22 | EXINT3 (IRQ#6) | настраиваемый | Внешнее прерывание EXINT3/EXINT4 (порты PD/PE) |

23 | COMP (IRQ#7) | настраиваемый | Общее прерывание от аналогового компаратора |

24 | DMA (IRQ#8) | настраиваемый | Прерывание модуля DMA |

25 | (IRQ#9) | - | Зарезервировано |

26 | ADC (IRQ#10) | настраиваемый | Прерывание от АЦП |

27 | DAC (IRQ#11) | настраиваемый | Прерывание от ЦАП |

28 | TM0x (IRQ#12) | настраиваемый | Общее прерывание таймеров TM0x |

29 | TM10 (IRQ#13) | настраиваемый | Прерывание таймера TM10 |

30 | TM1x (IRQ#14) | настраиваемый | Общее прерывание таймеров TM1x |

31 | TM20 (IRQ#15) | настраиваемый | Прерывание таймера TM20 |

32 | TM2x (IRQ#16) | настраиваемый | Общее прерывание таймеров TM2x |

33 | TM3x (IRQ#17) | настраиваемый | Общее прерывание таймеров TM3x |

34 | (IRQ#18) | - | Зарезервировано |

35 | (IRQ#19) | - | Зарезервировано |

36 | URT0 (IRQ#20) | настраиваемый | Прерывание модуля URT0 |

37 | URT123 (IRQ#21) | настраиваемый | Общее прерывание модулей URT1, URT2, URT3 |

38 | URT4x (IRQ#22) | настраиваемый | Общее прерывание модулей URT4, URT5, URT6, URT7 |

39 | (IRQ#23) | - | Зарезервировано |

40 | SPI0 (IRQ#24) | настраиваемый | Прерывание модуля SPI0 |

41 | (IRQ#25) | - | Зарезервировано |

42 | (IRQ#26) | - | Зарезервировано |

43 | (IRQ#27) | - | Зарезервировано |

44 | I2C0 (IRQ#28) | настраиваемый | Прерывание модуля I2C0 |

45 | I2Cx (IRQ#29) | настраиваемый | Общее прерывание модулей I2Cx |

46 | USB (IRQ#30) | настраиваемый | Прерывание модуля USB |

47 | APX (IRQ#31) | настраиваемый | Прерывание дополнительных модулей APX |

Первое 32-битное слово в таблице векторов содержит начальное значение регистра указателя стека MSP (Main Stack Pointer) и не связано с исключением. Первые пятнадцать исключений 1-15 являются стандартными для ядра Cortex-M0. Исключения 16-47 соответствуют прерываниям IRQ#0-31 периферийных модулей и определяются в конкретной реализации МК. Все указанные исключения асинхронны, кроме HardFault (3) и SVCall (11).

Каждое исключение имеет свой приоритет (чем меньше число, тем выше приоритет). Исключения 1-3 имеют фиксированный приоритет, приоритет остальных исключений в любом случае будет ниже и выбирается еще из четырех уровней, поддерживаемых контроллером NVIC ядра Cortex-M0. Таким образом, всего получается семь уровней приоритета. В архитектуре Cortex-M0 значение приоритета задается 8-битовым числом, в котором используются только старшие биты 6 и 7, младшая часть читается как 0.

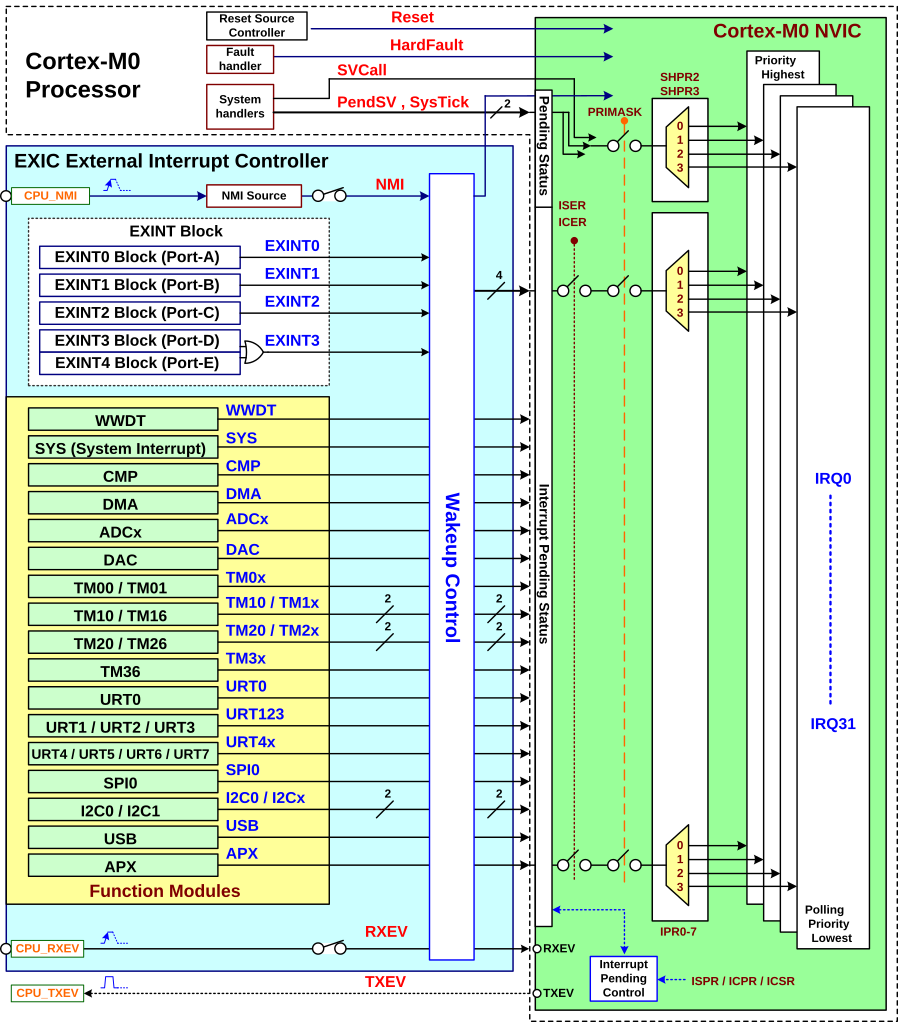

На следующем рисунке показана общая функциональная схема подсистемы прерываний.

Прерывания IRQ#0-31 для блока NVIC формируются контроллером внешних прерываний EXIC и контроллером пробуждения WIC, который получает сигналы прерываний от всех периферийных модулей.

Каждое из 32-х прерываний может быть разрешено путем записи слова с установленным битом в поле SETENA в регистр CPU_ISER (поле занимает весь регистр), соответствующим номеру прерывания. Аналогично, каждое из 32-х прерываний может быть запрещено путем записи слова с установленным соответствующим битом в поле CLRENA в регистр CPU_ICER. Чтение из этих регистров дает одинаковый результат: состояние разрешения (1) или запрета (0) соответствующего прерывания.

С помощью системных регистров CPU_ISPR (весь регистр — поле SETPEND) и CPU_ICPR (весь регистр — поле CLRPEND) можно соответственно установить или сбросить статус прерывания "отложено". Чтение из этих регистров дает статус соответствующего прерывания: "отложено" (1) или "нет" (0). Статус "отложено" возникает у прерывания, если оно происходит, например, в процессе обработки прерывания с более высоким приоритетом.

Регистры CPU_SHPR2 и CPU_SHPR3 (System Handler Priority Registers) определяют приоритет исключений SVCall (11), PendSV (14) и SysTick (15). Регистры CPU_IPR0 - CPU_IPR7 (Interrupt Priority Registers) определяют приоритет прерываний IRQ#0-31 (исключения 16-47).

Для каждого периферийного модуля имеется отдельная возможность разрешить или запретить генерацию им прерывания, а также определить конкретные события в этом модуле, которые приведут к генерации прерывания. Эти настройки осуществляются через управляющие регистры соответствующих модулей. Например, чтобы разрешить прерывания от модуля URT0, необходимо установить бит URT0_IEA в регистре RT0_INT (UART interrupt enable register).

В МК также имеется общее системное прерывание INT_SYS, которое происходит при возникновении прерываний в модулях:

RTC (INT_RTC),

IWDT (INT_IWDT),

памяти (INT_MEM),

подсистеме тактирования (INT_CSC),

подсистеме питания (INT_PW),

на шинах APB (INT_APB) и EMB (INT_EMB).

Разрешение или запрещение этого прерывания определяет бит SYS_IEA в регистре SYS_INT. В свою очередь, каждый из перечисленных модулей также имеет собственный регистр настроек и разрешения прерывания. Например, модуль RTC для разрешения своего общего прерывания имеет бит RTC_IEA в регистре RTC_INT.

Контроллер внешних прерываний EXIC позволяет обрабатывать внешние прерывания, сигналы о которых поступают на выводы портов PA-PE МК (для MG32F02A032 только PA-PD). Разрешением прерывания от порта Px (где x — A,B,C,D,E) управляет бит EXIC_Px_IEA регистра EXIC_INT.

Поля EXIC_Pxn_TRGS регистров EXIC_Px_TRGS позволяют задать одно из правил срабатывания триггеров для каждого вывода отдельно:

вывод не приводит к срабатыванию,

срабатывание по уровню,

срабатывание по фронту,

срабатывание по обоим фронтам.

Низкий или высокий уровень, передний или задний фронт импульса срабатывания триггера определяются включением или отключением инверсии соответствующих выводов в настройках самих портов. Биты EXIC_Pxn_PF регистров EXIC_Px_PF являются флагами срабатывания триггеров для каждого сконфигурированного вывода.

С помощью установки битов регистров маски EXIC_Px_MSK для каждого из портов можно организовать генерацию прерывания по схеме "ИЛИ" или по схеме "И", подключая необходимые выводы портов в качестве входов.

Регистры EXIC_SRC0 - EXIC_SRC7 позволяют выяснить, какое из внешних прерываний контроллера EXIC сработало, причем в поле EXIC_ID1 регистра EXIC_SRC0 указывается, какой именно модуль вызвал общее прерывание INT_SYS.

Отдельно обрабатывается сигнал немаскируемого прерывания NMI (исключение 2). Его источником может служить системное прерывание CPU_NMI от одноименного вывода МК (если бит EXIC_NMI_SEL регистра EXIC_CR0 сброшен) или любое из прерываний IRQ#x (если бит EXIC_NMI_SEL установлен). Номер прерывания IRQ#x во втором случае определяется полем EXIC_NMI_MUX регистра EXIC_CR0.

ЦПУ поддерживает коммуникационный интерфейс событий, включающий входной сигнал CPU_RXEV и выходной сигнал CPU_TXEV, передаваемые через одноименные выводы МК. Если бит EXIC_EM_RXEV регистра EXIC_CR0 установлен, активный сигнал CPU_RXEV заставляет ЦПУ "проснуться", если он до этого был переведен в состояние "sleep" или "deep sleep" инструкцией WFE. Сигнал CPU_TXEV активируется процессорной инструкцией SEV (Send Event).

Инициализация и загрузка МК

При включении питания в МК выполняется POR-сброс, включающий "холодный" сброс, в результате которого значения конфигурационных ячеек OB0 загружаются в соответствующие разряды регистров аппаратной конфигурации CFG_ORx. Большая часть разрядов этих регистров имеет нулевое значение по-умолчанию. Поскольку ячейки flash-памяти имеют обычно начальное значение 0xFFFFFFFF, в МК принята схема инвертирования загружаемых данных из ячеек OBx в регистры CFG_ORx, чтобы пользователь мог что-то "включить", не прибегая к процедуре стирания. Это необходимо учитывать при программировании ячеек OBx.

Согласно настройкам по-умолчанию, источником тактирования выбирается генератор HRCO с частотой 12,0000 МГц, блок PLL отключается, а большая часть делителей частоты имеет коэффициент 1.

В зависимости от значения поля BOOT_MS ячеек OB0 на адрес 0x00000000 отображается одна из следующих областей памяти:

flash-секция AP (вариант конфигурации без бутлоадера с максимальным размером прикладной части flash-памяти),

flash-секция ISP (бутлоадер),

встроенное ОЗУ SRAM.

Далее происходит сброс настроек всех выводов МК на значения по-умолчанию и выполняется сброс всех модулей и блоков. Затем процессор считывает таблицу векторов с адреса 0x00000000, инициализирует регистр стека MSP, загружает в PC адрес вектора Reset (смещение 0x00000004) и начинает выполнение инструкций. Отметим, что согласно настройкам по-умолчанию, в МК отключены практически все периферийные модули (отключено тактирование и запрещена их работа), а также отключены прерывания. Следовательно, на начальном этапе инициализации МК в программе необходимо предусмотреть выбор конфигурации тактирования подсистем МК, разрешить работу требуемых модулей, разрешить необходимые прерывания.

В следующей статье будут рассмотрены: контроллер flash-памяти, методика программирования МК на основе OpenOCD, разработка программы на gcc, управление GPIO.