Здравствуйте. В данной статье я хочу по возможности максимально просто и понятно рассказать о том, как рассчитываются временные ограничения (timing constraints) на синхронные интерфейсы ПЛИС. Просто — не значит коротко, но зато простыми словами, которые вы сможете легко понять. Если вы новичок и перед вами стоит задача описать свой первый SPI, то данная статья должна вам помочь понять для чего нужны ограничения и как их рассчитать.

Временны́е ограничения — это некоторая информация, пользуясь которой утилита временно́го анализа в составе САПР может посчитать успешно ли пройдут данные через все регистры проекта. Эти ограничения пользователь должен сам рассчитать и записать в файле временны́х ограничений. Без этих ограничений пользователь пишет проект наугад, не проверяя его работоспособность, а компилятор будет ругаться, что не нашел ограничений.

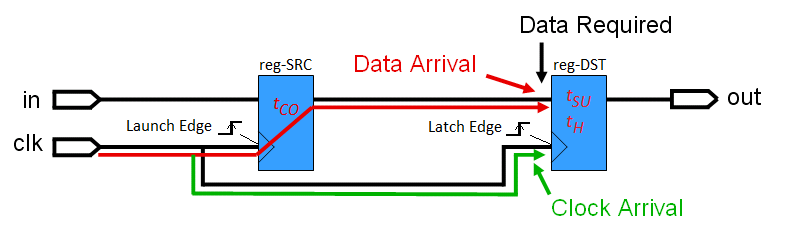

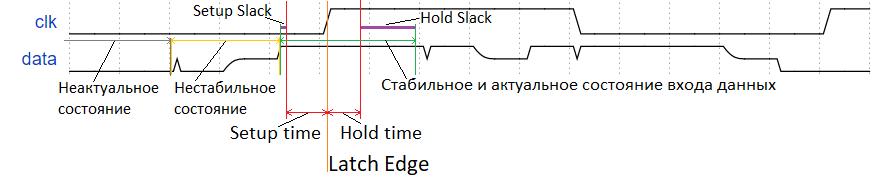

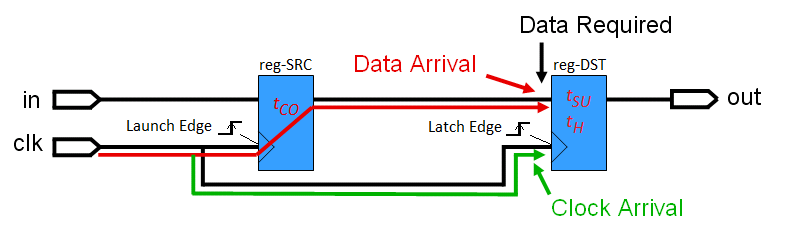

В предыдущей статье (ссылка) я рассказал о том, что из себя представляет передача данных между двумя регистрами и как рассчитывается выполнение временны́х соотношений в случае передачи данных внутри ПЛИС, когда оба рассматриваемых регистра, пути прохождения тактовых сигналов и сигналов данных лежат внутри ПЛИС. Из той статьи нужно вынести понимание концепции синхронной логики как сети, сплетенной из множества межрегистровых передач (рис.1), и термина «слэк» (рис.2).

В этой статье мы рассмотрим случаи передачи данных, в которых один из двух регистров передачи находится вне ПЛИС — это регистр внешнего устройства — микроконтроллера, АЦП и т.п.

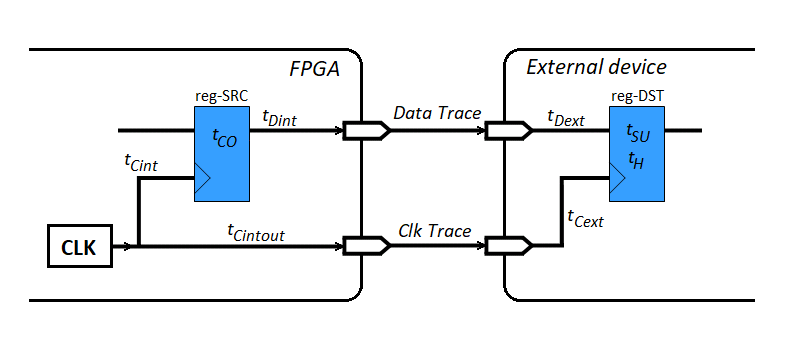

Рис. 1. Схема межрегистровой передачи данных от регистра-источника (source) к регистру-получателю (destination).

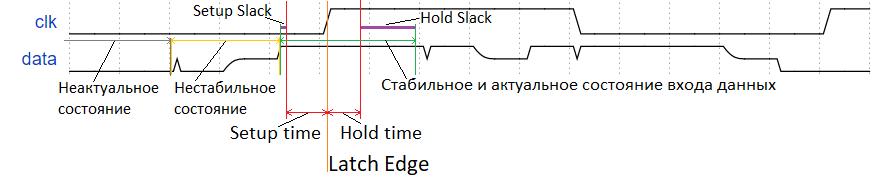

Рис. 2. Смысл слэков относительно фронта захвата на входе регистра-получателя.

Общие формулы расчета слэков, выведенные в предыдущей статье:

Пробежимся по терминам.

Слэк (slack) — это запас по времени. Он должен быть положительным.

Время предустановки (setup time, ) — минимальное время, которое данные должны уже находиться на входе регистра-получателя на момент прихода фронта клока на тактовый вход получателя.

) — минимальное время, которое данные должны уже находиться на входе регистра-получателя на момент прихода фронта клока на тактовый вход получателя.

Время удержания (hold time, ) — минимальное время, которое данные должны всё ещё держаться на входе получателя после момента прихода фронта клока на тактовый вход получателя.

) — минимальное время, которое данные должны всё ещё держаться на входе получателя после момента прихода фронта клока на тактовый вход получателя.

Время срабатывания регистра (clock-to-output time, ) — время от прихода фронта клока на тактовый вход регистра-источника до появления на его выходе новых стабильных данных.

) — время от прихода фронта клока на тактовый вход регистра-источника до появления на его выходе новых стабильных данных.

SR и HR — это Setup и Hold Relationship, разница моментов фронта захвата и фронта запуска на источнике клока с учетом нестабильности. В случае анализа внутренних передач ПЛИС берутся только восходящие фронты клока, поэтому это выражение упрощается до . Но в интерфейсах часто используются разные фронты, поэтому надо использовать более общее представление.

. Но в интерфейсах часто используются разные фронты, поэтому надо использовать более общее представление.

Нестабильность тактовой частоты по предустановке/удержанию (CSU/CHU) — мера нестабильности тактового сигнала. В расчетах несет смысл запаса «на всякий случай» для учтения явлений, вызванных неидеальной периодичностью клока.

— это время прохождения сигналом данных пути между регистрами.

— это время прохождения сигналом данных пути между регистрами.

— это время, за которое фронт тактового сигнала доходит от источника тактового сигнала до тактового входа регистра-источника. А от источника тактового сигнала до регистра-получателя — соответственно

— это время, за которое фронт тактового сигнала доходит от источника тактового сигнала до тактового входа регистра-источника. А от источника тактового сигнала до регистра-получателя — соответственно  .

.

Пути прохождения сигналов проиллюстрированы на рисунке 3.

Рис. 3. Обозначение времени прохождения путей тактовых сигналов и данных.

На этом рисунке мы видим две точки — зеленую и красную. Обе из них являются точками, в которых пути клока источника и клока получателя еще не разошлись. Зеленая точка — это выход глобального тактового буфера, точка входа в глобальную тактовую сеть ПЛИС, относительно которой тактовые входы всех регистров приблизительно равноудалены. Красная точка — некая произвольная точка в глобальной тактовой сети, в которой, как и на входе сети, клок ещё не разделился на две свои копии, ушедшие на разные регистры. Но только зеленая точка является подходящей точкой для начала отсчета времён прохождения клоков, потому что находится в одном из понятных компилятору мест. В данном примере — на входе глобальной тактовой сети. Но в случае простых интерфейсов, тактирующихся снаружи, зеленой точкой может быть и просто ножка ПЛИС. Компилятор знает тайминги от этой точки до каждого из регистров. А красная точка, место случайного совпадения путей двух анализируемых клоков, не подходит для начала отсчета.

Давайте проведем классификацию случаев для временного анализа. Анализ проводится отдельно для каждой ножки ПЛИС относительно некоторого клока. В результате анализа оценивается возможность ножки корректно отдать или принять данные. Внешний интерфейс синхронного обмена данными ПЛИС с внешним устройством представляет собой несколько линий, подведенных к ножкам. Из них одна линия — это линия клока. Он должен быть общим для регистров на обеих сторонах. Остальные линии, одна или множество, это однонаправленные линии ввода или вывода. То, что для ПЛИС является линией ввода, для внешнего устройства является линией вывода, и наоборот. В данной статье мы рассматриваем только простейшие случаи временного анализа, поэтому не касаемся асинхронных и самосинхронных интерфейсов, а также использования двунаправленных линий ввода-вывода.

Случаи анализа можно классифицировать по направлению данных относительно ПЛИС (Input/Output) и по направлению клока относительно ПЛИС (данные тактируются от ПЛИС/от внешнего источника). Для каждого случая есть два типа анализа (Setup/Hold). Итого, четыре случая для анализа и восемь уравнений, которые нам надо вывести.

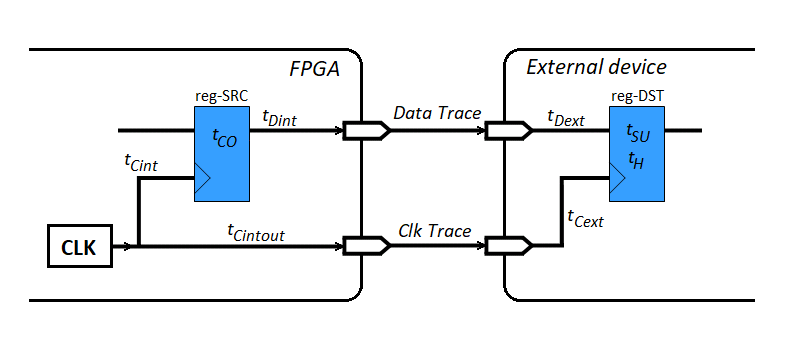

Рассмотрим случай, когда нам нужно отдать что-то наружу на своем клоке (рис.4).

Принципиально схема передачи данных не изменилась. Вот только регистры теперь принадлежат двум разным микросхемам, а на пути данных между ними не комбинационная логика, а просто дорожки на плате. И наша задача состоит в том, чтобы адаптировать известные нам формулы слэков к немного иной ситуации.

Рис. 4. Передача данных наружу по собственному клоку ПЛИС.

На рисунке 4 мы видим схему межрегистровой передачи. На ней показаны времена процессов, относящиеся к каждому из регистров, и времена, за которые сигналы проходят пути.

Я задал следующую индексацию: время, относящееся к данным, помечено буквой D. Время, относящееся к клоку, помечено буквой C. Если событие происходит внутри ПЛИС, то его время помечено индексом «int», а если во внешнем устройстве, то «ext». Время на путь клока от источника клока до выходной клоковой ножки имеет самый длинный индекс «Cintout». DataTrace и ClkTrace — это времена на проход соответствующих дорожек на печатной плате. Блок «CLK» символизирует собой некий внутренний источник клока.

Главная черта упомянутых на рисунке величин — все они положительные. Все они равны абсолютной длительности каких-либо физических процессов, а значит физически могут быть только положительными величинами. Это важно для дальнейших рассуждений.

Теперь мы максимально подробно рассмотрим анализ слэка предустановки. Глядя на рисунок 4 мы легко соотносим увиденные величины со слагаемыми формул слэков:

Вот теперь мы пользуемся знанием того, что все слагаемые, которые сейчас в скобках, больше нуля. А значит мы знаем как раскрыть такие скобки: минимум суммы равен сумме минимумов, а максимум суммы равен сумме максимумов:

Теперь переставим слагаемые местами так, чтобы сгруппировать в скобках слагаемые процессов внутри ПЛИС и процессов внутри внешнего устройства:

Что же мы видим в скобках? Если присмотреться и еще раз вспомнить про то, что все указанные величины больше нуля, то можно сказать, что мы видим выражение некого эквивалентного (со звездочкой) времени срабатывания регистра ПЛИС и эквивалентного времени предустановки регистра внешнего устройства:

Почему бы нам не пользоваться эквивалентными величинами, если производители микросхем уже посчитали их за нас с учетом своих внутренних задержек? Эквивалентные значения на стороне ПЛИС рассчитает компилятор без участия пользователя, а эквивалентные значения внешнего устройства указываются в явном виде в даташите на устройство.

Теперь вглядимся внимательно еще раз в последнее выражение. В нем первые три слагаемых уже известны анализатору, ведь мы уже указали ему рабочую частоту и величину нестабильности. Компилятор произвел трассировку и анализатор знает эквивалентное время срабатывания своего регистра. Значит анализатору известна длительность всех процессов внутри ПЛИС. А вот последние три слагаемых уникальны для каждой ножки и пользователю необходимо самому их посчитать и указать анализатору в виде числа. Что же это за число? Рассмотрев внимательнее три последних слагаемых мы увидим, что их можно интерпретировать как отрицательный максимум некой величины:

И эта величина по смыслу равна задержке всего, что происходит снаружи ПЛИС, относительно всего, что происходит внутри. Ее так и называют — выходная задержка, Output Delay.

Подытожим:

Теперь выведем аналогичное уравнение для слэка удержания. Вспомним общее уравнение и подставим в него новые слагаемые:

и

и  :

:

Подытожим:

Надо подчеркнуть, что и

и  — это минимум и максимум не абсолютно одной и той же величины. В каждом анализе по предустановке и анализе по удержанию рассматриваются разные ситуации и разные внешние задержки. А значит и слагаемые, как видно из формул, берутся разные.

— это минимум и максимум не абсолютно одной и той же величины. В каждом анализе по предустановке и анализе по удержанию рассматриваются разные ситуации и разные внешние задержки. А значит и слагаемые, как видно из формул, берутся разные.

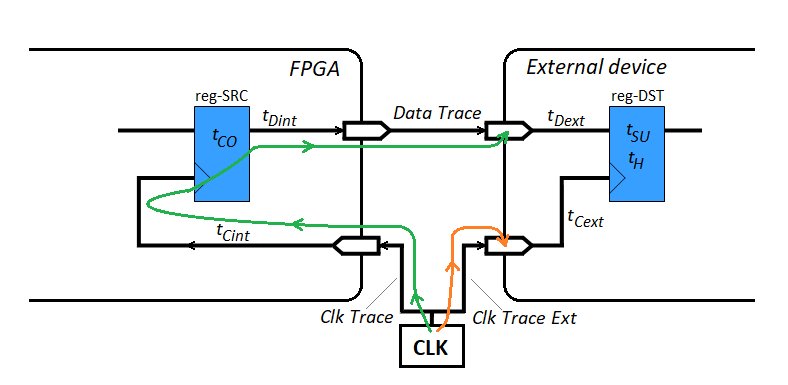

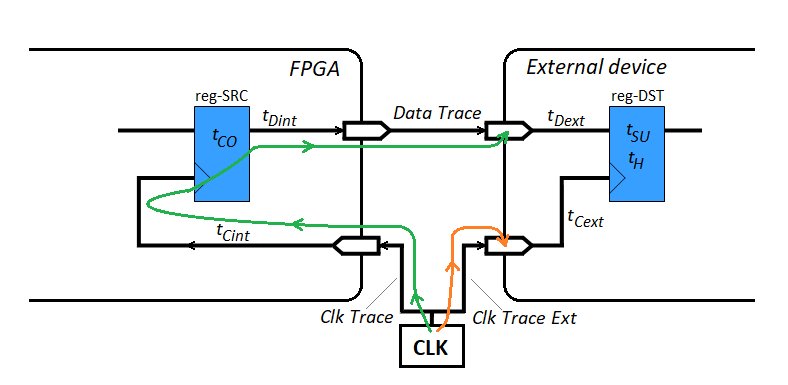

Теперь перейдем к случаю, когда нам нужно отдать что-то наружу, но по внешнему относительно ПЛИС клоку (рис.5). В общем случае источник клока находится снаружи ПЛИС, в частности он может быть внутри внешнего устройства.

Рис. 5. Передача данных наружу по внешнему клоку.

На рисунке 5 мы видим источник клока снаружи. Соответственно исчезла величина и появилось время прохода клока до внешнего устройства «Clk Trace Ext».

и появилось время прохода клока до внешнего устройства «Clk Trace Ext».

Глядя на рисунок 5 соотнесём увиденные величины со слагаемыми общих формул слэков:

С помощью этих выражений раскроем слагаемые в формуле слэка предустановки, сразу сгруппируем их по регистрам и получим эквивалентный вид:

Аналогично разбираем слэк удержания:

Если в этой схеме рассмотреть частный (но частый) случай, когда источник клока находится внутри внешнего устройства, то выведенные формулы изменятся только лишь тем, что ClkTraceExt станет в них равным нулю. Перемещение источника клока вовнутрь внешнего устройства вызовет в наших расчетах микроскопическое растекание клока внутри внешнего устройства между тактовым выходом и регистром, но оно будет учтено производителем внешнего устройства и войдет в величины эквивалентных и

и  .

.

Теперь переходим к рассмотрению входных ног синхронного интерфейса. ПЛИС и внешнее устройство на рисунке 6 поменялись местами.

Рис. 6. Прием данных по собственному клоку ПЛИС.

Анализ такой схемы ничуть не сложнее предыдущих.

Теперь слэк удержания:

Также, по накатанной, смотрим на схему передачи данных и раскрываем слагаемые общей формулы.

Рис. 7. Прием данных по внешнему клоку.

Формула слэка предустановки:

Формула слэка удержания:

Опять же, если источник клока находится внутри внешнего устройства — то просто приравниваем ClkTraceExt нулю.

Формулы — это конечно хорошо, но если вы погружаетесь в данную тему в первый, раз, то формулы выглядят непонятными, неживыми. Хочется что-то попонятнее, чтобы формулы обрели видимый смысл. Хорошо, давайте разберем физический смысл формул взяв для примера случай вывода данных по внешнему клоку. Напомню как выглядят схема и формулы:

Рис. 8. Передача данных наружу по внешнему клоку.

В ходе передачи данных происходят два события: срабатывает регистр-источник и срабатывает регистр-получатель. События происходят потому что их инициируют фронты клока, выходящие из источника клока. Отсюда и начнем смотреть.

Источник клока порождает фронт запуска и тот за время ClkTrace добирается до ПЛИС. Далее происходит срабатывание регистра ПЛИС за время . Далее порожденные этим срабатыванием новые данные идут от ПЛИС к внешнему устройству за время DataTrace.

. Далее порожденные этим срабатыванием новые данные идут от ПЛИС к внешнему устройству за время DataTrace.

С другой стороны источник клока также порождает и фронт захвата и тот добирается до внешнего устройства за время ClkTraceExt.

Встречаются эти два события на входе данных внешнего устройства. И тут важно чтобы данные пришли туда раньше, чем регистр-получатель начнет захват. Они должны прийти с запасом времени по меньшей мере , а лучше еще раньше. Чтобы убедиться что это выполнится рассматривают самый худший случай. Если запас есть даже в самом худшем случае — значит точно все в порядке. Поэтому самый худший момент прибытия данных — это самый поздний момент,

, а лучше еще раньше. Чтобы убедиться что это выполнится рассматривают самый худший случай. Если запас есть даже в самом худшем случае — значит точно все в порядке. Поэтому самый худший момент прибытия данных — это самый поздний момент,  . А худший момент ожидания данных — это самый ранний момент,

. А худший момент ожидания данных — это самый ранний момент,  . И даже в худшем случае второй момент должен быть позже первого:

. И даже в худшем случае второй момент должен быть позже первого:

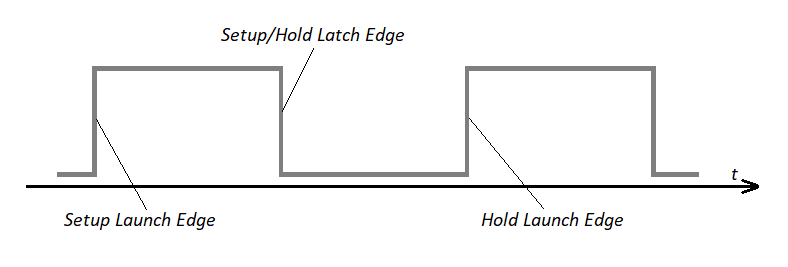

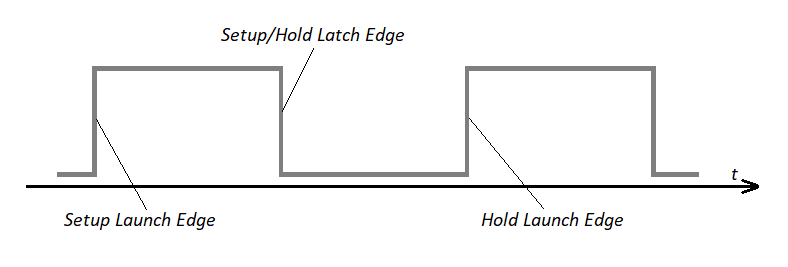

В этом выражении мы видим моменты фронтов — LaunchEdge и LatchEdge, которые обычно спрятаны в слагаемых SR и HR. Давайте вспомним что это такое. В анализе предустановки и удержания рассматриваются четыре фронта:

Setup Launch Edge — тот фронт, что заставит источник отправить данные, которые должен ловить получатель.

Hold Launch Edge — тот фронт, что заставит источник отправить следующие данные, которые могут помешать получателю успеть захватить предыдущие. Между Setup LaunchEdge и Hold Launch Edge по определению всегда один период клока.

Setup Latch Edge — тот фронт, что заставит получателя захватывать данные на входе.

Hold Latch Edge — это тот же Setup Latch Edge. То есть по сути Latch Edge физически един, просто ему даются для красоты два имени в двух видах анализа.

Внутри ПЛИС синхронная логика обычно работает только на восходящих фронтах (рис. 9). В этом случае с точки зрения анализа слэка предустановки Setup Launch Edge и Setup Latch Edge разнесены друг от друга на один период клока, а с точки зрения анализа удержания Hold Launch Edge и Hold Latch Edge совпадают.

Рис. 9. Взаимное расположение фронтов в случае когда оба регистра тактируются восходящими фронтами.

Однако никто не запрещает завести на тактовый вход одного из двух регистров инвертированный тактовый сигнал и тем самым заставить его работать по падающему фронту клока. Так, кстати, часто и делается в тех же интерфейсах SPI. Давайте изучим подробнее этот вариант работы.

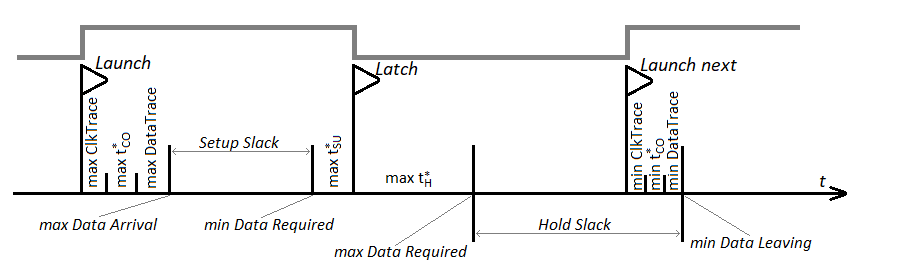

Рассмотрим ситуацию вывода данных из ПЛИС по внешнему клоку, но один из двух регистров работает на инвертированном клоке, то есть по падающему фронту. Пускай это будет регистр-получатель на внешнем устройстве. Тогда роли фронтов во времени распределятся иначе (рис.10).

Рис. 10. Взаимное расположение фронтов в случае когда источник тактируется восходящим фронтом, а получатель падающим фронтом.

Такое включение регистров позволяет выравнивать размеры слэков по предустановке и удержанию. Если бы регистры работали от фронтов одного направления, то из-за мизерного в сравнении с периодом клока времени распространения сигналов по дорожкам платы слэк предустановки был бы огромным, а слэк удержания очень мал.

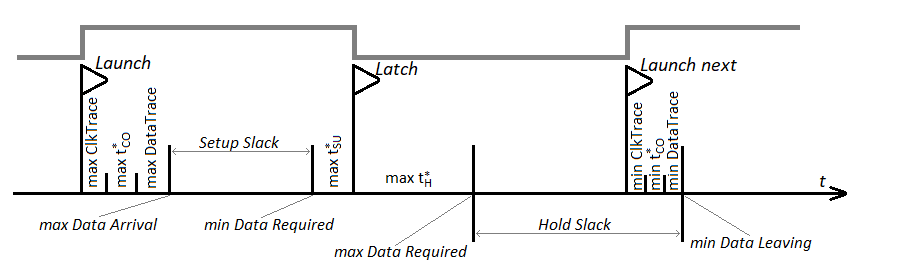

На рисунке 11 показана картина временных слагаемых относительно тактового сигнала на источнике клока. Для упрощения рисунка я не стал указывать слагаемое ClkTraceExt. Будем считать, что источник клока находится внутри внешнего устройства.

Рис. 11. Положение слэков во времени относительно фронтов клока в случае когда получатель тактируется падающим фронтом.

На этом рисунке max Data Arrival — это самый поздний момент, когда данные могут прийти на вход получателя. Самый ранний момент, когда данные точно должны уже быть на входе получателя — это min Data Required. Самый поздний момент, когда данные еще должны быть на входе получателя — это max Data Required. А самый ранний момент, когда данные могут уже уйти со входа получателя сменяясь следующими данными — назван min Data Leaving.

Теперь формулы и их слагаемые должны стать понятнее.

Мы получили формулы внешних задержек и можем рассчитать конкретные числа задержек, чтобы вписать их в файл временных ограничений. Эти формулы глобально состоят из двух видов слагаемых — это временные характеристики портов внешнего устройства и задержка на дорожках платы.

Характеристики портов обычно находятся в даташитах в разделах под названиями вроде «Electrical Characteristics / AC Specifications / Timing Requirements». Порой эти характеристики названы другими именами и придется проявить смекалку, чтобы найти их. Но таблицы с числами как правило сопровождаются временными диаграммами, которые позволят вам идентифицировать нужный параметр. Важный нюанс, который может сбить с толку, в даташитах на многие микросхемы выходные ножки часто описываются параметрами «Setup Output time» и «Hold Output time». В формулах данной статьи их следует сопоставлять так: .

.

С дорожками несколько сложнее. Точный расчет задержки на плате — вопрос нетривиальный. Задержка зависит от длины, ширины, толщины и углов поворота дорожки, от толщины и материала платы, от расстояния до разных земляных слоев, от близости дорожек друг к другу и от множества иных факторов. Впрочем влияние каждого из этих факторов довольно невелико и на низких частотах интерфейсов, до десятков мегагерц, этими сложностями можно пренебречь. Упрощенный расчет задержки на дорожке выглядит так: скорость распространения волны в фольге считается равной половине скорости света в вакууме. В пересчете это дает примерно 0.007 нс/мм. Погрешность такой оценки нивелируется широким диапазоном оценки задержки. Для максимальной задержки считаем удельную задержку равной 0.010 нс/мм, а для минимальной — 0.005 нс/мм.

Есть еще один нюанс. Схемотехники, проектируя печатные платы, стараются протягивать дорожки синхронных интерфейсов примерно одинаковым путем и соблюсти их равные длины. Проверьте длины дорожек данных и клока на своей целевой плате. Скорее всего они почти равны и компонент выражений (DataTrace — ClkTrace) на практике можно считать нулевым.

Если на пути данных или клока стоит элемент вносящий задержку — ее тоже нужно учесть. Это может быть буфер, инвертор, преобразователь уровня или гальваноразвязка. Такие элементы способны вносить очень большую задержку, десятки наносекунд, поэтому к ним нужно отнестись очень внимательно.

В данной статье вы увидели формулы, по которым определяется выполнение временных ограничений в синхронных интерфейсах. Зная эти формулы можно понимать от чего зависит успешная передача данных и как рассчитать верные ограничения для анализатора. В следующей статье я приведу пример оформления файла временных ограничений и использования анализатора.

Введение

Временны́е ограничения — это некоторая информация, пользуясь которой утилита временно́го анализа в составе САПР может посчитать успешно ли пройдут данные через все регистры проекта. Эти ограничения пользователь должен сам рассчитать и записать в файле временны́х ограничений. Без этих ограничений пользователь пишет проект наугад, не проверяя его работоспособность, а компилятор будет ругаться, что не нашел ограничений.

В предыдущей статье (ссылка) я рассказал о том, что из себя представляет передача данных между двумя регистрами и как рассчитывается выполнение временны́х соотношений в случае передачи данных внутри ПЛИС, когда оба рассматриваемых регистра, пути прохождения тактовых сигналов и сигналов данных лежат внутри ПЛИС. Из той статьи нужно вынести понимание концепции синхронной логики как сети, сплетенной из множества межрегистровых передач (рис.1), и термина «слэк» (рис.2).

В этой статье мы рассмотрим случаи передачи данных, в которых один из двух регистров передачи находится вне ПЛИС — это регистр внешнего устройства — микроконтроллера, АЦП и т.п.

Рис. 1. Схема межрегистровой передачи данных от регистра-источника (source) к регистру-получателю (destination).

Рис. 2. Смысл слэков относительно фронта захвата на входе регистра-получателя.

Общие формулы расчета слэков, выведенные в предыдущей статье:

Пробежимся по терминам.

Слэк (slack) — это запас по времени. Он должен быть положительным.

Время предустановки (setup time,

Время удержания (hold time,

Время срабатывания регистра (clock-to-output time,

SR и HR — это Setup и Hold Relationship, разница моментов фронта захвата и фронта запуска на источнике клока с учетом нестабильности. В случае анализа внутренних передач ПЛИС берутся только восходящие фронты клока, поэтому это выражение упрощается до

Нестабильность тактовой частоты по предустановке/удержанию (CSU/CHU) — мера нестабильности тактового сигнала. В расчетах несет смысл запаса «на всякий случай» для учтения явлений, вызванных неидеальной периодичностью клока.

Пути прохождения сигналов проиллюстрированы на рисунке 3.

Рис. 3. Обозначение времени прохождения путей тактовых сигналов и данных.

На этом рисунке мы видим две точки — зеленую и красную. Обе из них являются точками, в которых пути клока источника и клока получателя еще не разошлись. Зеленая точка — это выход глобального тактового буфера, точка входа в глобальную тактовую сеть ПЛИС, относительно которой тактовые входы всех регистров приблизительно равноудалены. Красная точка — некая произвольная точка в глобальной тактовой сети, в которой, как и на входе сети, клок ещё не разделился на две свои копии, ушедшие на разные регистры. Но только зеленая точка является подходящей точкой для начала отсчета времён прохождения клоков, потому что находится в одном из понятных компилятору мест. В данном примере — на входе глобальной тактовой сети. Но в случае простых интерфейсов, тактирующихся снаружи, зеленой точкой может быть и просто ножка ПЛИС. Компилятор знает тайминги от этой точки до каждого из регистров. А красная точка, место случайного совпадения путей двух анализируемых клоков, не подходит для начала отсчета.

Виды анализируемых передач

Давайте проведем классификацию случаев для временного анализа. Анализ проводится отдельно для каждой ножки ПЛИС относительно некоторого клока. В результате анализа оценивается возможность ножки корректно отдать или принять данные. Внешний интерфейс синхронного обмена данными ПЛИС с внешним устройством представляет собой несколько линий, подведенных к ножкам. Из них одна линия — это линия клока. Он должен быть общим для регистров на обеих сторонах. Остальные линии, одна или множество, это однонаправленные линии ввода или вывода. То, что для ПЛИС является линией ввода, для внешнего устройства является линией вывода, и наоборот. В данной статье мы рассматриваем только простейшие случаи временного анализа, поэтому не касаемся асинхронных и самосинхронных интерфейсов, а также использования двунаправленных линий ввода-вывода.

Случаи анализа можно классифицировать по направлению данных относительно ПЛИС (Input/Output) и по направлению клока относительно ПЛИС (данные тактируются от ПЛИС/от внешнего источника). Для каждого случая есть два типа анализа (Setup/Hold). Итого, четыре случая для анализа и восемь уравнений, которые нам надо вывести.

Вывод данных, тактированных внутренним клоком ПЛИС

Рассмотрим случай, когда нам нужно отдать что-то наружу на своем клоке (рис.4).

Принципиально схема передачи данных не изменилась. Вот только регистры теперь принадлежат двум разным микросхемам, а на пути данных между ними не комбинационная логика, а просто дорожки на плате. И наша задача состоит в том, чтобы адаптировать известные нам формулы слэков к немного иной ситуации.

Рис. 4. Передача данных наружу по собственному клоку ПЛИС.

На рисунке 4 мы видим схему межрегистровой передачи. На ней показаны времена процессов, относящиеся к каждому из регистров, и времена, за которые сигналы проходят пути.

Я задал следующую индексацию: время, относящееся к данным, помечено буквой D. Время, относящееся к клоку, помечено буквой C. Если событие происходит внутри ПЛИС, то его время помечено индексом «int», а если во внешнем устройстве, то «ext». Время на путь клока от источника клока до выходной клоковой ножки имеет самый длинный индекс «Cintout». DataTrace и ClkTrace — это времена на проход соответствующих дорожек на печатной плате. Блок «CLK» символизирует собой некий внутренний источник клока.

Главная черта упомянутых на рисунке величин — все они положительные. Все они равны абсолютной длительности каких-либо физических процессов, а значит физически могут быть только положительными величинами. Это важно для дальнейших рассуждений.

Теперь мы максимально подробно рассмотрим анализ слэка предустановки. Глядя на рисунок 4 мы легко соотносим увиденные величины со слагаемыми формул слэков:

Теперь подставим эти равенства в формулу слэка предустановки:

Вот теперь мы пользуемся знанием того, что все слагаемые, которые сейчас в скобках, больше нуля. А значит мы знаем как раскрыть такие скобки: минимум суммы равен сумме минимумов, а максимум суммы равен сумме максимумов:

Теперь переставим слагаемые местами так, чтобы сгруппировать в скобках слагаемые процессов внутри ПЛИС и процессов внутри внешнего устройства:

Что же мы видим в скобках? Если присмотреться и еще раз вспомнить про то, что все указанные величины больше нуля, то можно сказать, что мы видим выражение некого эквивалентного (со звездочкой) времени срабатывания регистра ПЛИС и эквивалентного времени предустановки регистра внешнего устройства:

Почему бы нам не пользоваться эквивалентными величинами, если производители микросхем уже посчитали их за нас с учетом своих внутренних задержек? Эквивалентные значения на стороне ПЛИС рассчитает компилятор без участия пользователя, а эквивалентные значения внешнего устройства указываются в явном виде в даташите на устройство.

Теперь вглядимся внимательно еще раз в последнее выражение. В нем первые три слагаемых уже известны анализатору, ведь мы уже указали ему рабочую частоту и величину нестабильности. Компилятор произвел трассировку и анализатор знает эквивалентное время срабатывания своего регистра. Значит анализатору известна длительность всех процессов внутри ПЛИС. А вот последние три слагаемых уникальны для каждой ножки и пользователю необходимо самому их посчитать и указать анализатору в виде числа. Что же это за число? Рассмотрев внимательнее три последних слагаемых мы увидим, что их можно интерпретировать как отрицательный максимум некой величины:

И эта величина по смыслу равна задержке всего, что происходит снаружи ПЛИС, относительно всего, что происходит внутри. Ее так и называют — выходная задержка, Output Delay.

Подытожим:

Теперь выведем аналогичное уравнение для слэка удержания. Вспомним общее уравнение и подставим в него новые слагаемые:

Раскроем скобки и сразу же сгруппируем слагаемые вокруг каждого из регистров:

И снова мы видим как слагаемые группируются в эквивалентные величины, на сей раз

И последние три слагаемых можно понимать как минимальную внешнюю задержку:

Подытожим:

Надо подчеркнуть, что

Вывод данных, тактированных внешним клоком

Теперь перейдем к случаю, когда нам нужно отдать что-то наружу, но по внешнему относительно ПЛИС клоку (рис.5). В общем случае источник клока находится снаружи ПЛИС, в частности он может быть внутри внешнего устройства.

Рис. 5. Передача данных наружу по внешнему клоку.

На рисунке 5 мы видим источник клока снаружи. Соответственно исчезла величина

Глядя на рисунок 5 соотнесём увиденные величины со слагаемыми общих формул слэков:

С помощью этих выражений раскроем слагаемые в формуле слэка предустановки, сразу сгруппируем их по регистрам и получим эквивалентный вид:

Аналогично разбираем слэк удержания:

Если в этой схеме рассмотреть частный (но частый) случай, когда источник клока находится внутри внешнего устройства, то выведенные формулы изменятся только лишь тем, что ClkTraceExt станет в них равным нулю. Перемещение источника клока вовнутрь внешнего устройства вызовет в наших расчетах микроскопическое растекание клока внутри внешнего устройства между тактовым выходом и регистром, но оно будет учтено производителем внешнего устройства и войдет в величины эквивалентных

Ввод данных, тактированных внутренним клоком ПЛИС

Теперь переходим к рассмотрению входных ног синхронного интерфейса. ПЛИС и внешнее устройство на рисунке 6 поменялись местами.

Рис. 6. Прием данных по собственному клоку ПЛИС.

Анализ такой схемы ничуть не сложнее предыдущих.

Раскрываем, группируем…

И получаем величину внешней задержки, которую на этот раз уже мы назовем входной:

Теперь слэк удержания:

Ввод данных, тактированных внешним клоком

Также, по накатанной, смотрим на схему передачи данных и раскрываем слагаемые общей формулы.

Рис. 7. Прием данных по внешнему клоку.

Формула слэка предустановки:

Формула слэка удержания:

Опять же, если источник клока находится внутри внешнего устройства — то просто приравниваем ClkTraceExt нулю.

Наглядная интерпретация

Формулы — это конечно хорошо, но если вы погружаетесь в данную тему в первый, раз, то формулы выглядят непонятными, неживыми. Хочется что-то попонятнее, чтобы формулы обрели видимый смысл. Хорошо, давайте разберем физический смысл формул взяв для примера случай вывода данных по внешнему клоку. Напомню как выглядят схема и формулы:

Рис. 8. Передача данных наружу по внешнему клоку.

В ходе передачи данных происходят два события: срабатывает регистр-источник и срабатывает регистр-получатель. События происходят потому что их инициируют фронты клока, выходящие из источника клока. Отсюда и начнем смотреть.

Источник клока порождает фронт запуска и тот за время ClkTrace добирается до ПЛИС. Далее происходит срабатывание регистра ПЛИС за время

С другой стороны источник клока также порождает и фронт захвата и тот добирается до внешнего устройства за время ClkTraceExt.

Встречаются эти два события на входе данных внешнего устройства. И тут важно чтобы данные пришли туда раньше, чем регистр-получатель начнет захват. Они должны прийти с запасом времени по меньшей мере

Надеюсь такое объяснение проливает больше света на происходящее.

В этом выражении мы видим моменты фронтов — LaunchEdge и LatchEdge, которые обычно спрятаны в слагаемых SR и HR. Давайте вспомним что это такое. В анализе предустановки и удержания рассматриваются четыре фронта:

Setup Launch Edge — тот фронт, что заставит источник отправить данные, которые должен ловить получатель.

Hold Launch Edge — тот фронт, что заставит источник отправить следующие данные, которые могут помешать получателю успеть захватить предыдущие. Между Setup LaunchEdge и Hold Launch Edge по определению всегда один период клока.

Setup Latch Edge — тот фронт, что заставит получателя захватывать данные на входе.

Hold Latch Edge — это тот же Setup Latch Edge. То есть по сути Latch Edge физически един, просто ему даются для красоты два имени в двух видах анализа.

Внутри ПЛИС синхронная логика обычно работает только на восходящих фронтах (рис. 9). В этом случае с точки зрения анализа слэка предустановки Setup Launch Edge и Setup Latch Edge разнесены друг от друга на один период клока, а с точки зрения анализа удержания Hold Launch Edge и Hold Latch Edge совпадают.

Рис. 9. Взаимное расположение фронтов в случае когда оба регистра тактируются восходящими фронтами.

Однако никто не запрещает завести на тактовый вход одного из двух регистров инвертированный тактовый сигнал и тем самым заставить его работать по падающему фронту клока. Так, кстати, часто и делается в тех же интерфейсах SPI. Давайте изучим подробнее этот вариант работы.

Рассмотрим ситуацию вывода данных из ПЛИС по внешнему клоку, но один из двух регистров работает на инвертированном клоке, то есть по падающему фронту. Пускай это будет регистр-получатель на внешнем устройстве. Тогда роли фронтов во времени распределятся иначе (рис.10).

Рис. 10. Взаимное расположение фронтов в случае когда источник тактируется восходящим фронтом, а получатель падающим фронтом.

Такое включение регистров позволяет выравнивать размеры слэков по предустановке и удержанию. Если бы регистры работали от фронтов одного направления, то из-за мизерного в сравнении с периодом клока времени распространения сигналов по дорожкам платы слэк предустановки был бы огромным, а слэк удержания очень мал.

На рисунке 11 показана картина временных слагаемых относительно тактового сигнала на источнике клока. Для упрощения рисунка я не стал указывать слагаемое ClkTraceExt. Будем считать, что источник клока находится внутри внешнего устройства.

Рис. 11. Положение слэков во времени относительно фронтов клока в случае когда получатель тактируется падающим фронтом.

На этом рисунке max Data Arrival — это самый поздний момент, когда данные могут прийти на вход получателя. Самый ранний момент, когда данные точно должны уже быть на входе получателя — это min Data Required. Самый поздний момент, когда данные еще должны быть на входе получателя — это max Data Required. А самый ранний момент, когда данные могут уже уйти со входа получателя сменяясь следующими данными — назван min Data Leaving.

Теперь формулы и их слагаемые должны стать понятнее.

Как пользоваться полученными формулами

Мы получили формулы внешних задержек и можем рассчитать конкретные числа задержек, чтобы вписать их в файл временных ограничений. Эти формулы глобально состоят из двух видов слагаемых — это временные характеристики портов внешнего устройства и задержка на дорожках платы.

Характеристики портов обычно находятся в даташитах в разделах под названиями вроде «Electrical Characteristics / AC Specifications / Timing Requirements». Порой эти характеристики названы другими именами и придется проявить смекалку, чтобы найти их. Но таблицы с числами как правило сопровождаются временными диаграммами, которые позволят вам идентифицировать нужный параметр. Важный нюанс, который может сбить с толку, в даташитах на многие микросхемы выходные ножки часто описываются параметрами «Setup Output time» и «Hold Output time». В формулах данной статьи их следует сопоставлять так:

С дорожками несколько сложнее. Точный расчет задержки на плате — вопрос нетривиальный. Задержка зависит от длины, ширины, толщины и углов поворота дорожки, от толщины и материала платы, от расстояния до разных земляных слоев, от близости дорожек друг к другу и от множества иных факторов. Впрочем влияние каждого из этих факторов довольно невелико и на низких частотах интерфейсов, до десятков мегагерц, этими сложностями можно пренебречь. Упрощенный расчет задержки на дорожке выглядит так: скорость распространения волны в фольге считается равной половине скорости света в вакууме. В пересчете это дает примерно 0.007 нс/мм. Погрешность такой оценки нивелируется широким диапазоном оценки задержки. Для максимальной задержки считаем удельную задержку равной 0.010 нс/мм, а для минимальной — 0.005 нс/мм.

Есть еще один нюанс. Схемотехники, проектируя печатные платы, стараются протягивать дорожки синхронных интерфейсов примерно одинаковым путем и соблюсти их равные длины. Проверьте длины дорожек данных и клока на своей целевой плате. Скорее всего они почти равны и компонент выражений (DataTrace — ClkTrace) на практике можно считать нулевым.

Если на пути данных или клока стоит элемент вносящий задержку — ее тоже нужно учесть. Это может быть буфер, инвертор, преобразователь уровня или гальваноразвязка. Такие элементы способны вносить очень большую задержку, десятки наносекунд, поэтому к ним нужно отнестись очень внимательно.

Заключение

В данной статье вы увидели формулы, по которым определяется выполнение временных ограничений в синхронных интерфейсах. Зная эти формулы можно понимать от чего зависит успешная передача данных и как рассчитать верные ограничения для анализатора. В следующей статье я приведу пример оформления файла временных ограничений и использования анализатора.