Технологический процесс с проектными нормами 32 нм.

Два ядра ARMv7 с тактовой частотой 1,3 ГГц

Оперативная память – 1 Гбайт.

Технологический процесс с проектными нормами 150 нм.

Одно ядро PowerPC с тактовой частотой 200 МГц.

Оперативная память – 256 Мбайт.

Сверху – параметры центрального процессора iPhone5, внизу – марсохода Curiosity. Бортовой компьютер марсохода стоит приблизительно в двести раз дороже нового айфона. Почему так? Центральный процессор космического аппарата должен быть устойчивым к воздействию радиации. На Хабре уже была хорошая обзорная статья о космической электронике, а я постараюсь подробнее рассказать о физических принципах и эффектах, стоящих за сбоями и отказами в космосе.

Рисунок 1. Стоимость одноплатных компьютеров RAD компании BAE Systems измеряется в сотнях тысяч долларов.

Основные источники радиации – Солнце и звезды. Собственное светило снабжает нас протонами и электронами; от остальных звезд летит все подряд, включая, например, ядра тяжелых элементов. Обитателей Земли от радиации защищает магнитное поле, собирающее пролетающие частицы в радиационные пояса земли (также называемые поясами ван Аллена), и атмосфера, задерживающая то, что остаётся. Они же – серьезная проблема для космических аппаратов, так что время, проводимое ими в радиационных поясах, стараются минимизировать.

Рисунок 2. Радиационные пояса Земли.

Что происходит, когда микросхема попадает в космос? Основные эффекты – накопление полной поглощенной дозы (total ionizing dose, TID), эффекты, связанные с воздействием одиночных ионизирующих частиц (Single Event Effects, SEE), и эффекты смещения (displacement damage), когда прилетающие частицы выбивают атомы с их мест в кристаллической решетке.

Полная поглощенная доза излучения обуславливает дрейф некоторых характеристик микросхемы, который способен вызвать отказ, как параметрические, так и функциональные. Наиболее важные механизмы различаются от технологии к технологии; для современных микросхем актуальны радиационно-индуцированные токи утечки, а в старых технологиях важную роль играл сдвиг порогового напряжения транзистора.

Под действием ионизирующего излучения в микросхеме происходит образование электронно-дырочных пар. Эти пары в нормальных условиях достаточно быстро рекомбинируют (то есть оторвавшийся электрон захватывается атомом обратно), однако в электрическом поле дырки и электроны могут разделяться (потому что заряды противоположного знака движутся в поле в разные стороны). Основной изолятор, используемый в кремниевых микросхемах – диоксид кремния (SiO2). Подвижность электронов и дырок в SiO2 различается на несколько порядков, поэтому электроны достаточно быстро выносятся в кремний, а дырки могут накапливаться в оксиде и на границе оксида с кремнием.

Если заряд накопился в подзатворном диэлектрике МОП-транзистора, он будет влиять на его работу как дополнительно приложенное положительное напряжение (или как сдвиг порогового напряжения). В результате n-канальный транзистор будет приоткрываться. В старых технологиях с толстыми подзатворными диэлектриками сдвиг порогового напряжения n-канальных транзисторов мог быть достаточно большим для того, чтобы транзистор полностью переставал закрываться, что естественным образом приводило к потере работоспособности схемы. Впрочем, уменьшение порогового напряжения еще раньше приводило к тому, что общий ток потребления микросхемы превышал допустимый уровень из-за утечек.

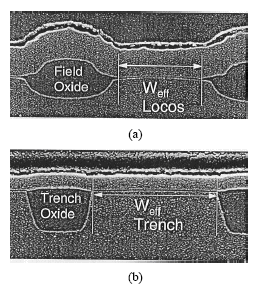

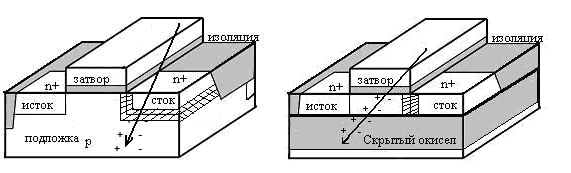

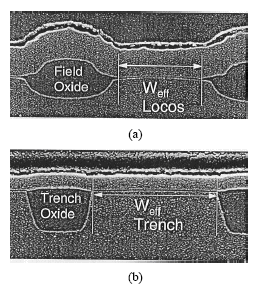

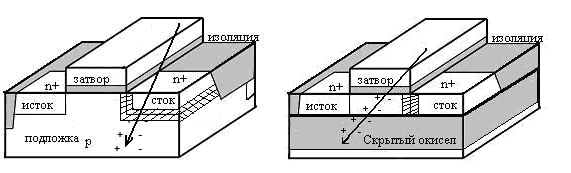

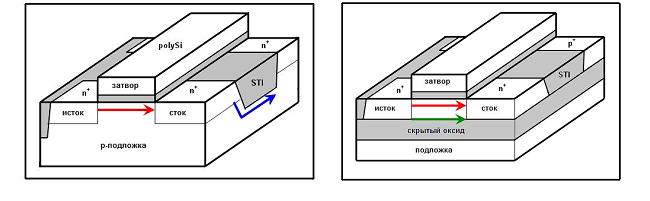

В современных технологиях толщина подзатворного диэлектрика составляет единицы нанометров, и в них попросту не может накопиться достаточно дырок для того, чтобы пороговое напряжение транзистора серьезно изменилось. Поэтому главную роль играет накопление заряда в других имеющихся в микросхеме оксидах, а именно в боковой изоляции, разделяющей соседние транзисторы, и на ее границе в подзатворным диэлектриком. На рисунке показано сечение МОП-транзистора вдоль затвора. Светлый слой – кремний, темный – SiO2. Хорошо видно, что боковая изоляция намного толще, чем подзатворный диэлектрик. Разница на картинках (а) и (б) связано с различными методами изготовления изоляции и играет важную роль в радиационной стойкости транзистора.

Рисунок 3. Разрез МОП структур с боковой изоляцией типа LOCOS и STI.

В толстом изолирующем диэлектрике электрическое поле невелико, и разделение электронно-дырочных пар проходит плохо. В подзатворном диэлектрике поле большое, однако сам оксид тонкий. А вот в переходной области все хорошо (то есть все плохо): оксид достаточно толстый, чтобы в нем накапливался заряд, а электрическое поле достаточно большое, чтобы дырки и электроны эффективно разделялись.

Транзистор в микросхеме можно представить как суперпозицию собственно транзистора и двух расположенных с боков паразитных транзисторов, у которых роль подзатворного диэлектрика играет переходный слой между подзатворным диэлектриком основного транзистора и боковой изоляцией. Пороговое напряжение основного транзистора при воздействии дозы излучения меняется мало, а вот порог паразитных структур может уменьшаться до нуля, создавая каналы протекания тока, не управляемые основным затвором. Через эти каналы ток свободно течет из стока в исток – что и называется током утечки.

Утечки, как я говорил выше, приводят к росту тока потребления схемы (что может быть неприемлемо в космическом аппарате, где доступная мощность весьма скромна) и даже к функциональным отказам. Например, распространенная проблема флэш-памяти связана не с запоминающими элементами, а с генератором высокого напряжения, используемым для перезаписи. В этом генераторе есть ключи, которые из-за утечек перестают полностью закрываться, без чего невозможно формирование напряжения, достаточного для перезаписи памяти.

Одиночные эффекты возникают при попадании в транзистор одной ионизирующей частицы (протона, нейтрона или ядра более тяжелого элемента) и делятся на «мягкие» (сбои) и «жесткие» (отказы), Последние – достаточно редкое явление, характерное для мощных схем и малоизученное. Варианты отказов включают пробой подзатворного диэлектрика и прогорание транзистора из-за возникновения проводящего канала между стоком и истоком, а также тиристорный эффект, на котором я остановлюсь подробнее чуть позже.

У «мягких» сбоев есть два основных механизма – первичная и вторичная ионизация. Первая характерна для тяжелых заряженных частиц (ТЗЧ; ими в данном контексте называют все ядра тяжелее протона), вторая – для протонов и нейтронов. Пролетая через микросхему, частица тормозится из-за взаимодействия с кристаллической решеткой и отдает ей часть своей энергии (этот процесс можно сравнить с нагревом при трении).

Энергия, выделившаяся при пролете частицы, ионизирует атомы кремния. В нормальных условиях подавляющее большинство оторванных от атомов электронов возвращается обратно, но если ионизация происходит вблизи сильного электрического поля, оно может разделить электроны и дырки. Механизм сходен с тем, что происходит при накоплении дозы, но носители заряда не могут накапливаться в кремнии, и длительность одиночных эффектов измеряется не в месяцах, а в пикосекундах.

Сильное электрическое поле в кремнии – это истоковый pn-переход закрытого транзистора, разделение заряда вблизи которого приводит к тому, что носители заряда одного знака попадают в лини земли/питания, а второго – на сток транзистора. С точки зрения внешнего наблюдателя результат процесса выглядит как импульс тока с передним фронтом в несколько десятков пикосекунд и задним – в несколько сотен. Точные параметры импульса зависят от многих факторов, в том числе технологии изготовлении микросхемы, угла падения частицы и т.д.

Если проинтегрировать получившийся импульс тока по времени, мы получим полный заряд, выделившийся в результате попадания ТЗЧ. Минимальный заряд, приводящий к сбою, называется критическим зарядом сбоя (critical charge). Критический заряд зависит от параметров как пораженной схемы, так и падающей частицы; кроме того, его очень сложно измерить экспериментально, поэтому он обычно применяется для моделирования взаимодействия схемы и частицы и для сравнительного моделирования сбоеустойчивости разных схем.

Энерговыделение принято выражать при помощи линейной передачи энергии (ЛПЭ; английский термин – Linear Energy Transfer, LET), измеряемой в МэВ×см2/мг или точнее, в (МэВ/(мг/см3))/см. Одна единица ЛПЭ – это количество энергии выделяемое пролетающей частицей за сантиметр пролетаемого расстояния на единицу плотности вещества, через которое летит частица. Определение на первый взгляд весьма запутанное, но выбранная именно таким образом единица измерения обладает несколькими важными достоинствами: во-первых, численное значение относительно просто измерить экспериментально; во-вторых, в-третьих, применяемые на практике значения обычно укладываются в диапазон от единицы до сотни.

ЛПЭ – величина не постоянная, то есть параметры пролетающей частицы у крышки корпуса микросхемы, на границе кристалла и непосредственно у транзистора под многочисленными слоями будут разными. Из этого, однако, не следует, что более толстый корпус может помочь – зависимость ЛПЭ от дистанции, пройденной в кремнии, обычно имеет максимум на некоторой глубине (так называемый Брэгговский пик). Подобный эффект используется в радиационной терапии и в некоторых операциях изготовления микросхем: параметры имплантируемых ионов подбираются таким образом, чтобы они останавливались на определенной глубине и создавали на глубине слой с большим уровнем легирования.

Протоны и нейтроны имеют очень маленькую ЛПЭ (приблизительно 0,01 МэВ×см2/мг), однако при пролете высокоэнергетического протона/нейтрона через кремний существует вероятность ядерной реакции, продуктами которой являются ионы с коротким пробегом, но большой ЛПЭ (до 15 МэВ×см2/мг). В технологических процессах с не алюминиевой, а медной металлизацией (180 нм и ниже), кроме того, описаны механизмы взаимодействия протонов с вольфрамом, применяемым для контактов первого уровня (и расположенным, таким образом, прямо над чувствительными pn-переходами). ЛПЭ продуктов таких реакций может достигать 30 МэВ×см2/мг.

Характерные минимальные ЛПЭ падающих частиц, приводящие к сбою – в пределах десятки для технологий с проектными нормами 500-250 нм, и порядка единицы для суб-100 нм технологий, в которых критический заряд может быть так мал, что даже первичная ионизация от протонов и нейтронов способна вызвать сбой. Кроме того, маленький критический заряд сбоя приводит к тому, что достаточный заряд может разделиться при пролете частицы не только через обратно смещенный стоковый pn-переход, но и через несмещенный истоковый, что существенно увеличивает уязвимую площадь на кристалле.

Короткий импульс тока воспринимается микросхемой как импульсная помеха, и, если его амплитуда достаточно велика, он может привести к переключению элемента, стоящего за пораженным транзистором – это и есть радиационно-индуцированный сбой. Комбинационные и аналоговые схемы в момент прохождения импульса тока выдает неверный результат, а запоминающие элементы переключаются насовсем. Таким образом, наиболее уязвимой частью микропроцессора является кэш-память: ее на кристалле много, и сбои в ней не проходят сами по себе.

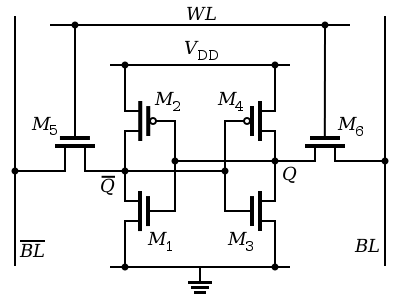

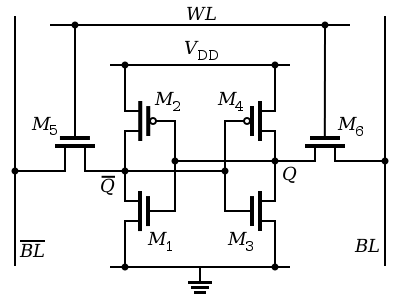

Рисунок 4. Схема шеститранзисторного запоминающего элемента.

Для примера удобнее всего описать механизм сбоя в шеститранзисторной ячейке статической памяти (простейшем из используемых запоминающих элементов). Запоминающий элемент состоит из двух соединенных положительными обратными связями инверторов (M1-M2 и M3-M4) и двух ключей (M5-M6). В режиме хранения два транзистора закрыты, а два открыты, и на выходах инверторов противоположные значения. Пусть для определенности открыты транзисторы M1 и M4. При попадании ТЗЧ в сток закрытого транзистора (M2 или M3) возникает импульс ионизационного тока, и в ячейке начинаются два процесса: срабатывание положительной обратной связи и рассасывание индуцированного заряда. Эти процессы являются независимыми (их временные константы определяются разными транзисторами) и конкурирующими (эффекты от воздействия процессов противоположны).

Пусть попадание произошло в транзистор закрытый транзистор M2, на стоке которого в результате появился импульс тока. Транзистор М1 в этот момент полностью открыт и имеет маленькое сопротивление, то есть индуцированный ТЗЧ ток через него проходит в землю. Однако емкость узла nQ может быть достаточно большой для того, чтобы его потенциал этого узла вырос на значительное время. Возрастание потенциала узла nQ приводит к переключению второго инвертора (M3-M4). При этом выходное напряжение второго инвертора меняется таким образом, что сопротивление транзистора M1 растет, а транзистор M2 приоткрывается. Если этот процесс происходит дольше, чем процесс рассасывания заряда, то запоминающий элемент переключается, и в нем оказывается записано неверное значение – это и есть радиационно-индуцированный сбой (single event upset, SEU).

Сбои в комбинационной логике проходят несколько проще сбоев в запоминающих элементах – здесь нет обратной связи, и повышение потенциала пораженного узла напрямую передается на следующий каскад. В случае, если амплитуда напряжения достаточно велика, следующий каскад переключается – и дальше по схеме распространяется переходный процесс (single event transient, «иголка» на российском жаргоне). Со сбоями в комбинационной логике связаны дополнительные эффекты, влияющие на то, как схема реагирует на сбой. С одной стороны, есть эффект логического маскирования: не все изменения входных состояний влияют на выход схемы (например, переключение одного из входов элемента «2ИНЕ» не влияет на выход, если на втором входе логический ноль). С другой стороны, если выход пораженной схемы нагружен несколькими элементами, то сбой попадет на входы каждого из них (представьте себе сбой в самом начале дерева тактовых сигналов). И наконец, временное маскирование: на выходе любой комбинационной схемы стоит триггер, запоминающий значения в определенные промежутки времени. При работе на малых частотах вероятность того, что импульс целиком придется на время, в которое триггер ничего не запоминает, довольно велика, однако с ростом частоты длительность импульса (от нескольких сотен пикосекунд до наносекунды) оказывается сравнима с периодом тактового сигнала, и на больших тактовых частотах интенсивность значащих сбоев в комбинационной логике может быть даже выше интенсивности сбоев в запоминающих элементах (кстати, в стоящих на выходах комбинационных схем триггерах тоже могут быть сбои).

Эффективный диаметр области сбора заряда от попадания ТЗЧ – порядка двух микрон, что существенно больше размеров логических элементов в современных технологиях. Поэтому от попадания одной частицы могут сбиться одновременно несколько элементов, например ячеек кэш-памяти. В технологии 65 нм «несколько» могут быть десятью, что создает существенные сложности в применении помехоустойчивых кодов и заставляет серьезно модифицировать топологию элементов микросхемы.

При попадании ТЗЧ в транзистор может возникнуть не только однократный сбой, но и условно-жесткий отказ, вызванный тиристорным эффектом («защелка» или latchup на профессиональном жаргоне). На рисунке показано сечение инвертора, выполненного по объемной КМОП технологии, и показаны паразитные элементы, сформированные слоями микросхемы.

Рисунок 5. Сечение КМОП инвертора с показанными паразитными структурами, участвующими в тиристорном эффекте.

Видно, что два биполярных транзистора образуют pnpn-структуру (исток-карман-подложка-исток), известную под названием тиристор. ВАХ тиристора показана на рисунке и характерна тем, что имеет нелинейность, то есть при достижении некоего прямого смещения на структуре ее сопротивление резко падает, а ток, соответственно, растет.

Рисунок 6. Вольт-амперная характеристика тиристора.

При попадании ТЗЧ индуцированный импульс тока может привести к открыванию биполярных транзисторов и попаданию паразитной тиристорной структуры в низкоомное состояние. Результатом будет формирование короткого замыкания между землей и питанием, потеря работоспособности пораженного элемента и резкий рост тока потребления, способный привести к «выгоранию» пораженного элемента и функциональному отказу. Тиристорный эффект относят к условно-жестким, потому что его воздействие можно остановить при помощи сброса питания с пораженной микросхемы. Эта мера, однако, весьма неудобна и, при большом количестве отказов, неприменима; тиристорный эффект является одной из основных головных болей разработчиков радиоэлектронной аппаратуры для космоса, особенно если они по каким-то причинам используют коммерческие микросхемы вместо специально разработанных.

Как бороться с тиристорным эффектом? Можно разнести транзисторы дальше друг от друга, таким образом увеличив длину базы транзистора Q2, но этот вариант нежелателен из-за снижения плотности упаковки кристалла. Можно увеличить уровни легирования подложки и кармана, снизив подвижность носителей заряда – но это снизит скорость работы и основных транзисторов тоже.

Самый удобный вариант – минимизировать базовые сопротивления паразитных транзисторов (Rs и Rw). Чем меньше сопротивление, тем меньше открывается эмиттерный pn-переход при протекании тока, и тем меньше вероятность включения биполярного умножения заряда. Технологически уменьшение базовых сопротивлений означает обеспечение хороших контактов к подложке и карману или создание транзисторов в выращенном поверх высоколегированной подложки низколегированном эпитаксиальном слое.

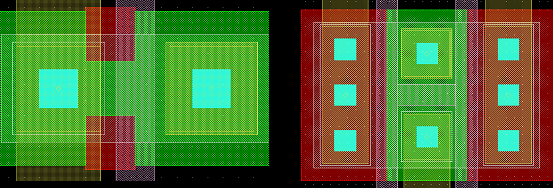

Наиболее надежный способ минимизации сопротивления контактов к карману и подложке в традиционной КМОП технологии – окружение транзистора кольцевым контактом (так называемые «охранные кольца» или guard rings). В зависимости от технологии и строгости требований охранных колец может быть от одного до четырех (например, в схемах ввода-вывода, где из-за протекания больших рабочих токов тиристорный эффект возможен и по не связанным с радиацией причинам, в том числе из-за электростатического пробоя). Очевидным недостатком охранных колец является серьезный рост площади элементов (до нескольких раз), то есть даже без учета других методов повышения радиационной стойкости на кристалл поместится намного меньше транзисторов, чем на аналогичный нерадиационностойкий.

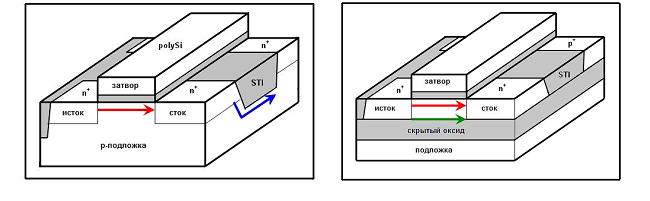

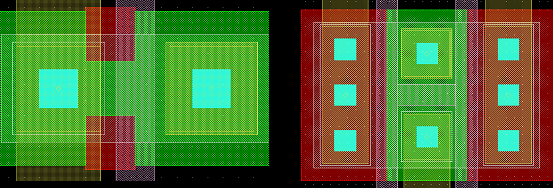

Еще один вариант защиты от тиристорного эффекта – полная электрическая изоляция каждого транзистора в схеме, реализуемая в технологии «кремний на изоляторе» (КНИ, по-английски Silicon on Insulator или SOI). Исторически важной разновидностью КНИ является кремний на сапфире (КНС, SOS), в котором отдельные кремниевые островки выращиваются на поверхности монокристалла сапфира, но при переходе к малым проектным нормам от него почти повсеместно отказались по технологическим причинам, и сейчас под кремнием на изоляторе практически всегда подразумевается кремний на SiO2. Существуют разные технологии создания таких пластин, но все они сводятся к тому, что на кремниевой подложке формируется относительно толстый слой SiO2 (называемый скрытым или захороненным оксидом или buried oxide), а поверх него – сплошной слой кремния, в котором и изготавливаются транзисторы, разделяемые обычной боковой изоляцией, доходящей до скрытого оксида. Сравнение сечений МОП-транзисторов, выполненных на объемной и КНИ технологии, показано на рисунке NUM. Там же показаны pn-переходы, вблизи которых происходит разделение электронно-дырочных пар.

Рисунок 7. Сечение МОП-транзисторов, выполненных на объемной и КНИ технологии. Показана генерация заряда при попадании тяжелой заряженной частицы.

Полное отсутствие в КНИ тиристорного эффекта привело к тому, что даже в среде специалистов-разработчиков аппаратуры до сих пор распространено убеждение «КНИ равно радиационная стойкость», но на самом деле это не так. Имея неоспоримое преимущество в стойкости к одному эффекту (и то выражающееся главным образом в экономии площади на охранных кольцах), КНИ может иметь существенно меньшую стойкость как к полной поглощенной дозе, так и к одиночным сбоям.

Электрическая изоляция транзисторов позволяет полностью избавиться от межтранзисторных утечек, но утечка по боковым граням никуда не девается и, более того, наличие скрытого оксида приводит к возникновению еще двух переходных зон между оксидами – и на границе самого скрытого оксида тоже может образоваться паразитный канал. Тем не менее, дозовая стойкость КНИ схем сравнима с аналогичными объемными, и большинство методов ее повышения в объемной технологии применима и к КНИ.

Рисунок 8. Сравнение мест возникновения токов утечки в объемном и КНИ МОП транзисторах.

С точки зрения одиночных эффектов КНИ технология имеет важное преимущество перед объемной: область, из которой происходит диффузионный сбор заряда, ограничена скрытым оксидом и приблизительно на порядок меньше, чем в аналогичной объемной технологии – то есть и сечение сбоев в области насыщения будет на порядок меньше (а также намного короче задний фронт импульса). К сожалению, в коммерческих КНИ схемах это достоинство полностью перечеркивается тем, что пороговая ЛПЭ сбоя так мала, что интенсивность сбоев оказывается у КНИ выше – за счет большого количества частиц с малыми ЛПЭ, которые не сбивают транзисторы объемной технологии, но сбивают КНИ транзисторы. Причина этого – паразитный биполярный эффект. Вы могли заметить из рисунков, что, если потенциал подзатворной области объемных транзисторов совпадает с потенциалом подложки или кармана, то потенциал подзатворной области КНИ МОП транзистора ничем не контролируется. При попадании ТЗЧ в подзатворную область в ней может накапливаться заряд, достаточный для существенного повышения потенциала. Подзатворная область, ограниченная сверху, снизу и с боков диэлектриком, а с оставшихся двух сторон – pn-переходами, в этой ситуации играет роль емкости, заряжаемой индуцированным ТЗЧ током. Повышение потенциала подзатворной области приводит к открыванию истокового pn-перехода. Дальше в МОП-транзисторе включается паразитный биполярный транзистор, который усиливает индуцированный ТЗЧ импульс тока в соответствующее число раз (коэффициент усиления подобных паразитных структур может быть от нескольких единиц до приблизительно десятки). Биполярное умножение приводит к тому, что критический заряд сбоя элемента снижается в несколько раз, и с ним – пороговая ЛПЭ сбоя, что делает КНИ КМОП схемы гораздо менее сбоеустойчивыми, чем аналогичные объемные.

Можно ли избавиться от паразитного биполярного эффекта? Конечно, нужно только сделать так, чтобы потенциал подзатворной области находился под контролем. Варианта два – сделать слой кремния достаточно тонким для того, чтобы он весь стал каналом транзистора (это называется полностью обедненный КНИ или full depleted SOI), или создать контакты к подзатворной области. Контакты бывают двух типов: независимые и привязывающие потенциал подзатворной области к потенциалу истока.

Рисунок 9. Разновидности контактов к подзатворной области КНИ МОП транзистора. Зеленым показано n-легирование, красным – p-легирование.

Главное достоинство контакта, связывающего подзатворную область с истоком – компактность, главный недостаток – невозможность использования для некоторых включений (например, в проходном ключе). Независимые контакты могут быть использованы где угодно, но их площадь сравнима с площадью самого транзистора, поэтому их ставят только там, где это действительно необходимо. Кроме того, контакты обоих типов обладают еще одним полезным свойством – они перекрывают места образования паразитных каналов и позволяют, таким образом, повысить стойкость микросхемы к полной поглощенной дозе.

Показанные выше приемы позволяют обеспечить КНИ технологии сравнимые показатели стойкости к полной дозе и меньшее на порядок сечение насыщения одиночных сбоев, но пороговые ЛПЭ сбоя при этом все еще достаточно малы для того, чтобы микросхема, оказавшаяся на орбите, сбивалась часто. Уменьшить частоту одиночных сбоев можно при помощи схемотехнических и системотехнических методов, но это тема для отдельной статьи (или сотни диссертаций).

Два ядра ARMv7 с тактовой частотой 1,3 ГГц

Оперативная память – 1 Гбайт.

Технологический процесс с проектными нормами 150 нм.

Одно ядро PowerPC с тактовой частотой 200 МГц.

Оперативная память – 256 Мбайт.

Сверху – параметры центрального процессора iPhone5, внизу – марсохода Curiosity. Бортовой компьютер марсохода стоит приблизительно в двести раз дороже нового айфона. Почему так? Центральный процессор космического аппарата должен быть устойчивым к воздействию радиации. На Хабре уже была хорошая обзорная статья о космической электронике, а я постараюсь подробнее рассказать о физических принципах и эффектах, стоящих за сбоями и отказами в космосе.

Рисунок 1. Стоимость одноплатных компьютеров RAD компании BAE Systems измеряется в сотнях тысяч долларов.

Основные источники радиации – Солнце и звезды. Собственное светило снабжает нас протонами и электронами; от остальных звезд летит все подряд, включая, например, ядра тяжелых элементов. Обитателей Земли от радиации защищает магнитное поле, собирающее пролетающие частицы в радиационные пояса земли (также называемые поясами ван Аллена), и атмосфера, задерживающая то, что остаётся. Они же – серьезная проблема для космических аппаратов, так что время, проводимое ими в радиационных поясах, стараются минимизировать.

Рисунок 2. Радиационные пояса Земли.

Что происходит, когда микросхема попадает в космос? Основные эффекты – накопление полной поглощенной дозы (total ionizing dose, TID), эффекты, связанные с воздействием одиночных ионизирующих частиц (Single Event Effects, SEE), и эффекты смещения (displacement damage), когда прилетающие частицы выбивают атомы с их мест в кристаллической решетке.

Полная поглощенная доза излучения обуславливает дрейф некоторых характеристик микросхемы, который способен вызвать отказ, как параметрические, так и функциональные. Наиболее важные механизмы различаются от технологии к технологии; для современных микросхем актуальны радиационно-индуцированные токи утечки, а в старых технологиях важную роль играл сдвиг порогового напряжения транзистора.

Под действием ионизирующего излучения в микросхеме происходит образование электронно-дырочных пар. Эти пары в нормальных условиях достаточно быстро рекомбинируют (то есть оторвавшийся электрон захватывается атомом обратно), однако в электрическом поле дырки и электроны могут разделяться (потому что заряды противоположного знака движутся в поле в разные стороны). Основной изолятор, используемый в кремниевых микросхемах – диоксид кремния (SiO2). Подвижность электронов и дырок в SiO2 различается на несколько порядков, поэтому электроны достаточно быстро выносятся в кремний, а дырки могут накапливаться в оксиде и на границе оксида с кремнием.

Если заряд накопился в подзатворном диэлектрике МОП-транзистора, он будет влиять на его работу как дополнительно приложенное положительное напряжение (или как сдвиг порогового напряжения). В результате n-канальный транзистор будет приоткрываться. В старых технологиях с толстыми подзатворными диэлектриками сдвиг порогового напряжения n-канальных транзисторов мог быть достаточно большим для того, чтобы транзистор полностью переставал закрываться, что естественным образом приводило к потере работоспособности схемы. Впрочем, уменьшение порогового напряжения еще раньше приводило к тому, что общий ток потребления микросхемы превышал допустимый уровень из-за утечек.

В современных технологиях толщина подзатворного диэлектрика составляет единицы нанометров, и в них попросту не может накопиться достаточно дырок для того, чтобы пороговое напряжение транзистора серьезно изменилось. Поэтому главную роль играет накопление заряда в других имеющихся в микросхеме оксидах, а именно в боковой изоляции, разделяющей соседние транзисторы, и на ее границе в подзатворным диэлектриком. На рисунке показано сечение МОП-транзистора вдоль затвора. Светлый слой – кремний, темный – SiO2. Хорошо видно, что боковая изоляция намного толще, чем подзатворный диэлектрик. Разница на картинках (а) и (б) связано с различными методами изготовления изоляции и играет важную роль в радиационной стойкости транзистора.

Рисунок 3. Разрез МОП структур с боковой изоляцией типа LOCOS и STI.

В толстом изолирующем диэлектрике электрическое поле невелико, и разделение электронно-дырочных пар проходит плохо. В подзатворном диэлектрике поле большое, однако сам оксид тонкий. А вот в переходной области все хорошо (то есть все плохо): оксид достаточно толстый, чтобы в нем накапливался заряд, а электрическое поле достаточно большое, чтобы дырки и электроны эффективно разделялись.

Транзистор в микросхеме можно представить как суперпозицию собственно транзистора и двух расположенных с боков паразитных транзисторов, у которых роль подзатворного диэлектрика играет переходный слой между подзатворным диэлектриком основного транзистора и боковой изоляцией. Пороговое напряжение основного транзистора при воздействии дозы излучения меняется мало, а вот порог паразитных структур может уменьшаться до нуля, создавая каналы протекания тока, не управляемые основным затвором. Через эти каналы ток свободно течет из стока в исток – что и называется током утечки.

Утечки, как я говорил выше, приводят к росту тока потребления схемы (что может быть неприемлемо в космическом аппарате, где доступная мощность весьма скромна) и даже к функциональным отказам. Например, распространенная проблема флэш-памяти связана не с запоминающими элементами, а с генератором высокого напряжения, используемым для перезаписи. В этом генераторе есть ключи, которые из-за утечек перестают полностью закрываться, без чего невозможно формирование напряжения, достаточного для перезаписи памяти.

Одиночные эффекты возникают при попадании в транзистор одной ионизирующей частицы (протона, нейтрона или ядра более тяжелого элемента) и делятся на «мягкие» (сбои) и «жесткие» (отказы), Последние – достаточно редкое явление, характерное для мощных схем и малоизученное. Варианты отказов включают пробой подзатворного диэлектрика и прогорание транзистора из-за возникновения проводящего канала между стоком и истоком, а также тиристорный эффект, на котором я остановлюсь подробнее чуть позже.

У «мягких» сбоев есть два основных механизма – первичная и вторичная ионизация. Первая характерна для тяжелых заряженных частиц (ТЗЧ; ими в данном контексте называют все ядра тяжелее протона), вторая – для протонов и нейтронов. Пролетая через микросхему, частица тормозится из-за взаимодействия с кристаллической решеткой и отдает ей часть своей энергии (этот процесс можно сравнить с нагревом при трении).

Энергия, выделившаяся при пролете частицы, ионизирует атомы кремния. В нормальных условиях подавляющее большинство оторванных от атомов электронов возвращается обратно, но если ионизация происходит вблизи сильного электрического поля, оно может разделить электроны и дырки. Механизм сходен с тем, что происходит при накоплении дозы, но носители заряда не могут накапливаться в кремнии, и длительность одиночных эффектов измеряется не в месяцах, а в пикосекундах.

Сильное электрическое поле в кремнии – это истоковый pn-переход закрытого транзистора, разделение заряда вблизи которого приводит к тому, что носители заряда одного знака попадают в лини земли/питания, а второго – на сток транзистора. С точки зрения внешнего наблюдателя результат процесса выглядит как импульс тока с передним фронтом в несколько десятков пикосекунд и задним – в несколько сотен. Точные параметры импульса зависят от многих факторов, в том числе технологии изготовлении микросхемы, угла падения частицы и т.д.

Если проинтегрировать получившийся импульс тока по времени, мы получим полный заряд, выделившийся в результате попадания ТЗЧ. Минимальный заряд, приводящий к сбою, называется критическим зарядом сбоя (critical charge). Критический заряд зависит от параметров как пораженной схемы, так и падающей частицы; кроме того, его очень сложно измерить экспериментально, поэтому он обычно применяется для моделирования взаимодействия схемы и частицы и для сравнительного моделирования сбоеустойчивости разных схем.

Энерговыделение принято выражать при помощи линейной передачи энергии (ЛПЭ; английский термин – Linear Energy Transfer, LET), измеряемой в МэВ×см2/мг или точнее, в (МэВ/(мг/см3))/см. Одна единица ЛПЭ – это количество энергии выделяемое пролетающей частицей за сантиметр пролетаемого расстояния на единицу плотности вещества, через которое летит частица. Определение на первый взгляд весьма запутанное, но выбранная именно таким образом единица измерения обладает несколькими важными достоинствами: во-первых, численное значение относительно просто измерить экспериментально; во-вторых, в-третьих, применяемые на практике значения обычно укладываются в диапазон от единицы до сотни.

ЛПЭ – величина не постоянная, то есть параметры пролетающей частицы у крышки корпуса микросхемы, на границе кристалла и непосредственно у транзистора под многочисленными слоями будут разными. Из этого, однако, не следует, что более толстый корпус может помочь – зависимость ЛПЭ от дистанции, пройденной в кремнии, обычно имеет максимум на некоторой глубине (так называемый Брэгговский пик). Подобный эффект используется в радиационной терапии и в некоторых операциях изготовления микросхем: параметры имплантируемых ионов подбираются таким образом, чтобы они останавливались на определенной глубине и создавали на глубине слой с большим уровнем легирования.

Протоны и нейтроны имеют очень маленькую ЛПЭ (приблизительно 0,01 МэВ×см2/мг), однако при пролете высокоэнергетического протона/нейтрона через кремний существует вероятность ядерной реакции, продуктами которой являются ионы с коротким пробегом, но большой ЛПЭ (до 15 МэВ×см2/мг). В технологических процессах с не алюминиевой, а медной металлизацией (180 нм и ниже), кроме того, описаны механизмы взаимодействия протонов с вольфрамом, применяемым для контактов первого уровня (и расположенным, таким образом, прямо над чувствительными pn-переходами). ЛПЭ продуктов таких реакций может достигать 30 МэВ×см2/мг.

Характерные минимальные ЛПЭ падающих частиц, приводящие к сбою – в пределах десятки для технологий с проектными нормами 500-250 нм, и порядка единицы для суб-100 нм технологий, в которых критический заряд может быть так мал, что даже первичная ионизация от протонов и нейтронов способна вызвать сбой. Кроме того, маленький критический заряд сбоя приводит к тому, что достаточный заряд может разделиться при пролете частицы не только через обратно смещенный стоковый pn-переход, но и через несмещенный истоковый, что существенно увеличивает уязвимую площадь на кристалле.

Короткий импульс тока воспринимается микросхемой как импульсная помеха, и, если его амплитуда достаточно велика, он может привести к переключению элемента, стоящего за пораженным транзистором – это и есть радиационно-индуцированный сбой. Комбинационные и аналоговые схемы в момент прохождения импульса тока выдает неверный результат, а запоминающие элементы переключаются насовсем. Таким образом, наиболее уязвимой частью микропроцессора является кэш-память: ее на кристалле много, и сбои в ней не проходят сами по себе.

Рисунок 4. Схема шеститранзисторного запоминающего элемента.

Для примера удобнее всего описать механизм сбоя в шеститранзисторной ячейке статической памяти (простейшем из используемых запоминающих элементов). Запоминающий элемент состоит из двух соединенных положительными обратными связями инверторов (M1-M2 и M3-M4) и двух ключей (M5-M6). В режиме хранения два транзистора закрыты, а два открыты, и на выходах инверторов противоположные значения. Пусть для определенности открыты транзисторы M1 и M4. При попадании ТЗЧ в сток закрытого транзистора (M2 или M3) возникает импульс ионизационного тока, и в ячейке начинаются два процесса: срабатывание положительной обратной связи и рассасывание индуцированного заряда. Эти процессы являются независимыми (их временные константы определяются разными транзисторами) и конкурирующими (эффекты от воздействия процессов противоположны).

Пусть попадание произошло в транзистор закрытый транзистор M2, на стоке которого в результате появился импульс тока. Транзистор М1 в этот момент полностью открыт и имеет маленькое сопротивление, то есть индуцированный ТЗЧ ток через него проходит в землю. Однако емкость узла nQ может быть достаточно большой для того, чтобы его потенциал этого узла вырос на значительное время. Возрастание потенциала узла nQ приводит к переключению второго инвертора (M3-M4). При этом выходное напряжение второго инвертора меняется таким образом, что сопротивление транзистора M1 растет, а транзистор M2 приоткрывается. Если этот процесс происходит дольше, чем процесс рассасывания заряда, то запоминающий элемент переключается, и в нем оказывается записано неверное значение – это и есть радиационно-индуцированный сбой (single event upset, SEU).

Сбои в комбинационной логике проходят несколько проще сбоев в запоминающих элементах – здесь нет обратной связи, и повышение потенциала пораженного узла напрямую передается на следующий каскад. В случае, если амплитуда напряжения достаточно велика, следующий каскад переключается – и дальше по схеме распространяется переходный процесс (single event transient, «иголка» на российском жаргоне). Со сбоями в комбинационной логике связаны дополнительные эффекты, влияющие на то, как схема реагирует на сбой. С одной стороны, есть эффект логического маскирования: не все изменения входных состояний влияют на выход схемы (например, переключение одного из входов элемента «2ИНЕ» не влияет на выход, если на втором входе логический ноль). С другой стороны, если выход пораженной схемы нагружен несколькими элементами, то сбой попадет на входы каждого из них (представьте себе сбой в самом начале дерева тактовых сигналов). И наконец, временное маскирование: на выходе любой комбинационной схемы стоит триггер, запоминающий значения в определенные промежутки времени. При работе на малых частотах вероятность того, что импульс целиком придется на время, в которое триггер ничего не запоминает, довольно велика, однако с ростом частоты длительность импульса (от нескольких сотен пикосекунд до наносекунды) оказывается сравнима с периодом тактового сигнала, и на больших тактовых частотах интенсивность значащих сбоев в комбинационной логике может быть даже выше интенсивности сбоев в запоминающих элементах (кстати, в стоящих на выходах комбинационных схем триггерах тоже могут быть сбои).

Эффективный диаметр области сбора заряда от попадания ТЗЧ – порядка двух микрон, что существенно больше размеров логических элементов в современных технологиях. Поэтому от попадания одной частицы могут сбиться одновременно несколько элементов, например ячеек кэш-памяти. В технологии 65 нм «несколько» могут быть десятью, что создает существенные сложности в применении помехоустойчивых кодов и заставляет серьезно модифицировать топологию элементов микросхемы.

При попадании ТЗЧ в транзистор может возникнуть не только однократный сбой, но и условно-жесткий отказ, вызванный тиристорным эффектом («защелка» или latchup на профессиональном жаргоне). На рисунке показано сечение инвертора, выполненного по объемной КМОП технологии, и показаны паразитные элементы, сформированные слоями микросхемы.

Рисунок 5. Сечение КМОП инвертора с показанными паразитными структурами, участвующими в тиристорном эффекте.

Видно, что два биполярных транзистора образуют pnpn-структуру (исток-карман-подложка-исток), известную под названием тиристор. ВАХ тиристора показана на рисунке и характерна тем, что имеет нелинейность, то есть при достижении некоего прямого смещения на структуре ее сопротивление резко падает, а ток, соответственно, растет.

Рисунок 6. Вольт-амперная характеристика тиристора.

При попадании ТЗЧ индуцированный импульс тока может привести к открыванию биполярных транзисторов и попаданию паразитной тиристорной структуры в низкоомное состояние. Результатом будет формирование короткого замыкания между землей и питанием, потеря работоспособности пораженного элемента и резкий рост тока потребления, способный привести к «выгоранию» пораженного элемента и функциональному отказу. Тиристорный эффект относят к условно-жестким, потому что его воздействие можно остановить при помощи сброса питания с пораженной микросхемы. Эта мера, однако, весьма неудобна и, при большом количестве отказов, неприменима; тиристорный эффект является одной из основных головных болей разработчиков радиоэлектронной аппаратуры для космоса, особенно если они по каким-то причинам используют коммерческие микросхемы вместо специально разработанных.

Как бороться с тиристорным эффектом? Можно разнести транзисторы дальше друг от друга, таким образом увеличив длину базы транзистора Q2, но этот вариант нежелателен из-за снижения плотности упаковки кристалла. Можно увеличить уровни легирования подложки и кармана, снизив подвижность носителей заряда – но это снизит скорость работы и основных транзисторов тоже.

Самый удобный вариант – минимизировать базовые сопротивления паразитных транзисторов (Rs и Rw). Чем меньше сопротивление, тем меньше открывается эмиттерный pn-переход при протекании тока, и тем меньше вероятность включения биполярного умножения заряда. Технологически уменьшение базовых сопротивлений означает обеспечение хороших контактов к подложке и карману или создание транзисторов в выращенном поверх высоколегированной подложки низколегированном эпитаксиальном слое.

Наиболее надежный способ минимизации сопротивления контактов к карману и подложке в традиционной КМОП технологии – окружение транзистора кольцевым контактом (так называемые «охранные кольца» или guard rings). В зависимости от технологии и строгости требований охранных колец может быть от одного до четырех (например, в схемах ввода-вывода, где из-за протекания больших рабочих токов тиристорный эффект возможен и по не связанным с радиацией причинам, в том числе из-за электростатического пробоя). Очевидным недостатком охранных колец является серьезный рост площади элементов (до нескольких раз), то есть даже без учета других методов повышения радиационной стойкости на кристалл поместится намного меньше транзисторов, чем на аналогичный нерадиационностойкий.

Еще один вариант защиты от тиристорного эффекта – полная электрическая изоляция каждого транзистора в схеме, реализуемая в технологии «кремний на изоляторе» (КНИ, по-английски Silicon on Insulator или SOI). Исторически важной разновидностью КНИ является кремний на сапфире (КНС, SOS), в котором отдельные кремниевые островки выращиваются на поверхности монокристалла сапфира, но при переходе к малым проектным нормам от него почти повсеместно отказались по технологическим причинам, и сейчас под кремнием на изоляторе практически всегда подразумевается кремний на SiO2. Существуют разные технологии создания таких пластин, но все они сводятся к тому, что на кремниевой подложке формируется относительно толстый слой SiO2 (называемый скрытым или захороненным оксидом или buried oxide), а поверх него – сплошной слой кремния, в котором и изготавливаются транзисторы, разделяемые обычной боковой изоляцией, доходящей до скрытого оксида. Сравнение сечений МОП-транзисторов, выполненных на объемной и КНИ технологии, показано на рисунке NUM. Там же показаны pn-переходы, вблизи которых происходит разделение электронно-дырочных пар.

Рисунок 7. Сечение МОП-транзисторов, выполненных на объемной и КНИ технологии. Показана генерация заряда при попадании тяжелой заряженной частицы.

Полное отсутствие в КНИ тиристорного эффекта привело к тому, что даже в среде специалистов-разработчиков аппаратуры до сих пор распространено убеждение «КНИ равно радиационная стойкость», но на самом деле это не так. Имея неоспоримое преимущество в стойкости к одному эффекту (и то выражающееся главным образом в экономии площади на охранных кольцах), КНИ может иметь существенно меньшую стойкость как к полной поглощенной дозе, так и к одиночным сбоям.

Электрическая изоляция транзисторов позволяет полностью избавиться от межтранзисторных утечек, но утечка по боковым граням никуда не девается и, более того, наличие скрытого оксида приводит к возникновению еще двух переходных зон между оксидами – и на границе самого скрытого оксида тоже может образоваться паразитный канал. Тем не менее, дозовая стойкость КНИ схем сравнима с аналогичными объемными, и большинство методов ее повышения в объемной технологии применима и к КНИ.

Рисунок 8. Сравнение мест возникновения токов утечки в объемном и КНИ МОП транзисторах.

С точки зрения одиночных эффектов КНИ технология имеет важное преимущество перед объемной: область, из которой происходит диффузионный сбор заряда, ограничена скрытым оксидом и приблизительно на порядок меньше, чем в аналогичной объемной технологии – то есть и сечение сбоев в области насыщения будет на порядок меньше (а также намного короче задний фронт импульса). К сожалению, в коммерческих КНИ схемах это достоинство полностью перечеркивается тем, что пороговая ЛПЭ сбоя так мала, что интенсивность сбоев оказывается у КНИ выше – за счет большого количества частиц с малыми ЛПЭ, которые не сбивают транзисторы объемной технологии, но сбивают КНИ транзисторы. Причина этого – паразитный биполярный эффект. Вы могли заметить из рисунков, что, если потенциал подзатворной области объемных транзисторов совпадает с потенциалом подложки или кармана, то потенциал подзатворной области КНИ МОП транзистора ничем не контролируется. При попадании ТЗЧ в подзатворную область в ней может накапливаться заряд, достаточный для существенного повышения потенциала. Подзатворная область, ограниченная сверху, снизу и с боков диэлектриком, а с оставшихся двух сторон – pn-переходами, в этой ситуации играет роль емкости, заряжаемой индуцированным ТЗЧ током. Повышение потенциала подзатворной области приводит к открыванию истокового pn-перехода. Дальше в МОП-транзисторе включается паразитный биполярный транзистор, который усиливает индуцированный ТЗЧ импульс тока в соответствующее число раз (коэффициент усиления подобных паразитных структур может быть от нескольких единиц до приблизительно десятки). Биполярное умножение приводит к тому, что критический заряд сбоя элемента снижается в несколько раз, и с ним – пороговая ЛПЭ сбоя, что делает КНИ КМОП схемы гораздо менее сбоеустойчивыми, чем аналогичные объемные.

Можно ли избавиться от паразитного биполярного эффекта? Конечно, нужно только сделать так, чтобы потенциал подзатворной области находился под контролем. Варианта два – сделать слой кремния достаточно тонким для того, чтобы он весь стал каналом транзистора (это называется полностью обедненный КНИ или full depleted SOI), или создать контакты к подзатворной области. Контакты бывают двух типов: независимые и привязывающие потенциал подзатворной области к потенциалу истока.

Рисунок 9. Разновидности контактов к подзатворной области КНИ МОП транзистора. Зеленым показано n-легирование, красным – p-легирование.

Главное достоинство контакта, связывающего подзатворную область с истоком – компактность, главный недостаток – невозможность использования для некоторых включений (например, в проходном ключе). Независимые контакты могут быть использованы где угодно, но их площадь сравнима с площадью самого транзистора, поэтому их ставят только там, где это действительно необходимо. Кроме того, контакты обоих типов обладают еще одним полезным свойством – они перекрывают места образования паразитных каналов и позволяют, таким образом, повысить стойкость микросхемы к полной поглощенной дозе.

Показанные выше приемы позволяют обеспечить КНИ технологии сравнимые показатели стойкости к полной дозе и меньшее на порядок сечение насыщения одиночных сбоев, но пороговые ЛПЭ сбоя при этом все еще достаточно малы для того, чтобы микросхема, оказавшаяся на орбите, сбивалась часто. Уменьшить частоту одиночных сбоев можно при помощи схемотехнических и системотехнических методов, но это тема для отдельной статьи (или сотни диссертаций).