Основные положения

В статье показана причинно-следственная связь между назначением сигналов печатной платы на выводы ПЛИС и маржинальной прибылью изделия. Кроме того, в статье рассматриваются возможности получения значительных конкурентных преимуществ без существенных временных и финансовых затрат.

Оглавление

Оценка степени влияния на прибыль

Процессы, ускоряющие настройку проектных ограничений

Ускорение процесса проектирования и минимизация производственных затрат

Прибыль от продукта — это последнее звено в цепочке принятии решений о возможных последствиях

Понимание факторов, препятствующих оптимизации

Организация команды разработчиков

Традиционные процессы проектирования

Инфраструктура для поддержки процессов проектирования

Доступность инструментов разработки

Существующие на сегодняшний день инструменты

Введение

Мощность, гибкость и доступность – ключевые характеристики ПЛИС, которые послужили их широкому распространению в проектах разработки печатных плат. Благодаря высокой производительности, ПЛИС способствуют быстрому выводу продукции на рынок, а значит, выступают достойной альтернативой более ресурсоемкими IC- / ASIC-решениям.

Типовой проект, реализованный на современных ПЛИС, приносит значительную экономическую и временную выгоду. В то же время часть полученной прибыли остаётся нереализованной. Основная проблема заключается в том, что в большинстве случаев гибкость и мощность ПЛИС не используются в качестве инструмента оптимизации печатной платы. Недостающее звено, наличие которого позволило бы максимизировать выгоду от гибкости ПЛИС, – анализ причинно-следственных связей, который начинается с назначения контактов на выводы ПЛИС и заканчивается получением наибольшей прибыли от использования устройства.

В этой статье рассмотрена причинно-следственная связь между назначением сигналов печатной платы на выводы ПЛИС и маржинальной прибылью изделия, а также представлены возможности получения значительных конкурентных преимуществ без существенных временных и финансовых затрат.

Оценка степени влияния на прибыль

Большинство руководителей отделов проектирования/производства будут удивлены, узнав, что каждый сигнал, поступающий к выводу ПЛИС, оказывает непосредственное влияние на маржинальную прибыль от их продукции. Анализ причинно-следственной цепочки (рис. 1) показывает, что назначение сигнала контакту ПЛИС влияет на домены проектирования как со стороны ПЛИС, так и со стороны печатной платы.

В то время как воздействие одного решения скорее всего будет незначительным, несколько тысяч таких решений могут существенно повлиять на стоимость, производительность и надежность проекта.

Во всех областях проектирования есть как функциональные, так и физические аспекты интерфейса FPGA-PCB, доступные для изменений. Если ограничить анализ физическими правками интерфейса печатной платы, мы упростим анализ, при этом не потеряем акцент на прибыльности продукта.

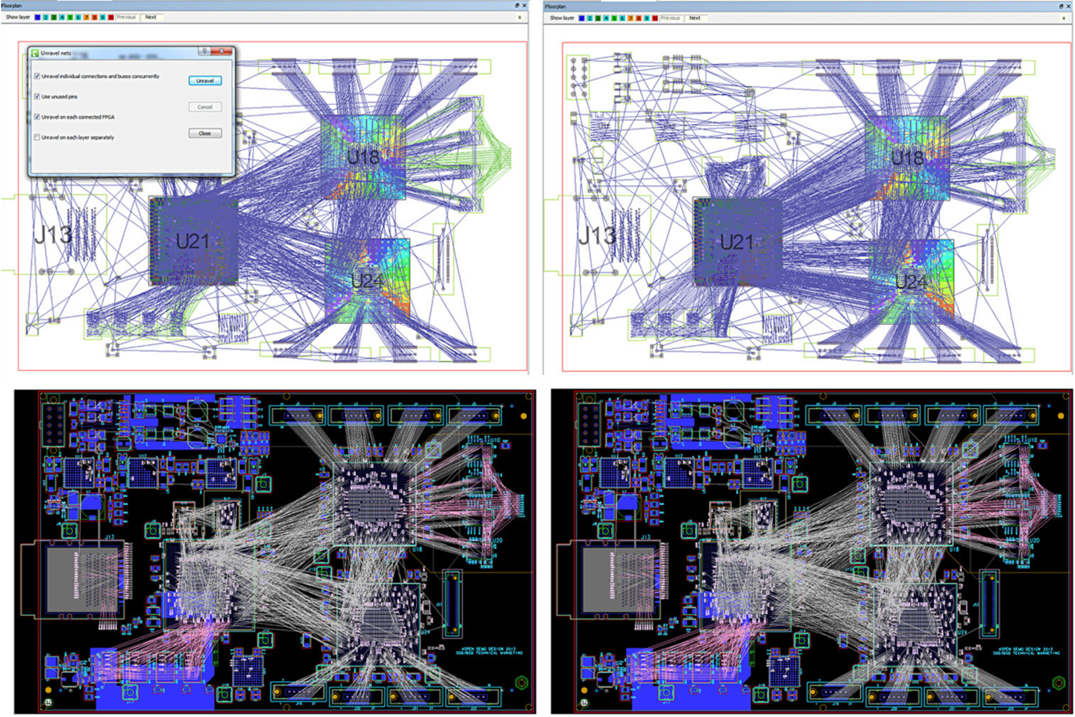

Каждый раз, когда сигнал печатной платы переназначается с одного контакта ПЛИС на другой, изменяется длина трассы, количество переходных отверстий, а также плотность трассировки. Это влияние заметно невооруженным глазом в случае длины трассы и плотности трассировки. На рис. 2 представлены два варианта назначения сигналов на выводы ПЛИС, из которых наглядно видно, как расположение сигналов на контактах ПЛИС влияет на длину трасс.

В этом примере длина проводников была уменьшена на 50%, в то же время снижены плотность трассировки и количество переходных отверстий.

Длина трассы влияет на задержку распространения сигнала в проводнике. За счет уменьшения длины трассы на 50%, задержка распространения сигнала была также уменьшена на 50%, что привело к увеличению на 100% максимальной рабочей частоты сигнала.

Переходные отверстия подвержены вибрации и, следовательно, могут стать механическими и электрическими местами возникновения дефектов. Минимизация пересечений проводников за счет гибкости распределения сигналов по контактам ПЛИС повысила надежность печатной платы.

В то время как влияние на плотность трассировки можно наглядно увидеть, сопоставление статистических характеристик с плотностью трассировки требует тщательного измерения площади поверхности, потребляемой обоими вариантами назначения сигналов. В нашем простом примере плотность трассировки была снижена примерно на 20%.

Очевидно, что назначение сигналов на выводы ПЛИС влияет на:

длину проводников;

задержку распространения сигналов;

надёжность печатной платы;

плотность трассировки.

Процессы, ускоряющие настройку проектных ограничений

Сколько времени в процессе проектирования уходит на выравнивание проводников в соответствии с временными ограничениями и требованиями к целостности сигналов? Если кратчайшее расстояние между двумя точками – прямая линия, то верно и то, что наименьшее расстояние достигается, когда две точки перемещаются как можно ближе друг к другу. Особенностью использования ПЛИС при проектировании печатных плат является то, что одна из двух точек электрического соединения – подвижна.

Можно тратить огромное количество времени на доработку и настройку (в соответствии с ограничениями) проекта печатной платы: изменять размещение компонентов, вращать их, формировать стек и пары сигнальных слоев, трассировать, подбирать материалы. Но более прагматичный подход – использовать гибкость ПЛИС. Сокращая до минимума соединения между ПЛИС и другими компонентами на плате, вы уменьшаете время, затрачиваемое на оптимизацию и выравнивание, на 20-50%.

Ускорение процесса проектирования и минимизация производственных затрат

Две ключевых характеристики ПЛИС позволяют ускорить процесс проектирования:

продуманный интерфейс FPGA-PCB (между ПЛИС и платой), который сокращает время трассировки на 25-50%;

гибкость назначения сигналов, которая уменьшает плотность трассировки и обеспечивает дополнительную площадь

Применение таких ПЛИС сокращает количество сигнальных слоев, необходимых для реализации того или иного интерфейса.

Зачастую оценить, обеспечивает ли текущая конфигурация слоев печатной платы необходимой площадью для трассировки, получается только в тот момент, когда становится ясно, что стек сконфигурирован неправильно. Используя гибкую функциональность ПЛИС для снижения плотности трассировки, можно оптимизировать стек печатной платы и избежать дополнительных затрат при производстве.

Прибыль от продукта – это последнее звено в цепочке принятия решений о возможных последствиях

Следствия решений, принимаемых на этапах от разработки интерфейса ПЛИС до получения прибыли, выстраиваются в подобие каскада домино. Инженеры не всегда осознают, что причина разрушения этого каскада может быть связана в том числе с влиянием, которое оказали их решения. Такая проблематика выходит за границы их зоны ответственности, а также приводит к противоречиям с устоявшимися процессами проектирования.

Понимание факторов, препятствующих оптимизации

Если гибкость ПЛИС может быть использована для оптимизации печатных плат, то почему разработчики так редко берут ее на вооружение?

Основные причины:

сложность проекта;

анализ рисков;

организация команды разработчиков;

традиционные процессы проектирования;

инфраструктура для поддержки процесса проектирования;

время выхода на рынок

доступность инструментов разработки.

Сложность проекта

Создание качественного интерфейса «ПЛИС-плата» – нетривиальная задача. Давайте рассмотрим возможные комбинации назначения сигналов на выводы ПЛИС:

2 вывода ПЛИС имеют 2 возможных варианта назначения;

3 вывода ПЛИС имеют 6 возможных комбинаций;

4 вывода ПЛИС имеют 24 возможные комбинации;

5 выводов ПЛИС имеют 120 возможных комбинаций;

небольшая ПЛИС на 100 контактов имеет 9х10157 комбинаций;

ПЛИС с 1000 сигнальными контактами имеет такое количество возможных комбинаций, что Microsoft Excel не в состоянии вычислить это значение.

Множество всех возможных конфигураций назначения сигналов на выводы ПЛИС содержит как разрешенные, так и запрещенные назначения.

Различие между разрешенным и запрещенным назначением определяется правилами производителя ПЛИС для каждого конкретного устройства.

Количество возможных конфигураций сигналов – это только одна из составляющих. Каждый вывод ПЛИС может быть определен как один из N возможных стандартов ввода/вывода, где N может достигать 78, как показано на рис. 3. Правила назначения являются динамическими и учитывают тип вывода, его логику и распределение по банкам как первичные переменные.

Простой пример: стандарт ввода-вывода 3,3 В не может сосуществовать со стандартом 1,8 В в пределах одного и того же банка контактов (область питания). Правила свопирования выводов будут определены только после того, как сигналы печатной платы будут назначены выводам ПЛИС и выводы ПЛИС будут электрически сконфигурированы в соответствии с этим сигналом.

Этот пример иллюстрирует основное различие между ПЛИС и стандартными компонентами с точки зрения их интерфейсов, но в то же время осложняет понимание реальных проблем при проектировании с использованием ПЛИС.

В каждом устройстве есть свои собственные комплексные и разнообразные правила и ограничения. ПЛИС имеют большое количество универсальных выводов:

тактовые пины, которые можно использовать в качестве сигнальных пинов ввода-вывода;

сигнальные пины ввода-вывода, которые могут быть использованы в качестве локальных тактовых пинов;

пины конфигурации ПЛИС (boot), которые могут использоваться в качестве сигнальных пинов ввода-вывода;

пины JTAG, которые можно использовать в качестве сигнальных пинов ввода-вывода;

пины ввода-вывода с регулируемыми настройками напряжения питания;

пины ввода-вывода с регулируемыми настройками скорости нарастания;

пины ввода-вывода с регулируемыми настройками терминирования;

пины ввода-вывода, которые могут быть сигнальным контактом дифференциальной пары положительной полярности;

пины ввода-вывода, которые могут быть сигнальным контактом дифференциальной пары отрицательной полярности;

Vref-пины, которые могут быть использованы в качестве пинов ввода/вывода при условии, что ни один из них в пределах одного и того же банка не требует опорного напряжения.

И это сокращенный список. Как правило, инженеру требуется несколько месяцев, для того чтобы получить опыт работы с устройствами ПЛИС, необходимый для эффективного создания проекта. К тому же этот опыт работы не распространяется на всю команду разработчиков, что приводит к появлению узких мест в процессе проектирования.

Анализ рисков

Расходы, связанные с ошибками, значительно превышают затраты на изготовление прототипа печатной платы. Цикл проектирования увеличивается, и реальная стоимость в итоге включает расходы, вызванные временными затратами на сравнение символов и изучение документации производителя ПЛИС для обнаружения ошибки (ошибок).

Наиболее распространенная реакция команды разработчиков на высокую сложность проектирования, связанную с интерфейсами FPGA-PCB, а также на необходимость поддерживать абсолютную синхронизацию данных между различными областями проектирования, заключается в фиксации проекта FPGA-PCB на ранних этапах процесса проектирования.

Если бы мы обсуждали ситуацию, когда у нас несколько десятков контактов, которые составляют интерфейс FPGA-PCB, то риск ошибки назначения сигналов и их сложность не стали бы решающими факторами в принятии решений разработчиками. Однако мы говорим об устройствах, в которых от нескольких сотен до нескольких тысяч сигнальных контактов. Когда комплексность выводов умножается на их количество, когда учитываются правила назначения выводов ПЛИС и далее анализируются для определения размера цепочки влияния на принятие решений, тогда необходимо учитывать миллиарды возможных факторов, влияющих на маржинальность прибыли продукта.

Организация команды разработчиков

Для того чтобы добиться эффективности в проектировании печатных плат, команда разработчиков ПЛИС, команда схемотехников и топологов должны работать в тесном сотрудничестве друг с другом. В то же время, благодаря аутсорсингу, возникла пропасть между функциональным и физическим проектированием. В процессе проектирования устройства проект передается от одной команды к другой, появляются организационные проблемы. Обмен проектными данными между подразделениями с целью оптимизации процесса разработки требует от руководства усилий, направленных на обеспечение эффективной коммуникации и минимизации риска возникновения ошибок.

Традиционные процессы проектирования

Важнейшим этапом в проектировании печатных плат остается разработка схемотехники. Историческим преимуществом процесса схематического проектирования является точная передача конструкторского замысла через символьное представление. Методы схематического проектирования имеют свои недостатки и риски:

необходимо создать и проверить УГО для всех компонентов, используемых в проекте;

ошибки в УГО приводят к неработоспособности печатных плат;

разработка схемы и подключение компонентов является трудоемким и длительным процессом;

ошибки в схеме приводят к неработоспособности печатных плат.

Создание одного символа для 500+ выводного ПЛИС – трудоемкий, длительный процесс с высоким риском появления ошибок, который может привести к тому, что символ физически не поместится на листе схемы. Чтобы вписать символ в размер листа, инженеры обычно разбивают УГО на составные части, что увеличивает трудоемкость и время на создание и верификацию. Чтобы обеспечить возможность повторного использования УГО, создаются общие символы с разбиением на основе банков.

Ограничение для таких общих символов ПЛИС заключается в том, что технически невозможно включить в них данные о свопировании, поскольку взаимная замена пинов является специфичной для конкретного проекта. Кроме того, понижается наглядность и читаемость схемы при одновременном увеличении затрат на процесс проектирования.

И поэтому проектировщики неохотно используют возможности ПЛИС для оптимизации печатной платы: затраты и риски, связанные с созданием, поддержкой и валидацией символов и схем, снижают для них ценность выгоды от гибкости ПЛИС.

Инфраструктура для поддержки процессов проектирования

Большинство компаний, занимающихся проектированием электронных устройств, используют корпоративные библиотеки и рабочие процессы для минимизации риска, связанного с ошибками при использовании COTS-компонентов (Commercial Off-The-Shelf — «готовые к использованию»). Исторически такие компоненты имеют общую особенность: их конфигурация практически не меняется. И поэтому целесообразно один раз потратить ресурсы для создания и проверки компонента, а затем использовать его во всех проектах, где это необходимо.

Та же логика была ошибочно применена к устройствам ПЛИС в попытке минимизировать риск, связанный с их использованием в сложных проектах. При этом не принимается во внимание простая истина: конфигурация ПЛИС индивидуальна для каждого проекта. В связи с тем, что для компонентов ПЛИС применяется историческая практика сокращения риска, в результате возникает ситуация, когда замена выводов (свопинг) в процессе проектирования не допускается. Существует мнение, что тополог не обладает специальными знаниями и опытом проектирования ПЛИС, как правило для того, чтобы обеспечить правильное свопирование выводов, в результате чего существенно теряется гибкость проектирования, которую можно было бы использовать для оптимизации печатной платы.

Время выхода на рынок

Время, затрачиваемое на вывод продукта на рынок, часто является основным фактором при принятии решения о применении ПЛИС. В условиях сжатых сроков реализации проекта одним из ключевых аспектов сокращения времени, необходимого для удовлетворения потребностей рынка, является снижение рисков, связанных с проектированием.

Использование гибкости ПЛИС для оптимизации печатных плат позволяет уменьшить риски при планировании проектирования.

Действительно, использование гибкости ПЛИС неоднократно доказывало, что существенно влияет на сокращение времени вывода продукта на рынок. Однако, это утверждение верно только тогда, когда для решения каждой проблемы оптимизации печатных плат используются современные технологии проектирования.

Доступность инструментов разработки

Каждый производитель ПЛИС предоставляет инструменты, которые позволяют автоматически формировать сигналы для назначения на выводы в конкретном устройстве. Эти решения учитывают только саму ПЛИС при формировании интерфейсов и никогда не учитывают физические соединения на печатной плате. Справедливости ради, следует отметить, что в случае, если поставщики ПЛИС будут поставлять инструменты, учитывающие компоновку печатной платы, это будет выглядеть, как неправильное вложение ресурсов или недостаток экспертизы с их стороны.

Давайте рассмотрим возможность использования на одной печатной плате нескольких FPGA, каждая из которых имеет 1500 контактов. Возможность вручную оценить все возможные варианты оптимизации такой конфигурации представляется абсолютно нереалистичной. Очевидно, что это область, где компьютерная оптимизация является единственной практической альтернативой.

Краткое резюме

Сочетание анализа рисков, исторических и культурных аспектов проектирования, соответствующей экспертизы, а также сложность каждого интерфейса (количество возможных вариантов исполнения) – все это создает прецедент для использования общих символов ПЛИС. Такой подход сводит к минимуму возможности оптимизации печатных плат и выводит рост прибыли вашего продукта за рамки обычного процесса проектирования.

Потенциал

Использование преимуществ применения ПЛИС позволило разработчикам добиться фантастических результатов в оптимизации печатных плат:

сократить трудоемкость как минимум на одну человеко-неделю на каждую ПЛИС с не менее 500 контактов;

сократить длины проводников на 25-50% и одновременно повысить производительность;

уменьшить количество переходных отверстий в среднем на 150 шт. на каждую 500-выводную ПЛИС;

сократить время проектирования интерфейсов на 60%;

превратить нетрассируемую плату в трассируемую с использованием одного и того же стека слоев;

сократить общий цикл проектирования на 50%.

Энергия цунами

Очевидно, что использование гибкости FPGA-устройств для оптимизации проектирования печатных плат с целью получения прибыли является важной составляющей эволюции процессов проектирования. На самом деле, этот этап оптимизации представляет собой первый шаг на пути к оптимизации печатных плат.

А как насчет систем на печатных платах, использующих более одной ПЛИС? Как быть, если сложность проекта предполагает использование 3, 4, 10, 20 ПЛИС-устройств? Без предварительной оптимизации такие проекты неизбежно столкнутся с проблемами при трассировке. Как показывает опыт, если для реализации проекта необходимо одно или два FPGA-устройства высокой плотности, то ваша команда разработчиков должна обладать достаточным опытом, знаниями, высокой самоотдачей и трудолюбием, чтобы выполнить поставленную задачу. Скорее всего, у них никогда не возникало необходимости рассматривать вопрос оптимизации прибыли, зато они следовали графику, и продукт работал. Как только на печатной плате окажется более 4 таких ПЛИС, самоотверженность вашей команды пошатнется, количество сигнальных слоев будет расти, как, впрочем, и расходы на производство печатных плат.

Клиенты, привязанные к своей корпоративной инфраструктуре, процессам и политикам, часто сталкиваются с оптимизацией печатных плат впервые, когда они пробуют более сложные проекты печатных плат, содержащих несколько FPGA-устройств. Распространенной практикой является попытка либо уменьшить количество ПЛИС путем поиска более мощных устройств, либо упростить проект. Главное – не сталкиваться с трудностями и ограничениями, связанными с оптимизацией печатной платы.

Применение технологий оптимизации печатных плат в проектах с несколькими ПЛИС представляет собой следующее звено в процессе оптимизации. Ключевым требованием при оптимизации является возможность одновременной оптимизации нескольких ПЛИС от разных производителей.

Знаете ли вы, что возможность гибкого назначения сигналов на выводы ПЛИС может быть использована для уменьшения количества компонентов на вашей печатной плате? За счет изменения электрических характеристик пинов дискретные компоненты могут быть исключены из конструкции печатной платы. Большинство команд проектировщиков работают в условиях дефицита времени и никогда не имели возможности исследовать этот уровень оптимизации печатной платы, не говоря уже о развитии необходимых технических навыков для использования этой продвинутой мощности и гибкости ПЛИС.

Не следует недооценивать опыт, необходимый для того, чтобы добиться уменьшения количества дискретных компонентов путем изменения электрических характеристик выводов ПЛИС:

изменения электрических характеристик выводов имеют зеркальное влияние как внутри корпуса FPGA, так и на самой печатной плате;

инструменты анализа целостности и времени сигналов, а также опыт их использования должны применяться для оценки каждого предполагаемого изменения электрических характеристик.

Как только использование внутри кристального терминирования считается целесообразным, необходимо выработать стратегию, учитывающую шум от одновременного переключения выходных буферов (SSN – Simultaneous Switching Output Noise).

При этом недооценка конкурентных преимуществ, получаемых за счет минимизации затрат на комплектующие для печатных плат и соответствующего положительного влияния на прибыль продукта, откроет дополнительные возможности для ваших конкурентов. В сочетании с современными процессами производства печатных плат (High Density Interconnect (HDI)) возможна существенная экономия затрат на производство, что является достаточным основанием для того, чтобы некоторые команды разработчиков печатных плат инвестировали значительные средства и вышли на следующую ступень оптимизации производства печатных плат.

Дверь для оптимизации печатных плат была открыта, но конечный пункт назначения не имеет координат. Мощность и гибкость FPGA-устройств продолжает развиваться так же, как и опыт, и знания, связанные с использованием этой гибкости и мощности.

Вам только осталось задать себе вопрос: хотите ли вы идти по пути оптимизации печатных плат?

Существующие на сегодняшний день инструменты

С момента, когда Siemens EDA (formely Mentor Graphics) открыл для себя возможности оптимизации устройств FPGA – а это более чем 10 лет назад – они непрерывно инвестируют в эту технологию. Siemens EDA (formely Mentor Graphics) разработали FPGA I/O Optimizer, который обеспечивает удобную оптимизацию печатных плат и одновременно устраняет риск возникновения ошибок, позволяет масштабироваться для обеспечения одновременной оптимизации нескольких ПЛИС, как показано на рис. 4. Технологическое лидерство и крупные партнеры-клиенты – эти два фактора способствовали развитию и валидации процесса оптимизации печатных плат как ключевого конкурентного преимущества для команд разработчиков РЭА.

С демонстрацией работы FPGA I/O Optimizer, а также с кратким описанием его функционала можно ознакомиться посмотрев вебинар:

Тестовые 30-дневные лицензии можно запросить ЗДЕСЬ

Присоединяйтесь к нам в соц. сетях:

Филипов Богдан

Field Application Engineer, Nanosoft