Перед нами девушка Лиля, с FPGA платой и учебником Харрис & Харрис в руках, на фоне самого высокого на Земле дерева Sequoia sempervirens, недалеко от Стенфорда в Silicon Valley.

Представьте, что вы приехали сюда в командировку в типичную электронную компанию. Усаживаетесь в офисе, входите со своего ноубука (в Америке их чаще называют лаптопами) в корпоративную сеть и пытаетесь что-то напечатать. А принтер не подсоединяется. Вы обращаетесь к ко-воркеру "Что делать?", а он вам говорит: "Обратитесь в IT". Вы в замешательстве "В Ай-Ти? А я что - не айтишник?"

Спокойствие. Если вы программист, вы не IT, вы software engineer и работаете в отделе Software Engineering Department. Если вы электронщик, вы тоже не IT, вы работаете в Hardware Engineering Department. IT Department - это другое, это отдельный от разработки отдел, это группа сисадминов, которые поддерживает внутри-корпоративную сетку и ведут учет выданых сотрудникам лаптопов.

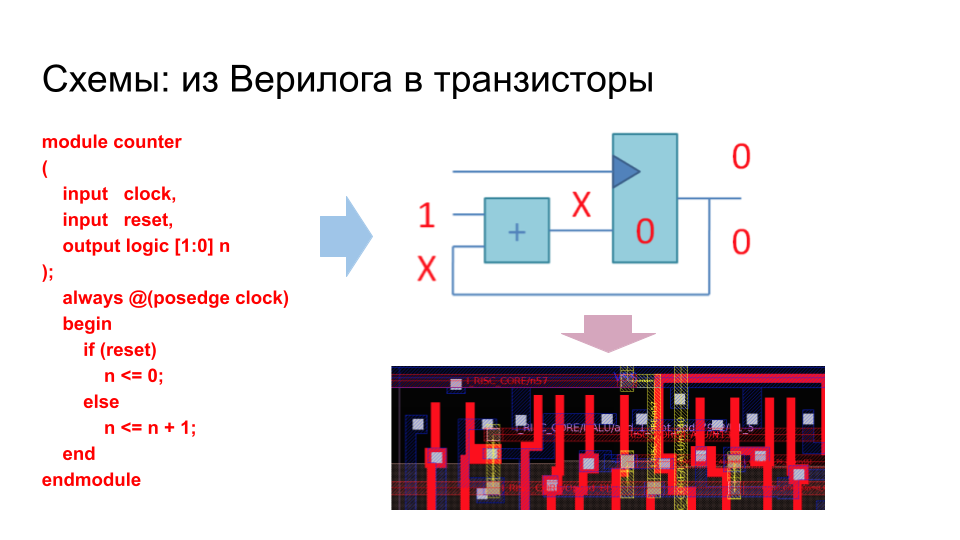

Но это слишком тривиально, обсудим более интересный вопрос: вот все эти люди, которые пишут код на языке описания аппаратуры Verilog, который потом превращается в дорожки и транзисторы из silicon на фабрике - они программисты? Аппарентли, нет.

Код на Verilog выглядит как программа? Но код на HTML тоже незнакомому с ним человеку может показаться похожим на программу.

В язык Верилог входят все черты языков программирования, в SystemVerilog есть даже классы и ООП, но это связано с тем, что верилог используется не только для написания кода, который превращается ("синтезируется") в железо, но и для написания моделей, тестового окружения и тестов.

Код на синтезируемом подмножество верилога использует уровень абстракции, который называется "уровень регистровых передач" - Register Transfer Level, RTL (не путать с другими расшифровками аббревиатуры, например Run Time Library или Resistor–Transistor Logic).

Тут человек, который не знаком с верилогом, но программировал на ассемблере, услышав слово "регистровая передача" может кивнуть "а понятно, это как в MOV R5, R0". Нет, непонятно. Проблема в том, что слово "регистр" в данном случае является омонимом. У слова "регистр" если два (точнее три, но сконцентрируемся на двух) разных значения:

1. Регистр в контексте программирования на ассемблере. Электронщики называют такие регистры software-visible registers, "регистры, видимые софтверу" или architecture registers, "архитектурные регистры", чтобы не путать с микроархитектурой (архитектура и микроархитектура - это столь же разные вещи как культура и физкультура).

2. Регистр как набор из D-триггеров в электронной схеме. Те регистры, которые видит программа и которые доступны инструкциям (см. пункт первый) - тоже на электронном уровне строятся из D-триггеров, но кроме них в процессоре есть на порядок или два порядка больше других регистров. Регистры используются для хранения данных между стадиями конвейера, для буферов при сбрасывании в кэш данных, как состояние в конечных автоматах итд.

[3. Есть еще memory-mapped registers, хорошо знакомые например программистам микроконтроллеров, но опустим их из этого поста для сохранения фокуса]

Так вот.

Когда вы пишете на верилоге:

always @ (posedge clock)

r <= функция_нового_состояния_от (r, вводы, другие_регистры);

- вы создаете схему, на уровне регистровых передач, которая реализуется комбинационным облаком из элементов и-или-не итд и стоит между вводами, регистрами (в значении 2, то есть D-триггерами) и регистром r (опять в значении 2, то есть группой D-триггеров).

Register transfer в контексте проектирования - это задание правила трансфера (функции) превращения состояния регистров из предыдущего такта, перед положительным фронтом тактового сигнала clock, в состояние регистров в новом такте.

А вот когда вы пишете:

MOV R5, R0

- вы создаете программу, последовательность из нуликов и единичек, которая хранится в памяти, откуда ее вытаскивает процессор (схема), декодирует и на ее основе меняет свое внутреннее состояние, которое включает PC - program counter, software visible регистры и другие регистры (в значении 2).

Схема которая строится с помощью так называемого маршрута RTL2GDSII из кода на верилоге, является не абстрактной диаграммой, а случае ASIC design совершенно конкретной электрической схемой, изготавливаемой на фабрике. C металлическими дорожками меди, которые соединяют блоки ASIC library, которые реализуют функции and2, and3, andor, mux, dff (d-flip-flop) итд.

"Ну а как с FPGA design? Ведь там мы не переделываем микросхему на фабрике, а меняем ее, загружая биты в память конфигурации. Разве bitstream - это не программа?"

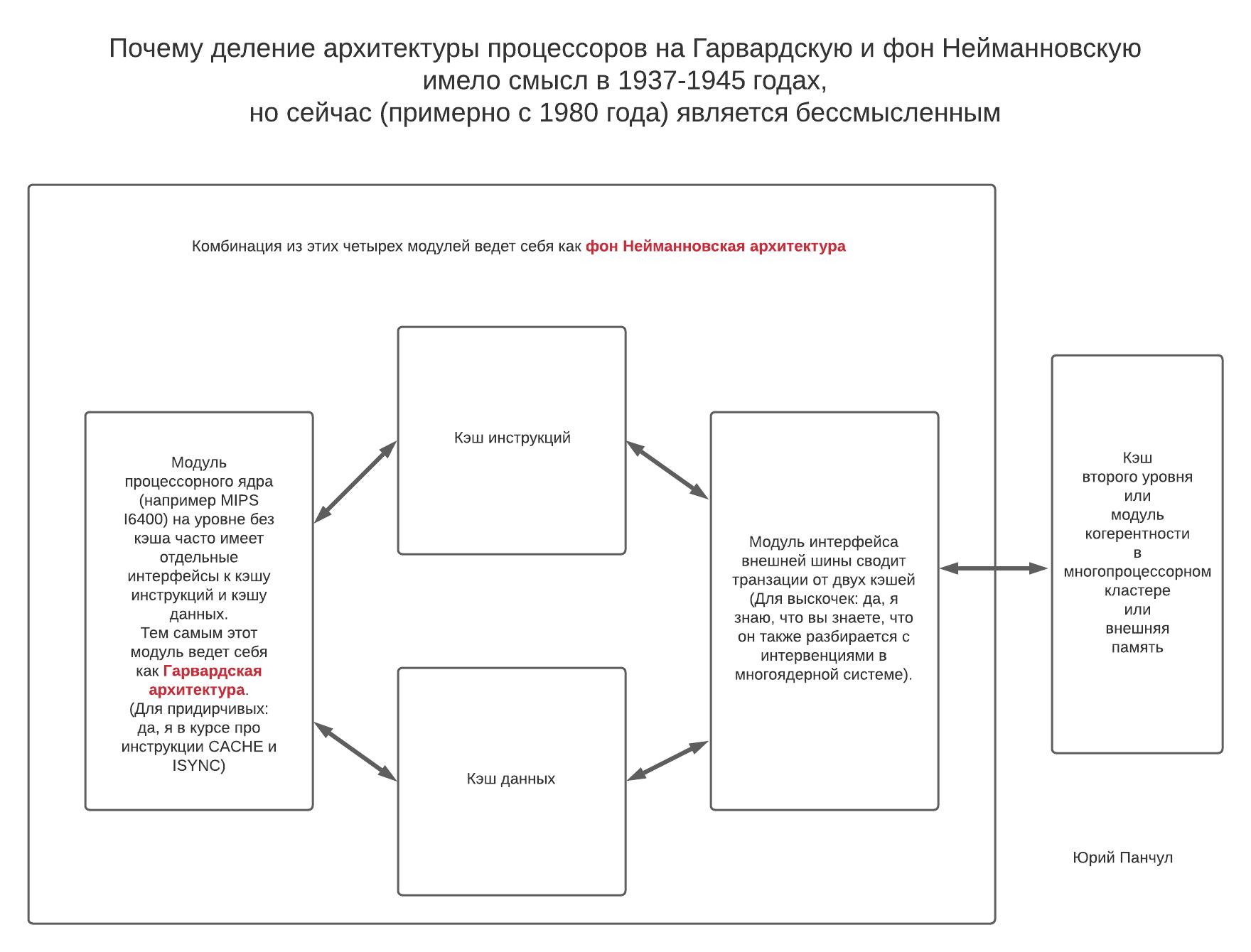

В случае FPGA design схема является более виртуальной - она задаётся набором битов подключенным к контрольным сигналам мультиплексоров, идущим к lut (lookup table) и другим элементам clb (ячеек) уже сделанной на фабрике микросхемы FPGA. Но эта схема все равно не является программой. Потому что словом "программа", по сложившейся с 1940-х годов традиции, называют цепочку инструкций фон-Нейманновской машины (сейчас кто-то решит показать эрудицию и заговорит о гарвардской архитектуре, но мы возразим эрудиту вот такой картинкой:

В американских, [западно]европейских и [южно и восточно]азиатских электронных компаниях никто синтезируемый код на верилоге программой не называет. Говорят просто "RTL': "напишите RTL", "готов RTL?" , а не "напишите программу?" , "готова ли программа?" итд.

Как же научиться RTL?

Группа энтузиастов по подьему образования в России и Украине на уровень 21 века провела в сентябре в Сколково Школу Синтеза Цифровых Схем с упражнениями на FPGA платах. Школа оказалась популярна (на 25 мест было 86 заявок) и мы решили ее расширить до полноценного семестрового курса по субботам, с объемом материала на уровне университетских лабораторных по FPGA (типа MIT 6.111), к которым добавили элементы компьютерной архитектуры, базовый туториал для ASIC и некоторые умения из промышленности.

Новый цикл занятий начнется с 30 октября 2021, закончится 12 февраля 2022, и будет проходить по субботам в Сколково в Москве, с трансляцией в казанский Иннополис и другие места. Регистрация уже открыта .

Среди преподавателей на школе - инженеры российской компании Syntacore / Ядро, SberDevices, IRQ, ИнСис и Inline Group (использование FPGA для высокоскоростного трейдинга на бирже), преподаватели МИЭТ, МИРЭА, МГУ, ВШЭ МИЭМ, Черниговского ЧНТУ, российского представительства Mentor Graphics / Siemens EDA. Школа поддержана компанией Cadence Design Systems.

Место еще не выбрано окончательно, но занятия будут проходить или в Технопарке Сколково, или вот в таком занятном здании, которое называется Гиперкуб и в котором можно поместить больше участников. Вы можете высказать в опросе, что лучше - технопарк или гиперкуб:

Школа предназначена для трех категорий слушателей:

Школьники-старшеклассники олимпиадного типа смогут понять, что представляют из себя работы в микроэлектронной промышленности: проектирование чипов для смартфонов, игровых приставок и самоуправляющихся автомобилей, или использование микросхем реконфигурируемой логики для управления космическим кораблем.

Студенты младших курсов смогут заложить твердую основу для дальнейшего изучения схемотехники и архитектуры компьютеров в их вузах.

Преподаватели вузов, физматшкол или кружков технологии смогут найти материал для постановки или улучшения своих курсов.

Школа может также понравиться кросс-дисциплинариям. Вот например участники школы на ChipEXPO распознают с помощью FPGA платы мелодии, которые играет для них преподавательница флейты Мария Беличенко:

План семинаров школы:

30 октября 2021: 1. Введение в маршрут проектирования и упражнения с комбинационной логикой.

13 ноября 2021: 2. Последовательностая логика и конечные автоматы.

20 ноября 2021: 3. Разбор учебного проекта: модульная графичеcкая игра со спрайтами.

27 ноября 2021: 4. Разбор учебного проекта: распознавание и генерация звуков и мелодий.

4 декабря 2021: 5. Конвейеры и систолические массивы, с приложением для искуственного интеллекта.

11 декабря 2021: 6. Архитектура: вид процессора с точки зрения программиста.

18 декабря 2021: 7. Микроархитектура: вид процессора с точки зрения схемотехника.

25 декабря 2021: 8. Пробуем маршрут RTL2GDSII: как разрабатываются массовые микросхемы.

15 января 2022: 9. Элементы микроархитектуры 1: очереди FIFO и кредитные счетчики.

22 января 2022: 10. Элементы микроархитектуры 2: арбитры, банки и разделение памяти.

29 января 2022: 11. Элементы микроархитектуры 3: строим процессорный кэш.

5 февраля 2022: 12. Имитация собеседования на позицию проектировщика цифровых микросхем.

12 февраля 2022: 13. Разбор имитации интервью с вручением поощрительных призов.

Популярная группа GSPD (что расшифровывается как "Государственная Служба Пропаганды Дискотек" - про это у них есть песня) сочинила также песню "У России три пути - Рейвы, Водка и Айти".

Но они неправы! У России несомненно есть и четвертый путь - проектирование сверхбольших интегральных микросхем с продвинутой микроархитектурой. Для гаджетов, сетевой инфраструктуры, ускорителей машинного обучения, космических аппаратов и самоуправляемых автомобилей. И для этого нам всем нужно подготовить будущих супердизайнеров проектирования на уровне регистровых передач. Из современных школьников и студентов.

Кое-что из этого будущего уже появляется - например российский процессор Скиф для планшетов, спроектированный в зеленоградском НПО Элвис. Но одного Элвиса не хватит, чтобы изделия на российских микросхемах значимо проникли например на Consumer Electronics Show в Лас-Вегасе - для этого нужна на порядок бОльшая инженерная экосистема.