В данной статье представлен перевод материала, взятого с сайта Xilinx. Уровень владения языка и осведомленность в данной теме оставляет желать лучшего, но, надеюсь, данный материал кому-то принесёт пользу.

Устройства Spartan-7, новейшее поколение, предлагают лучшую в своем классе производительность/ватт, а также упаковку малого форм-фактора, отвечающую самым строгим требованиям. Эти устройства оснащены программным процессором MicroBlaze, работающим более 200 DMIP, с поддержкой DDR3 800 Мбит/с, построенными по технологии 28 нм. Кроме того, устройства Spartan-7 предлагают интегрированный АЦП, специальные функции безопасности и Q-класс (от -40 до + 125 ° C) на всех коммерческих устройствах. Эти устройства идеально подходят для промышленных, бытовых и автомобильных приложений, включая возможность соединения «любой-к-любому», объединение датчиков и встроенное зрение.

Автомобильная модель Spartan-7. Преимущества продукта

Устройства Zynq UltraScale + MPSoC объединяют в одном устройстве многофункциональную 64-разрядную четырехъядерную систему обработки ARM Cortex -A53 и двухъядерный процессор ARM Cortex-R5 (PS) и программируемую логику Xilinx (PL) UltraScale. Это масштабируемое решение для устройств идеально подходит для различных автомобильных платформ для помощи водителям и автоматизированным системам вождения, предоставляя непревзойденное сочетание производительности, энергоэффективности, функциональной безопасности и функций безопасности.

Семейство Xilinx Spartan-7 предлагает ряд недорогих и высокоэффективных ПЛИС. Эти устройства были специально разработаны для удовлетворения особых потребностей чувствительного рынка.

ПЛИС Spartan-7 объединяет в себе высокопроизводительную программируемую архитектуру 28 нм с низкой стоимостью, компактным размером корпуса, обеспечивающий высокую производительность при небольшой занимаемой площади на печатной плате. Ключевые преимущества семейства Spartan-7 включают в себя:

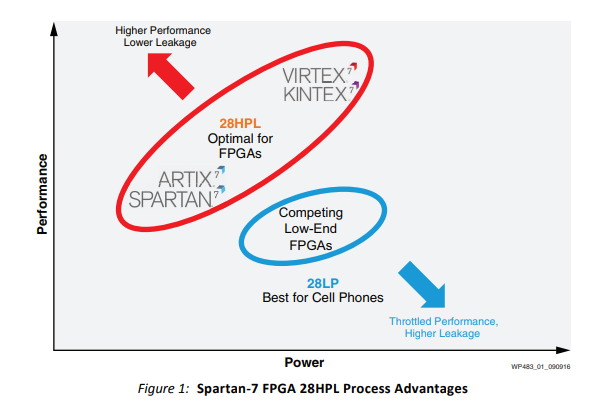

- Процесс 28HPL с максимальной производительностью на ватт

- Масштабируемость архитектуры 28 нм для повторного использования дизайна

- Vivado Design Suite для простого и недорогого ввода дизайна и проверки

Это обеспечивает проектировщика необходимыми ресурсами при низком энергопотреблении и низкой общей стоимости для удовлетворения потребностей чувствительных к стоимости приложений.

Семейство Xilinx Spartan FPGA заслужило свое наследство как ведущий класс ПЛИС с оптимальной стоимостью с момента его создания в 1998 году. Оно включает в себя множество поколений недорогих устройств малого форм-фактора, предназначенных для соединения, коммутации, управления, обработки, сопряжений и других функций. Но для соответствия производительности и возможности, необходимым для современных приложений, например, для «Промышленного интернета вещей» (I-IoT), усовершенствованных систем помощи водителю (ADAS) / систем осведомленности водителя и медицинских систем следующего поколения, требуется гораздо больше, чем одна логика. Ввиду этого растущего спроса на функциональные возможности небольшого размера семейство Spartan-7 и программный процессор MicroBlaze созданы для удовлетворения потребностей в высокопроизводительной, оптимизированной по стоимости, программируемой логике и встроенной обработке, доступной в компактном виде. Выбирая идеальный процесс Xilinx разработал 28-нм технику HPL совместно с TSMC при создании устройств серии 7 (Artix-7, Kintex-7 и Virtex-7).

Процесс производства металлических затворов с высоким значением диэлектрической константы (HKMG) обеспечивает наилучшее сочетание высокой производительности и низкого энергопотребления, позволяя создавать разные семейства для обслуживания различных потребностей рынка. FPGA Spartan-7 используют тот же процесс 28HPL, что и установленные семейства 7-й серии, и получают выгоду от множества базовых элементов архитектуры. В результате появилось семейство компактных, оптимизированных по стоимости ПЛИС, которые обеспечивают высокую логику и производительность ввода-вывода при строго контролируемом энергопотреблении и способны вписаться в агрессивно малый корпус форм-фактора — и все это при низких затратах. Гибкость процесса также позволяет устройствам работать при двух разных напряжениях ядра, что позволяет пользователю выбирать компромисс между максимальной производительностью и минимальным энергопотреблением. В отличие от процесса 28LP, используемого конкурирующими ПЛИС, процесс 28HPL имеет достаточно широкое операционное окно, позволяющее устройствам достигать лучшей метрики производительности/мощности, то есть более высокой производительности при более низком энергопотреблении.

Архитектура успеха. Логическая структура является основой для всех архитектур ПЛИС. Логические ячейки являются единой мерой емкости и возможностей устройства, но для того, чтобы разработчик понимал, что можно сделать с устройством, иногда необходимо более глубоко изучить составляющие блоки. ПЛИС Spartan-7 использует настраиваемый логический блок (CLB), который содержит срезы, которые состоят из справочных таблиц (LUT), цепочек переноса и регистров. Эти срезы могут быть сконфигурированы для выполнения логических функций, арифметических функций, функций памяти и функций сдвига регистров. Благодаря поколениям ПЛИС Spartan-7 количество ресурсов в CLB эволюционировало, чтобы постоянно обеспечивать оптимальные возможности по разумной цене. Например, CLB в Spartan первого поколения (конец 1990-х годов) содержал одну LUT с 3 входами, две LUT с 4 входами и два регистра. Сравнивая это с восемью 6-входными LUT и шестнадцатью регистрами в CLB в ПЛИС Spartan-7, легко увидеть прогресс в работе устройства.

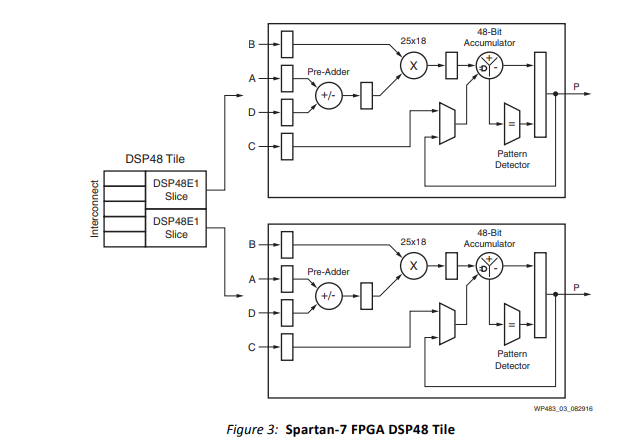

LUT в Spartan-7 могут быть сконфигурированы как одна 6-входная LUT с одним выходом или как две 5-входные LUT с отдельными выходами. Каждый LUT может быть дополнительно зарегистрирован в триггере. Четыре LUT и восемь триггеров образуют срез, а два среза образуют CLB. Некоторые из секций могут также использовать свои LUT в качестве распределенной 64-битной оперативной памяти или в качестве 32-битных сдвиговых регистров (SRL32). Эти мощные и гибкие функции могут быть реализованы непосредственно на этапе синтеза Vivado Design Suite, что позволяет пользователям использовать расширенные возможности, не тратя время на изучение всех отдельных портов и имен сигналов различных блоков. Однако эффективность проектирования, предлагаемая ПЛИС Spartan-7, не ограничивается LUT и регистрами; блоки, предназначенные для обработки и хранения цифровых сигналов, также доступны для разработчика. DSP Аудио и видео контент все чаще встречается в современных системах. Высокоскоростные математические характеристики необходимы для обеспечения возможности манипулирования цифровыми аудио- и видеоданными. Для облегчения проектирования в такой среде все FPGA Spartan-7 включают в себя несколько фрагментов DSP, каждый из которых содержит два фрагмента DSP. Каждый срез содержит множитель 25x18 и 48-разрядный аккумулятор, способный работать на частотах 550 МГц или выше.

25-битный предварительный сумматор позволяет экономически эффективно создавать симметричные фильтры, такие как FIR-фильтры. Если посмотреть на устройство средней комплектации Spartan-7, такое как XC7S50, то есть 120 DSP-срезов, которые, если все они используются для реализации симметричных FIR-фильтров, обеспечивают проектировщику 132 GMAC/с вычислительной мощности. Конечно, при всех этих возможностях обработки проект также требует места для хранения данных до и после обработки.

32-разрядный программный процессор RISC MicroBlaze

Процессор MicroBlaze представляет собой 32-разрядный микропроцессор с высокой степенью конфигурации, оптимизированный для ПЛИС Xilinx. Чтобы ускорить развертывание приложения, были определены предустановленные конфигурации («предустановки»), которые аналогичны другим известным классам процессоров:

- Микроконтроллер: для запуска чистого кода.

- Процессор реального времени: для детерминированных возможностей обработки в реальном времени с ОСРВ.

- Процессор приложений: для полной мощности Linux во встроенной системе.

Начиная с этих предустановок, можно добавлять или удалять различные конкретные параметры для дальнейшей настройки процессора в соответствии с конкретными потребностями приложения. Процессор MicroBlaze отвечает требованиям для множества различных приложений на рынках I-IoT, медицины, автомобилестроения, бытовой техники и связи, в частности. Процессор MicroBlaze может использоваться во всех семействах Xilinx FPGA и All Programmable (AP) SoC. Он бесплатно входит в комплект инструментов Vivado HL WebPACK Edition. Используя IP-интегратор инструментов Vivado, процессор MicroBlaze можно расширить с помощью IP-адреса из каталога периферийных устройств с поддержкой драйверов, таких как ШИМ, UART, последовательные интерфейсы и т. Д. Дизайнеры могут использовать бесплатный комплект разработки программного обеспечения Xilinx на основе Eclipse.

Память

В дополнение к распределенной оперативной памяти, упомянутой ранее, все ПЛИС Spartan-7 содержат настраиваемые блоки памяти объемом 36 КБ, называемые блочной оперативной памятью. Каждый блок ОЗУ может поддерживать различные режимы работы, включая однопортовый, простой двухпортовый, истинный двухпортовый и FIFO. ОЗУ блока можно использовать как отдельные блоки по 36 КБ, разделить на два независимых блока по 18 КБ или соединить вместе, чтобы получить ОЗУ объемом 64 КБ или более. Для обеспечения правильного содержимого памяти каждый блок RAM имеет дополнительную схему проверки и исправления ошибок (ECC), способную исправлять однобитовые ошибки и обнаруживать двухбитные ошибки. FPGA Spartan-7 содержат до 120 блоков оперативной памяти, что эквивалентно 4,2 МБ встроенной памяти. Добавьте к этому распределенную оперативную память, и доступное хранилище увеличится до 5,3 МБ. Интерфейс ввода-вывода и памяти FPGA Spartan-7 обмениваются данными через печатную плату через свои высокочастотные (HR) входы/выходы, способные взаимодействовать по многим стандартам, включая HSTL, SSTL, LVDS, LVCMOS и RSDS, работающие от 1,2 В до 3,3 В. Программируемая мощность привода позволяет вводу-выводу HR может обеспечивать любое соединение с любым до 1250 Мбит/с, потребляя при этом как можно меньше энергии. Для дальнейшего снижения энергопотребления в блоке ввода/вывода отдельные компоненты могут быть отключены, если они не используются. Например, буфер вывода отключен во время транзакции чтения, а буфер ввода отключен во время операции записи.

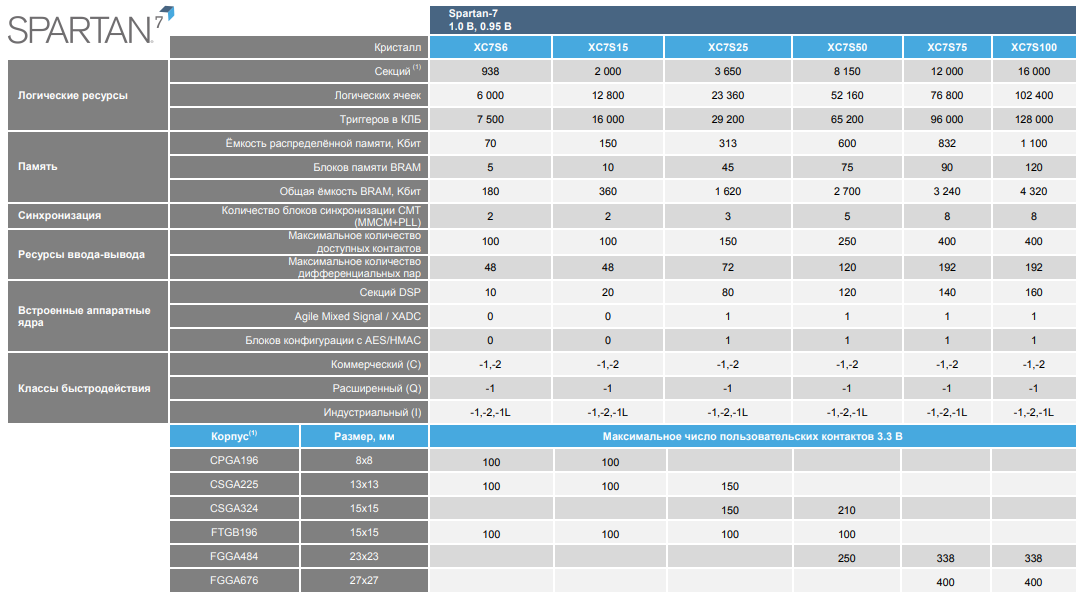

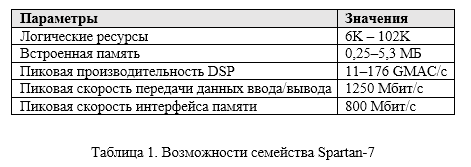

Подобно тому, как включены другие функции Spartan-7, Vivado Design Suite избавляет дизайнера от сложности решения, когда отключать буферы ввода-вывода. HR-входы в Spartan-7 расположены в блоках по 50 выводов ввода-вывода. Благодаря реализации встроенной памяти PHY, каждый полностью связанный банк способен реализовать интерфейс памяти. Инструмент генератора интерфейсов памяти (MIG), доступный в Vivado Design Suite, упрощает создание контроллеров программной памяти в соответствии с требованиями дизайнера. Он может быть настроен для поддержки до 800 Мбит/с недорогой основной DDR3 или может альтернативно поддерживать устаревшие стандарты, такие как DDR2 и LPDDR2. В таблице 1 показаны возможности Spartan-7 в табличном формате. На печатных платах такие приложения, как промышленные системы управления, часто имеют электронику, распределенную по большой площади, но с очень ограниченной областью, доступной в каждом месте. Как правило, сигналы от датчиков должны быть сопоставлены, обработаны и отправлены в центральный блок управления для объединения вместе. Физическая область, доступная для выполнения начальной сортировки и обработки, часто очень ограничена.

Небольшой форм-фактор, недорогие сборки. Чтобы втиснуть мощные программируемые возможности в ограниченном пространстве, семейство Spartan-7 использует ряд недорогих сборок размером от 8x8 мм с шагом 0,5 мм. Устройства, доступные в одной и той же сборке, всегда совместимы с занимаемой площадью, поэтому пользователь может мигрировать вверх в пределах одного пакета, если требуется расширенная функциональность.

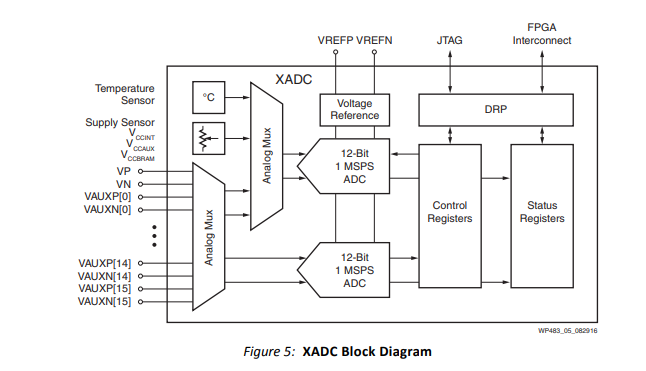

XADC. Большинство Spartan-7 содержат гибкий аналоговый интерфейс, называемый XADC. В сочетании с программируемой логикой XADC может выполнять широкий спектр функций сбора данных и мониторинга. Это позволяет разработчику отслеживать поведение системы даже в удаленных труднодоступных местах.

XADC содержит два 12-разрядных АЦП 1MSPS с отдельными усилителями отслеживания и удержания, встроенный мультиплексор до 17 внешних аналоговых входов и встроенные датчики температуры и питания для обеспечения общей надежности, доступности, безопасности и безопасности системы. соответствующие уровню безопасности FIPS 140-2 4. Большинство ПЛИС Spartan-7 обеспечивают безопасность проектирования и IP с помощью ряда различных мер. Программный файл или поток битов может быть зашифрован с использованием 256-битного шифрования AES, чтобы обеспечить конфиденциальность при выключении системы и во время настройки при включении. Ключ дешифрования может храниться либо в ОЗУ с резервным питанием от батареи, либо в eFuse, причем первый может очищать содержимое ключа при обнаружении подделки.

Предоставление инструментов для работы в среде Vivado IDE представлена простая методология разработки с кнопками со многими расширенными функциями, позволяющая дизайнерам быстро создавать проекты, ориентированные на FPGA и SoC. Многие функции повторного использования дизайна позволяют упаковывать разделы дизайна или IP, созданные для одного устройства или семейства, для последующего повторного использования в другом устройстве или семействе, использующем аналогичную архитектуру. Например, разработчик может создать IP-адрес, который используется в Spartan-7. По мере развития системных требований разработчик может повторно использовать тот же IP-адрес в ПЛИС Artix-7. Vivado Design Suite позволяет пользователю вводить RTL-проекты на выбранном ими языке с поддержкой VHDL 2008, Verilog и System Verilog. После того, как дизайн создан, появилось множество инструментов отладки и проверки для обеспечения правильной функциональности, в том числе бесплатный инструмент для моделирования на разных языках без ограничений строки кода. Все производственные устройства Spartan-7 поддерживаются бесплатными Vivado HL WebPACK Edition и Xilinx SDK, что обеспечивает самый быстрый и недорогой инструмент для этих устройств. ПЛИС Spartan-7 объединяют в себе высокопроизводительную программируемую архитектуру 28нм в недорогом, компактном корпусе, обеспечивающей высокую производительность при небольшой занимаемой площади печатной платы. Сочетание логики, памяти, DSP, ввода-вывода и схемы интерфейса памяти, программного процессора MicroBlaze и периферийного IP-адреса и 28-нм высокопроизводительного процесса с низким энергопотреблением позволяет устройствам Spartan-7 выполнять сложные функции, такие как интерфейс датчиков, управление двигателем и протокол соединения. Установленный Vivado Design Suite предоставляет множество функций, позволяющих сэкономить время и позволяющих дизайнерам создавать сложные чувствительные к стоимости проекты на Spartan-7 с относительно небольшими усилиями.

Оптимизация ввода/вывода с высокой производительностью на ватт. Непревзойденная производительность и энергоэффективность при наименьших затратах Если ваши требования к питанию или производительности столь же сложны, как и ваши затраты, обращайтесь к ПЛИС Spartan-7. Изготовленное с использованием процесса HPL 28 нм TSMC, это семейство объединяет обширные возможности архитектуры ПЛИС серии Xilinx 7 с небольшим форм-фактором и RoHS-совместимой упаковкой для наиболее оптимизированного решения для подключения в портфеле серии 7. Эффективная архитектура CLB 7-й серии, улучшенный DSP и блочная RAM позволяют снизить энергопотребление примерно на 50% по сравнению с предыдущими Spartan семействами и в то же время повысить производительность на 30%. 32-разрядный RISC-процессор MicroBlaze обеспечивает 200-мегапиксельную вычислительную мощность на устройстве Spartan-7. Устройства Spartan-7 обеспечивают, в частности, ключевые возможности подключения и обработки на промышленном, автомобильном, информационно-развлекательном, потребительском и коммуникационном рынках. Лидирующая в отрасли поддержка инструментов и IP с помощью Vivado Design Suite. Начните работу с создания правильного блочного дизайна, используя обширный каталог из более чем 200 доступных 7-серийных IP-решений в Vivado Design Suite IP Integrator. Для быстрого развертывания процессора MicroBlaze доступны предварительные настройки для случаев использования микроконтроллера, процессора реального времени и процессора приложений. Начните с предустановки, затем дополнительно настройте конкретные функции процессора в соответствии с конкретными потребностями вашего приложения. Затем расширьте свою процессорную систему MicroBlaze, используя перетаскивание IP-адресов из каталога периферийных устройств с поддержкой драйверов, таких как ШИМ, UART, последовательные интерфейсы и т. д. Ускорьте замыкание синхронизации и увеличьте использование на 20%, используя экспертную оценку Vivado Design Suite и маршрутные технологии. Проверьте свой дизайн с меньшими хлопотами, используя симулятор смешанного языка без ограничений строки кода, без каких-либо дополнительных затрат. Процессор MicroBlaze, периферийные устройства drag-n-drop, версия Vivado HLx Design Suite WebPACK и комплект разработки программного обеспечения на основе Eclipse — все это бесплатно от Xilinx, что позволяет вам использовать самые быстрые и недорогие инструменты проектирования для этих устройств.

Особенности 28-нм TSMC:

- Масштабируемая архитектура CLB 7-й серии

- Гибкие LUT настраиваются как логические, распределенное ОЗУ или регистры сдвига

- От логических ячеек 6K — 102K для интеграции на уровне

- Множество эффективных интегрированных блоков для снижения стоимости спецификации, включая двойные 12-разрядные аналого-цифровые преобразователи XADC с контролем напряжения питания и контроля температуры

- Оптимизированный выбор стандартов ввода/вывода встроенная обработка с помощью программного процессора MicroBlaze

- 200+ процессоров DMIP MicroBlaze в конфигурации микроконтроллера, процессора реального времени или прикладного процессора

- Встроенная емкость блока памяти до 4,2 МБ

- Блочная оперативная память с огромной гибкостью

- Эффективная и высокопроизводительная блочная оперативная память с байтовой записью позволяет и дополнительная конфигурация FIFO

- 36K-блоки можно разделить на две независимые 18K-блоки RAM.

- Поддержка DDR3 / DDR2 / LPDDR2

- Скорость передачи данных до 800 Мбит/с (пиковая пропускная способность 25,6 Гбит/с)

- Максимальная гибкость распиновки

- Мастер программного обеспечения для сопровождения всего техпроцесса

- Скорость передачи данных LVDS до 1,25 Гбит/с, с суммарной полосой пропускания до 240 Гбит/с

- Стандарты и протоколы от 3,3В до 1,2В ввод/вывод

- Интерфейсы памяти HSTL и SSTL

- Регулируемые скорости нарастания для добавления целостности сигнала

- Эффективные срезы DSP48E1 управляют высокопроизводительной арифметикой и обработкой сигналов

- Каждый срез содержит быстрый множитель 18x25 шириной с 48-битным аккумулятором и 25-битным предварительным сложением

- Возможность 176GMAC до 551 МГц

- Конвейерная обработка, балансировка, каскадирование, SIMD поддержка, интегрированное распознавание образов и расширенная безопасность проектирования ALU Снижение стоимости системы, повышение надежности и защита вашего дизайна.

- Серийный номер устройства и идентификатор eFUSE

- AES256 de шифрование и аутентификация SHA-256 для битового потока

- Контроль несанкционированного доступа и ответная реакция

- Малый корпус, соответствующий требованиям RoHS 6/6

- 8–27мм места на плате с минимальным шагом 0,5–1 мм