О мостиковых схемах и асинхронной логике

Александр Кушнеров

10.01.2025

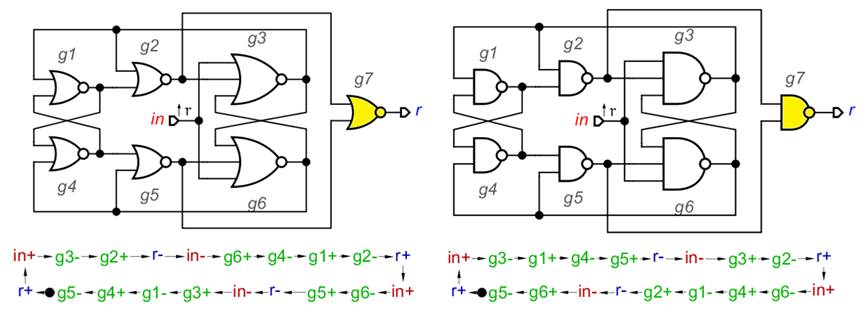

Аннотация – Дизайн замкнутых комбинационных схем основан на законах поглощения конъюнкций и дизъюнкций. Если в такой схеме используется только один выход, то её транзисторная реализация будет избыточной, а граф этой реализации будет содержать ложные циклы. Значения на выходах комбинационной схемы, в том числе и замкнутой, можно считать правильными лишь через какое-то время, необходимое для завершения всех переходных процессов. В статье показано как дополнить замкнутую схему индикатором завершения переходных процессов, т.е. сделать её асинхронной.

1. Введение

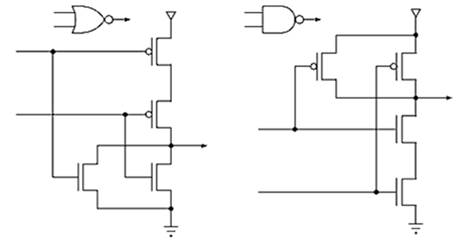

Замыкание выхода комбинационной схемы на один или несколько её входов может дать новую комбинационную схему. Поскольку данные обрабатываются от входов к выходам, обратную связь можно представить как направленную петлю на графе. С другой стороны, графы, которые задают контактные мостиковые схемы, содержат не направленные петли (циклы). Именно из-за петель такие схемы часто являются минимальными. Преобразование графа мостиковой схемы в последовательно-параллельный соответствует схеме на логических элементах. Это преобразование размыкает все петли и называется декомпозиция в базисе И/ИЛИ. Мы будем рассматривать декомпозицию, которая даёт минимальное количество логических элементов. Чтобы корректно замкнуть полученные схемы нужно выполнить определённые условия. В качестве этих условий мы используем известную замкнутую схему.

В инженерной практике релейно-контактные мостиковые схемы начали использоваться по крайней мере со второй половины 1890-х годов [1]. Однако, привлечение булевой алгебры для их анализа и синтеза состоялось лишь во второй половине 1930-х годов [2]. Рассмотрим простейшую мостиковую схему из пяти замыкающих ключей (контактов), назовём её K5. Каждый ключ в этой схеме управляется своей переменной. Присвоить переменные можно например так, как показано в Табл. 1. Последовательное соединение ключей записывается как произведение переменных, а параллельное – как сумма. Таким образом, чтобы записать булеву функцию схемы в дизъюнктивной нормальной форме (ДНФ), нужно найти все возможные пути от входа к выходу.