Comments 14

Зачем убирать под спойлеры текст? Его тут и так, скажем мягко, не слишком много, что девальвирует изначально неплохую идею по написанию англоязычных статей.

P.S. Код выглядит как типовой вариант «перепишем этот С в синтаксисе HDL». Я бы постеснялся такое выкладывать, откровенно говоря.

P.S. Код выглядит как типовой вариант «перепишем этот С в синтаксисе HDL». Я бы постеснялся такое выкладывать, откровенно говоря.

Is this code for fpga or for simulation only? It isn't useful for fpga implementation.

Obviously, a code with the initial keyword can't be implemented in hardware.

Конечно же это не так. Initial — это механизм задания начальных значений, который может быть использован на тех платформах, где это поддерживается.

На каких конкретно?

Ну так все современные FPGA умеют инициализировать триггеры и большинтсво видов блочной памяти. С асиками не знаю, там отдельный разговор.

То есть, вы можете предоставить проект для любой современной ПЛИС, например Cyclone 10 (это современная ПЛИС, не так ли) в котором триггеры будут инициализироааться в блоке initial, и этот проект будет синтезироваться и работать на девборде.

Ну ок, скинете ссылку на гитхаб, посмотрим.

Ну ок, скинете ссылку на гитхаб, посмотрим.

Конечно могу. Такса стандартная — 100$/час. Впрочем могу предложить облегченный вариант, достаточно будет если вы съедите свою шляпу.

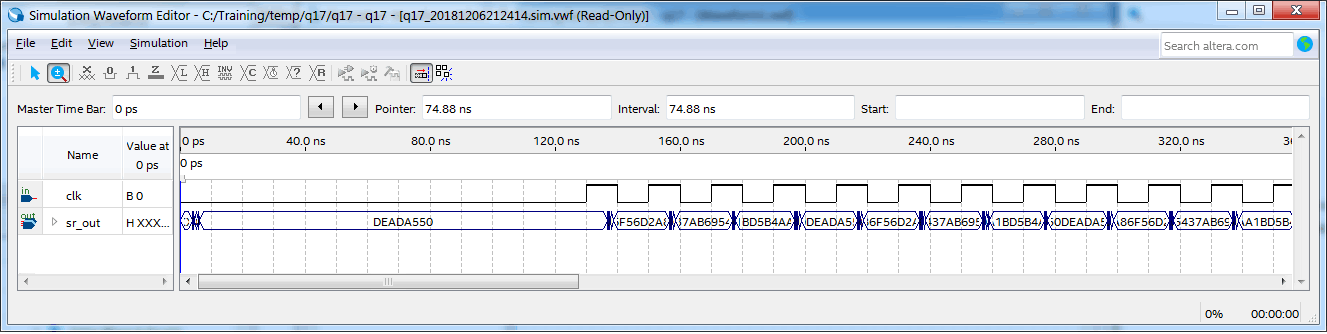

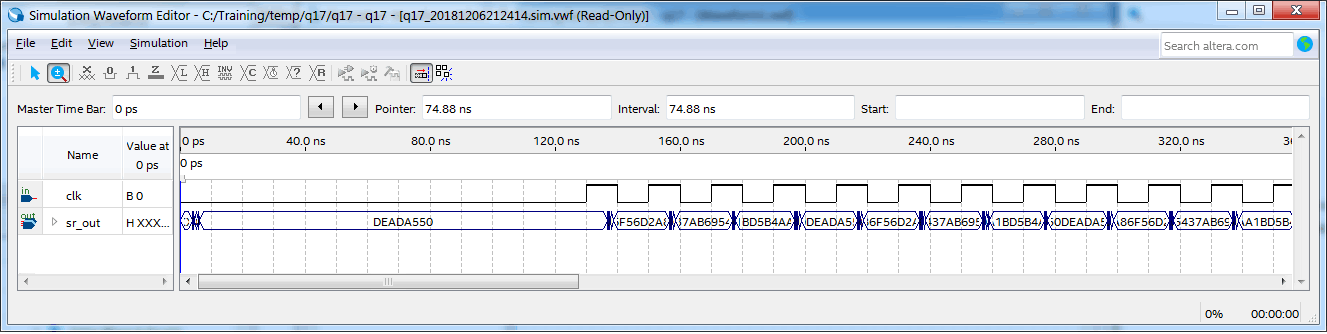

Post-route simulation

module tffmy

(

input clk,

output [31:0] sr_out

);

reg [31:0] sr;

initial

begin

sr = 32'hdeada550;

end

always @ (posedge clk)

begin

sr <= {sr[0], sr[31:1]} ;

end

assign sr_out = sr;

endmodule

set_global_assignment -name FAMILY "Cyclone IV E"

set_global_assignment -name DEVICE EP4CE6F17C8

set_global_assignment -name TOP_LEVEL_ENTITY tffmy

set_global_assignment -name LAST_QUARTUS_VERSION "16.1.0 Lite Edition"

Post-route simulation

Я про остаток имел в виду, что он в общем случае не будет работать и про дурацкое присваивание в always блоке.

с начала времен регистрам и памяти можно было задавать начальные значения.

Мой совет — читайте больше профлитературы на английском.

SLY_G и marks со своими левыми переводами наверняка рвут на себе всё подряд — «а что, так можно было?»

Sign up to leave a comment.

RAM with Simple direct-mapped cache simulation on FPGA in Verilog