Перевод коллективной статьи Practical experiences based on MIPSfpga, не так давно представленной Сарой Харрис на симпозиуме в Торонто. Приводится подробное описание MIPSfpga 2.0, релиз которой состоялся 3 июля 2017 года. Основное, на мой взгляд, отличие по сравнению с версией 1.3: пакет лабораторных работ расширен набором, ориентированным на внутреннюю работу процессора. Так что, если вы хотите узнать, как работает современное ядро, то MIPSfpga 2.0 — это ваш выбор для качественного самообразования. Крайне полезной данная статья будет для преподавателей ВУЗов — подробно и с примерами рассматривается вопрос интеграции MIPSfpga 2.0 в учебный процесс, включая ее соответствие Методическим рекомендациям IEEE/ACM для программ бакалавриата в области вычислительной техники.

В статье присутствует легкий налет маркетинга, но как мне кажется, это не приуменьшает достоинства MIPSfpga 2.0, т.к. ничего похожего по глубине, ширине охвата и ориентированности документации на образовательный процесс среди открытых процессорных ядер пока не наблюдается.

В числе авторов статьи можно отметить Дэвида Харрис и Сару Харрис — авторов популярного учебника по цифровой схемотехнике и архитектуре компьютера, YuriPanchul — которой уже известен аудитории хабра своей активностью по популяризации MIPSfpga и образовательными инициативами в странах СНГ. Стоит упомянуть Роберта Оуэна, который курирует Imagination's University Programme, и Zubair L. Kakakhel, обеспечившего добавление поддержки MIPSfpga в основную ветвь ядра Linux (именно с его кодом в ядре я работал, когда поднимал Linux на MIPSfpga-plus). Ссылка на оригинал статьи: [L1].

Practical experiences based on MIPSfpga

Авторы: Daniel Chaver, Yuri Panchul, Enrique Sedano, David M. Harris, Robert Owen, Zubair L. Kakakhel, Bruce Ableidinger, Sarah L. Harris

В статье обсуждается использование soft-микропроцессора MIPSfpga при преподавании курсов архитектуры компьютера в рамках программ бакалавриата или магистратуры. Его последняя версия (MIPSfpga 2.0) состоит из следующих частей: стартовый пакет (MIPSfpga Getting Started Guide), пакет лабораторных работ (MIPSfpga Labs) и система на кристалле (MIPSfpga System on Chip). В статье дается их краткое описание, приводятся примеры интеграции MIPSfpga в учебную программу, основанные на опыте преподавания в Мадридском университет Комплутенсе, Дармштадтском техническом университете, а также семинарах, которые были проведены в университетах и исследовательских центах России. Доступ к MIPSfpga — промышленному процессорному ядру архитектуры MIPS, включая возможность его исследования и модификации, позволяет студентам преодолеть разрыв между теорией и практикой.

1. Введение

Проект MIPSfpga представляет собой комплексный набор материалов, ориентированных на преподавание архитектуры компьютера и разработанный компанией Imagination Technologies. Помимо исходных кодов ядра MIPS microAptiv UP, он включает учебные материалы и средства разработки. Soft-микропроцессоры используются уже несколько десятилетний, но MIPSfpga – это первое коммерческое ядро доступное под академической лицензией, коды которого не подверглись при этом обфускации. Что позволяет преодолеть разрыв между существующими образовательными программами, построенными с использованием «игрушечных» ядер MIPS архитектуры, и реальными промышленными процессорами MIPS и вспомогательным инструментарием.

Первая версия MIPSfpga, выпуск которой состоялся в июне 2015 года, включает в себя стартовый пакет (Getting Started Guide), который помимо исходных кодов ядра microAptiv UP, также содержит описание процессора, систему на кристалле (СнК), средства отладки и разработки, а также набор скриптов и примеров. Следующий пакет (MIPSfpga Fundamentals) содержит девять лабораторных работ, которые поэтапно знакомят обучаемых с настройкой оборудования, программированием, отладкой, подключением к процессорному ядру различных периферийных устройств. И, наконец, третий пакет (MIPSfpga-SoC) представляет собой систему на кристалле, на примере которой показано, как получить функционирующее под управлением ОС Linux законченное решение, построенное вокруг MIPS ядра, взаимодействующего с памятью (DDR), интерфейсами UART16550, I2C, Ethernet, контроллером прерываний.

В июне 2017 года выпущена вторая версия пакета (MIPSfpga 2.0). Как и ранее, она состоит из трех частей: стартовый пакет (MIPSfpga Getting Started Guide, GSG), набор лабораторных работ (MIPSfpga Labs), который заменил собой пакет MIPSfpga Fundamentals, и систему на кристалле (MIPSfpga System on Chip, SoC). По сравнению с предыдущим релизом пакет GSG дополнен инструкциями о программировании и отладке ядра без использования программатора Bus Blaster, развертывании необходимого для работы с MIPSfpga программного обеспечения на компьютерах под управлением ОС Windows и ОС Linux, добавлено описание модуля верхнего уровня системы MIPSfpga на языке VHDL. В пакет MIPSfpga Labs включено 17 новых лабораторных работ, которые ориентированы на исследование и внесение изменений в ядро на уровне микроархитектуры. Среди них: анализ и модификация структур кэша и контроллера кэша; добавление определяемых пользователем инструкций (UDI) посредством интерфейса CorExtend, использование прерываний и прямого доступа к памяти (DMA) для операций ввода-вывода; показано, как осуществляется внесение изменений в ядро MIPSfpga.

Раздел 2 настоящей статьи описывает пакеты, входящие в состав MIPSfpga 2.0 (стартовый пакет, набор лабораторных работ, система на кристалле), а также анализ того, насколько данные материалы соответствуют Методическим рекомендациям IEEE/ACM для программ бакалавриата в области вычислительной техники (IEEE/ACM Curriculum Guidelines for Undergraduate Degree Programs in Computer Engineering) [1]. Раздел 3 на примере трех курсов показывает, каким образом можно интегрировать MIPSfpga в учебную программу. Раздел 4 описывает проекты, аналогичные MIPSfpga, выводы приведены в Разделе 5.

2. Обзор MIPSfpga 2.0

Проект MIPSfpga состоит из трех пакетов, доступных на ресурсе [2] и рассмотренных в разделах 2.1-2.3. Более подробное описание приведено в [3]. Данные материалы хорошо согласуются теоретическими представлениями, преподаваемыми в рамках курсов компьютерной архитектуры. В разделе 2.4 приводится краткое описание Методических рекомендаций IEEE/ACM для программ бакалавриата в области вычислительной техники [1] и показано, каким образом требования данного документа покрываются MIPSfpga 2.0.

2.1. Стартовый пакет (MIPSfpga Getting Started Guide, GSG)

Первым из рассматриваемых пакетов является GSG, в составе которого поставляются необфусцированные исходные коды процессора MIPS, специально ориентированного для развертывания на ПЛИС. Данный soft-микропроцессор является версией ядра microAptiv UP, которое, в частности, применено в популярном микроконтроллере Microchip PIC32MZ. Он представляет собой набор файлов (на языке Verilog), содержащих описание процессора с 5-ступенчатым конвейером и набором инструкций MIPS32r3 [4]. Также в пакете идут средства для разработки и отладки (Codescape MIPS SDK Essentials и OpenOCD), описание ядра MIPSfpga и построенной на его базе системы, руководство по использованию MIPSfpga и программного инструментария, набор скриптов и примеров (прим. переводчика: в состав GSG входит проект СнК, достаточной для запуска bare metal кода. Более сложная СнК, ориентированная на запуск Linux, представлена в пакете MIPSfpga-SoC).

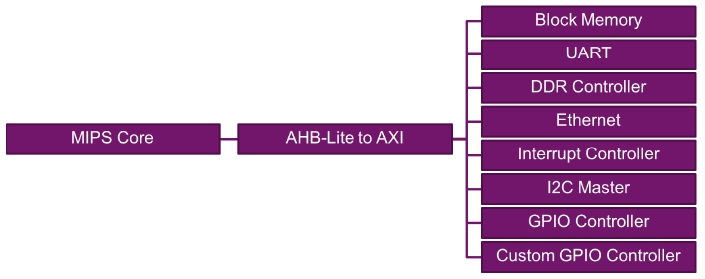

Рисунок 1. Система MIPSfpga

Показанная на Рисунке 1 система MIPSfpga состоит из ядра (MIPS Core) и периферийных устройств, которые подключены к нему с помощью шины AHB-Lite. Периферийные устройства включают в себя память (в данном случае используется блочная память ПЛИС, block RAM) и интерфейс ввода/вывода общего назначения (GPIO), с помощью которого обеспечивается доступ к светодиодам и переключателям на отладочной плате ПЛИС. С учетом того, что многие университеты в учебных курсах используют Verilog или VHDL, модуль верхнего уровня MIPSfpga 2.0 присутствует в двух вариантах — для каждого из перечисленных языков.

Для работы с MIPSfpga необходима отладочная плата с ПЛИС и программатор (отладчик) BusBlaster (примечание переводчика: можно использовать и более доступный отладчик, см. [L2]). Несмотря на то, что в приведенных примерах рассматриваются только Nexys4 DDR и DE2-115, документация содержит подробную инструкцию для тех, кому необходимо портировать систему MIPSfpga на отладочные платы с более скромными возможностями (такие как Basys3 или DE0). Кроме того, в руководстве описываются шаги по скачиванию, установке и использованию инструментария, необходимого для работы с MIPSfpga, включая средства симуляции и синтеза (Vivado или Quartus II), необходимые для конфигурирования ПЛИС, а также средства разработки. Для их работы необходимо компьютер под управлением ОС Windows или Linux.

Стоит отметить, что между Imagination Technologies и проектами Europractice и MOSIS заключено партнерское соглашение, в рамках которого академическим и исследовательским центрам предлагается доступ к ядру MIPS для его использования при производстве Multi Project Wafer (MPW) – до 100 участков. Под это соглашение подпадают ядра 5100 и 5150 класса Warrior M. Данный класс является расширением семейства microAptiv, ориентированным на решения интернета вещей (Internet of Things), носимые устройства (wearable) и иные встраиваемые применения. Таким образом, исследователи получают доступ к эволюционно последней версии того же ядра, что использовано в составе MIPSfpga. Эти ядра предлагаются в полной конфигурационной комплектации, включая блок вычислений с плавающей точкой (FPU), DSP, набор инструкций microMIPS и блок аппаратной виртуализации, необходимый для решений с особыми требованиями в части безопасности. Все это позволяет позиционировать MIPSfpga как комплексное образовательное решение, которое можно использовать как в составе курсов компьютерной архитектуры, так и при преподавании более сложных разделов магистерской программы, включая доступную для исследовательских проектов возможность реализации конечного решения в кремнии.

2.2. Лабораторные работы (MIPSfpga Labs)

Второй из пакетов MIPSfpga предназначен для практических занятий по компьютерной архитектуре и проектированию систем на кристалле на базе проекта СнК, входящего в GSG. Для успешного выполнения лабораторных работ обучаемым необходимы начальные знания в части цифровой схемотехники, архитектуры компьютера и набора инструкций MIPS (ISA) [5]. Опыт разработки программного обеспечения будет при этом полезным, но не является обязательным, т.к. необходимые вещи могут быть освоены в процессе выполнения работ.

В состав пакета входит 25 лабораторных работ, которые позволяют обучаемому пройти через процедуры первичной настройки системы MIPSfpga, изучить сложные взаимодействия, которые происходят внутри ядра и системы на его базе. Лабораторные работы можно условно поделить на 4 части: вводная, ввод-вывод, микроархитектура, память. В вводных лабораторных работах (№1-4) показано, как выполнить развертывание системы MIPSfpga, ее программирование и отладку. На примере работ, посвященных вводу-выводу (№5-13) объясняется порядок подключении к системе новых периферийных устройств. Третья группа лабораторных работ (№14-19) погружает обучаемого в детали микроархитектуры процессорного ядра microAptiv – сердца MIPSfpga. И, наконец, последний набор (№20-25) посвящен исследованию и внесению изменений в иерархию памяти. Таблица 1 содержит список лабораторных работ, более детальное описание которых приведено ниже.

Таблица 1. Лабораторные работы MIPSfpga

Первая часть (вводная) состоит из 4 лабораторных работ, которые знакомят с инструментарием, необходимым для работы с MIPSfpga. В работе №1 изучается сборка проекта MIPSfpga под конкретную ПЛИС средствами ПО Vivado от Xilinx или ПО Quartus II от Altera (прим. переводчика: ныне Intel), на примере плат Basys3 и DE0 показан порядок развертывания MIPSfpga на различных отладочных платах. Работы №2,3 объясняют порядок использования Codescape SDK (содержит MIPS-сборки gcc и gdb) и аппаратного отладчика Bus Blaster для компиляции программ на С и ассемблере, их загрузки в память с последующим запуском и отладкой на MIPS-процессоре, развернутом на ПЛИС. Работа №4 содержит набор дополнительных практических задача по программированию.

Вторая часть начинается с 5 работ, посвященных взаимодействию с отображаемыми в память устройствами ввода-вывода. По мере их выполнения система MIPSfpga взаимодействует со все более сложной периферией: 7-сегментный индикатор, миллисекундный счетчик времени, излучатель звука для воспроизведения музыки, два устройства с интерфейсом SPI (LCD и датчик освещенности). Для работ №7-9 необходимы дополнительные компоненты, что описано в [3].

В работах №10-12 рассматриваются более сложные темы, такие как прерывания и прямой доступ к памяти (DMA). Базовые принципы использования прерываний в процессорах MIPS объясняются в работе №10. Тут же демонстрируется, как прерывания помогают избежать периодического опроса периферийных устройств, освобождая при этом процессорное время для вычислений или иных задач не связанных с вводом-выводом. В следующих работах рассматривается анализ, проектирование, построение и тестирование модуля прямого доступа к памяти (№11) и модуля шифрования по стандарту DES (№11). И, наконец, в работе №13 на практическом примере объясняется порядок настройки и использования счетчиков производительности, доступных в ядрах microAptiv. Предлагается несколько упражнений по оценке производительности программы, предполагающих использование счетчиков и различных типов событий. Данный механизм также используется для оценки эффективности программ в работах №14-25.

В третьей части лабораторных работ производится погружение во внутреннюю работу ядра: показано использование отдельных особенностей microAptiv, интерфейса CorExtend, детально описывается работа конвейера при выполнении инструкций. Первые 4 работы (№14-17) посвящены работе внутренних компонент ядра microAptiv и его конвейера. Изучается, как обрабатываются инструкции ADD, AND, LW и BEQ. Сперва описываются стадии конвейера microAptiv и показывается, как декодированная инструкция проходит через каждую из них. После этого во время пошаговой симуляции, с привязкой к Verilog-коду показаны основные сигналы, относящиеся к обработке данных инструкций. И, наконец, обучаемые получают задание проанализировать отдельные управляющие сигналы, исследовать дополнительные инструкции, добавить новые инструкции в набор поддерживаемых microAptiv команд.

В работе №18 объясняется и показывается работа блока разрешения конфликтов (Hazard Unit). Здесь же вводится использование делителя тактовой частоты, с помощью которого система может работать в диапазоне частот от нескольких МГц до 1 Гц. Снизив тактовую частоту и подключив управляющие сигналы процессорного ядра (конвейера, блока разрешения конфликтов, сигналы вытеснения кэша) к светодиодам отладочной платы, пользователи получают возможность в реальном времени изучить поведение программы.

Последняя из работ данной части (№19) посвящена использованию интерфейса CorExtend, который доступен в процессорах MIPS. Он является мощным инструментом, позволяющим объявить и реализовать пользовательские инструкции (User Defined Instruction, UDI). С помощью CorExtend пользователь может путем подключения специализированного аппаратного модуля к процессорному ядру увеличить скорость выполнения критичных участков алгоритма по сравнению с тем, что может быть достигнуто с использованием стандартного набора команд MIPS32. В работе описываются особенности интерфейса CorExtend, его возможности, ограничения, размещение модуля внутри ядра процессора, временные характеристики, взаимодействие блока пользовательских команд с конвейером microAptiv, предусмотрено несколько практических упражнений экспериментального плана.

В последней группе лабораторных работ исследуется система памяти MIPSfpga, начиная с кэша (№20-24) и заканчивая реализацией внутренней (сверхоперативной) памяти инструкций (Scratchpad RAM, №25). Анализ работы системы памяти MIPSfpga начинается с демонстрации попаданий и промахов кэша на примере нескольких программ с выводом соответствующей информации на LED (№20).

В работе №21 анализируются различные типы массивов, из которых состоит используемый ядром кэш (массивы Data, Tag и Way Select). В работе описан как интерфейс кэша, так и его реализация. После детального объяснения обучаемые получают задачу реализовать и протестировать новую конфигурация кэша, а также опробовать несколько подходов к оптимизации кода используя счетчики производительности.

Следующие три лабораторных работы посвящены реализации контроллера кэша. В работе №22 анализируется управление попаданиями и промахами, описываются основные стадии, структуры и сигналы участвующие в событии попадания или промаха. Все это иллюстрируется с помощью симуляции. И, наконец, предлагаются упражнения по исследованию системы кэширования, например, путем оценки накладных расходов (miss penalty) связанных с промахом кэша. Работа №23 описывает политики управления кэшем, поддерживаемые ядром microAptiv UP. Перед обучаемыми ставиться задача оценить различные политики записи (write policy) и выделения линии кэша (allocation policy), а также реализовать новые политики замещения (Replacement policy). И, наконец, в работе №24 объясняется функционирование буфера записи (Store Buffer), который временно сохраняет данные до момента их записи в каш данных. И буфера заполнения (Fill Buffer), содержащего блок, который следует поместить в кэш данных после промаха.

Наконец, в работе №25 показано, как добавить в MIPSfpga сверхоперативную память инструкций (Instruction Scratchpad RAM). В базовой конфигурации MIPSfpga присутствует соответствующий интерфейс, но нет реализации данного модуля. В данной лабораторной работе показано, как добавить сверхоперативную память в состав системы и взаимодействовать с ней посредством контроллера кэша инструкций/данных.

Закончив с лабораторными работами, обучаемые готовы к разработке более сложных проектов, таких как добавление поддержки новых периферийных устройств (к примеру, I2C или UART), новых возможностей в процессорное ядро (блок аппаратной предвыборки или предсказатель переходов) или систему памяти (второй уровень кэша или way predictor), или любых других заданий на выбор преподавателя.

2.3. Система на кристалле (MIPSfpga-SoC)

Последний из пакетов MIPSfpga 2.0 демонстрирует, как на базе процессорного ядра построить систему на кристалле под управлением ОС Linux — операционной системы с открытым исходным кодом. Дается детальное (поуровневое) описание устройства СнК (как элемента встраиваемой системы), обеспечивающей выполнение сложных программ.

СнК под управлением Linux построена на базе процессорного ядра MIPS управляющего периферийными устройствами посредством шины AHB-Lite. На шине процессор выступает ведущим устройством, периферийные модули – ведомыми. В качестве периферийных устройств используются Xilinx-специфические IP ядра, что существенно сокращает время разработки системы. (Примечание переводчика: а также делает невозможным запуск оригинальной MIPSfpga-SoC на ПЛИС других производителей. Выходом из этой ситуации является MIPSfpga-plus [L3] – аналогичный проект СнК, но с платформонезависимой периферий). Все периферийные устройства подключены к процессорному ядру с помощью шины AHB-Lite с отображением устройства в память (memory-mapped I/O). В связи с тем, что управление периферийными модулями Xilinx производится по шине AXI (Advanced eXtensible Interface) в состав системы (между процессором и периферией) включен соответствующий конвертер интерфейсов (мост) «AHB-Lite to AXI». Из всех устройств СнК, только процессорное ядро и модуль GPIO предоставлены Imagination Technologies, вся остальная периферия – IP модули Xilinx. Простой GPIO-модуль позволяет на примере взаимодействия процессорного ядра с кнопками и светодиодами разобраться в построении и подключении периферийного устройства.

Рисунок 2. Упрощенная структура СнК под управлением Linux

Операционную систему Linux можно условно разделить на две части: пользовательское пространство (Linux Userspace) и ядро (Linux Kernel). Приложения в пользовательском пространстве взаимодействуют с аппаратным обеспечением с помощью стандартного набора предоставленных ядром системных вызовов. Для построения пользовательского пространства MIPSfpga-SoC используется программный пакет Buildroot, который отличается большими возможностями по масштабированию. Ядро взаимодействует с аппаратным обеспечением и обеспечивает уровень абстракции. Для запуска ядра Linux в СнК должны быть выполнены как минимум следующие требования: процессор с поддержкой MMU, контроллер прерываний, прерывания таймера, интерфейс UART, память, интерфейс EJTAG. Заметим, что все перечисленное присутствует в системе, представленной на Рисунке 2.

Кроме того, в состав MIPSfpga-SoC входит набор патчей для Linux, которые добавляют поддержку системы в ядро ОС. Так как процессорное ядро microAptiv UP и периферийные модули уже поддерживаются ядром, то используется уже присутствующий в нем код и добавляется только описание платформы MIPSfpga-SoC. Для того чтобы запустить Buildroot на ядре СнК, его сборка осуществляется под архитектуру mips32r2. В результате мы получаем систему, на которой можно запускать приложения, использующие стандартные GNU C библиотеки.

2.4. Методические рекомендации IEEE/ACM для программ бакалавриата в области вычислительной техники

Перечень блоков (учебных тем), относящихся к области знаний Архитектура компьютера и определенных Методическими рекомендациями IEEE/ACM для программ бакалавриата в области вычислительной техники приведен в Таблице 2.

Таблица 2. Блоки в соответствии с Методическими рекомендациями IEEE

Лабораторные работы MIPSfpga обеспечивают широкое покрытие данных блоков. Появившаяся в начале 80х архитектура MIPS определила многие решения, которые были использованы и в более поздних архитектурах. Поэтому она играет ключевую роль в истории развития архитектуры вычислительных систем и соответствует тематике блока CE-CAO-1. Лабораторные работы №2-3 предполагают создание проектов в Vivado, компиляцию, запуск и отладку программ, что соответствует блоку CE-CAO-2. Тема измерения производительности (CE-CAO-4) затрагивается в лабораторной работе №13 при работе со счетчиками производительности. Которые используются для оценки влияния различных событий и комбинаций выполняемых инструкций на производительность ядра и его элементов. Кроме того, счетчики производительности задействованы в ходе лабораторных работ №14-25. В работе №14, в частности, изучается выполнение команды ADD и других арифметических инструкций, что соответствует теме CE-CAO-5.

Архитектура процессора (CE-CAO-6) изучается в лабораторных работах №14-18, которые, в которых, как было отмечено ранее, рассматривается структура конвейера MIPS. В работах №20-25 представлен исчерпывающий обзор иерархии памяти, включая кэши, сверхоперативную память, что в достаточном объеме покрывает блок CE-CAO-7. Тематике блоков CE-CAO-8 и CE-CAO-9 посвящены работы №5-20, где рассматриваются подключение различных устройств ввода-вывода к системе MIPSfpga, взаимодействие, построенное на обработке прерываний, передача данных с использованием прямого доступа к памяти, шифрование.

В связи с тем, что MIPSfpga – это одноядерная система, последние два тематических блока, посвященные многоядерным и распределенным системам (CE-CAO-10 и CE-CAO-11) не нашли отражения в материалах. Тем не менее, на базе MIPSfpga могут быть построены более сложные системы, т.к. она открыта для использования в академических целях. В качестве примера авторы [6] путем внесения масштабных изменений в код MIPSfpga разработали 120-ядерную система, которую развернули на отладочной плате Terasic DE5-NET FPGA.

3. Практический опыт использования MIPSfpga

MIPSfpga 2.0 уже использовалась для чтении курсов, проведения семинаров и хакатонов. В данной главе приведены три примера интеграция MIPSfpga в образовательный процесс, а также приведено несколько дополнительных примеров использования системы. Во всех рассматриваемых случаях MIPSfpga используется для преподавания курсов Архитектуры компьютера и проектирования систем на кристалле.

3.1. Мадридский университет Комплутенсе

В течение второго семестра 2016/2017 учебного года (с февраля по июнь 2017) MIPSfpga 2.0 использовалась в Мадридском университет Комплутенсе в рамках преподавания курса Архитектуры компьютера и встраиваемых систем — предмета, который является обязательным для получения диплома инженера в области систем связи и преподается на четвертом году обучения. Студенты данного курса показывают уверенные базовые знания в области цифровой схемотехники, VHDL, архитектуры компьютера (набор инструкций MIPS, одно- и многоядерные процессоры, подсистема ввода-вывода) и программирования (С++). Ниже приведено описание этого курса, лабораторных работ, критериев оценки, а также отзывы обучаемых.

3.1.1. Описание курса

12-недельный курс состоит из 24 полуторачасовых лекций (2 в неделю) разделенных на 4 модуля. Модуль №1 посвящен материалам, которые были изучены ранее: набор команд MIPS, одно- и многоядерные процессоры, система ввода-вывода. В модуле №2 изучается конвейер процессора MIPS, на примерах и задачах изучается его реализация. Модуль №3 посвящен иерархии кэша, а №4 является введением в системы на кристалле и встраиваемые системы. MIPSfpga 2.0 идеально подходит для данного курса.

В качестве основного учебника используется [5] с акцентом на главы 4 (языки описания аппаратуры), 6 (Архитектура), 7 (Микроархитектура) и 8 (Память и система ввода-вывода). Более того, используются идущие с книгой слайды, которые были доработаны для того, чтобы связать MIPSfpga и изучаемую теорию: добавлены материалы по MIPSfpga, а также сравнение MIPSfpga (Рисунок 1) и конвейерной реализации процессорного ядра, систем памяти и ввода-вывода, приведенных в [5].

3.1.2. Практические занятия

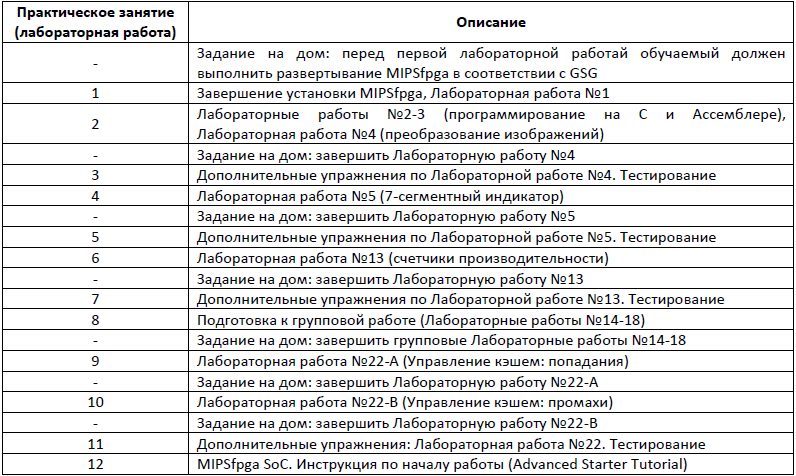

Практические занятия чередуются с 24 полуторачасовыми лекциями (примечание переводчика: для того, чтобы не создавать путаницу здесь и далее под Лабораторной работой понимается входящая в состав пакета MIPSfpga, а под практическим занятием – работа, проведение которой предполагается в соответствии с учебным курсом конкретного ВУЗа). Курс предполагает 12 еженедельных практических занятий, по 2 часа каждое. Учитывая, что в состав MIPSfpga входит 25 интенсивных лабораторных работ, они не могут быть выполнены в полном объеме, поэтому используется только часть: №№1-5, 13-18, 22 (описание лабораторных работ приведено в Таблице 1). Кроме того, используется пакет MIPSfpga-SoC. В Таблице 3 приводится перечень лабораторных работ и их соответствие описанным в предыдущем разделе модулям:

Таблица 3. Распределение лабораторных работ по модулям

Расписание работ приведено в Таблице 4. Очевидно, что проведению лабораторной работы должно предшествовать объяснение соответствующих теоретических концепций. Так перед проведением практического занятия №2 рассматривается набор команд MIPS, перед занятием №4 – система ввода вывода, объяснение работы конвейерного процессора и системы памяти – перед занятиями №6 и №9 соответственно. В первой лекции, которая проводится за несколько дней до практического занятия №1, обучаемым предоставляются отладочные платы Nexys4 DDR и аппаратные отладчики Bus Blaster. Дается задание выполнить загрузку пакета MIPSfpga GSG c ресурса [2], и установку необходимых программ в соответствии с идущими в нем инструкциями (в частности, для Windows — Приложения B и D, для Linux – Приложение G). Помимо этого, необходимо выполнить тестирование развернутой конфигурации (Разделы 4.1, 4.2.1 и 7.4 – для Windows, Раздел 4 и приложение G – для Linux). Также на первой лекции обучаемые получают задание приступить к самостоятельному изучению языка Verilog (Глава 4 книги [5]), т.к. имеющиеся у них знания касаются языка VHDL.

Таблица 4. Практические занятия

Выполнению каждой из лабораторных работ отводится 1-2 практических занятия. К примеру, работа №13 выполняется на занятиях №6 и №7: начало работ в ходе занятия №6, завершение в ходе самостоятельной (домашней) работы в промежутке между занятиями №6 и №7. В ходе последующего практического занятия (№7) студенты выполняют дополнительные упражнения и проходят тест, вопросы которого связаны с темой лабораторной работы.

Лабораторные работы №№14-18 выполняются группами по 3-4 человека. Каждая из 5 групп во время самостоятельной работы выполняет одну из 5 лабораторных работ и затем в течении 1 часа объясняет эту работу остальным обучаемым. После презентации выделяется 30 минут на вопросы и обсуждение.

Все учащиеся, которые посещали практически занятие, смогли справиться с большей частью лабораторных работ. Более 60% обучаемых справились с наиболее сложными заданиями (завершающая часть работ №№13-17) с минимальной помощью преподавателя или вообще без таковой.

3.1.3. Итоговая оценка

Итоговая оценка обучаемого определялась следующим образом: 0.5FE + 0.3LM + 0.2*TM, где FE – оценка по результатам экзамена, LM – оценка за лабораторные работы, в основном базирующаяся на результатах тестирования (Таблица 4), TM – оценка по результатам работы в группе.

3.1.4. Отзывы о курсе

Нам бы хотелось поблагодарить студентов, участвовавших в этом курсе (P. Fernandez, M. Sanchez, G. Diaz-Tejeiro, C. Oliver, J. Alvaro, A. Villarin, M. Cereceda, M. Perez, A. Dorda, P.M. Teba, F.J. Oliva, E.I. Quezada, D. Fernandez, J.A. Canadas, A. Menendez, J. Martin, I. Diaz) за чтение данного доклада и их ценные комментарии. Отзывы студентов: «Курс, а особенно лабораторные работы, дает исчерпывающее понимание архитектуры компьютера» (G. Diaz-Tejeiro); «Лабораторные работы позволили нам разобраться, как работает коммерческое процессорное ядро» (M. Sanchez); «Качество и полнота лабораторных работ облегчают обучение» (J. Martin); «Вначале было очень трудно привыкнуть к новому способу обучения. Однако, после того как мы освоили основные навыки, нам начал нравится предмет, и мы получили отличные знания о том, как работают ядро, кеш, ввод-вывод и другие элементы. По-моему, это лучший способ изучения подобного предмета» (A. Menendez). «Лабораторные работы позволили нам на практики реализовать те концепции, о которых рассказывали на лекциях» (P. Fernandez). «Лабораторные работы продемонстрировали применение концепций архитектуры компьютера в реальном мире» (A. Villarin).

3.2. Дармштадтский технический университет

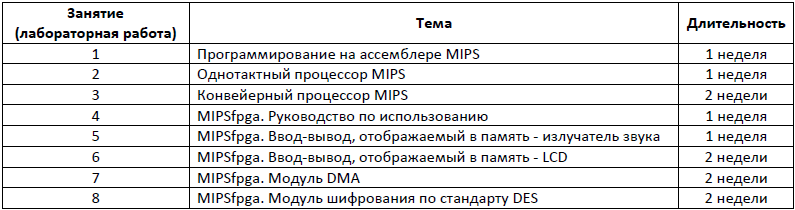

Во втором семестре 2015/2016 в Техническом университете Дармштадта (TUD) в Германии преподавался курс под названием «Основы архитектуры процессора и ввод-вывод, отображаемый в память». 14-недельный курс состоит из еженедельных лекций и недельных или двухнедельных практических занятий (лабораторных работ). В Таблице 5 представлен обзор восьми практических занятий и связанных с ними лекций. Первые три занятия построены на книге [5]. Для оставшихся (№№4-8) используются лабораторные работы из пакета MIPSfpga (Таблица 1).

Таблица 5. Распределение лабораторных работ по темам

Первые три лекции и практические занятия основаны на главах 6 и 7 книги [5] и служат введением в набор команд MIPS и архитектуру процессора. Остальные лекции и практические занятия основаны на презентациях и лабораторных работах, входящих в состав пакета MIPSfpga. Занятие №4 (MIPSfpga. Руководство по использованию) объединяет в себе Лабораторные работы №№1-3 (Таблица 1). Для остальных практических занятий использованы Лабораторные работы MIPSfpga №7, 9, 11 и 12 соответственно.

В лекциях 1-3 рассказывается про набор команд MIPS, тракт данных и устройство управления, архитектуру конвейерного процессора. Введение в процессор и систему MIPSfpga, а также окружение разработчика – тема следующих двух лекций. Последние 4 лекции посвящены следующим темам: отображаемый в память ввод-вывод и его использование при взаимодействии с периферийными устройствами; беглый обзор последовательного интерфейса и работа с ЖК-экранами (LCD); прямой доступ к памяти (DMA) и его реализация с использованием шины AHB-Lite; стандарт шифрования DES. Четыре недели перед окончанием семестра свободны от лекций – обучаемым дается время на завершение последних двух лабораторных работ. Однако, по согласованию с преподавателем в этот период могут читаться лекции на дополнительные темы.

В течение первой недели курса студенты получают необходимое оборудование (FPGA плата Nexys4 DDR, аппаратный отладчик Bus Blaster, звукоизлучатель, ЖК-экран, соединительные провода и конденсаторы). В ходе первого практического занятия выполняется развертывание необходимого программного инструментария (в соответствии с инструкциями из состава GSG). Помощь консультантов в лаборатории доступна в течение 2-4 часов в неделю, при этом многие обучаемые выполняют задание дома и посещают практические занятия, только если им необходима помощь в отладке. От студентов получены положительные отзывы, курс пользовался популярностью. Все записавшиеся на курс 42 студента завершили его.

3.3. Семинары в России, Украине и Казахстане

В течении 2015-2016 года была проведена серия коротких семинаров, посвященных MIPSfpga в девяти лучших университетах России, Украины и Казахстана: Национальный исследовательский университет «МИЭТ», Московский государственный университет имени М. В. Ломоносова, Национальный исследовательский ядерный университет «МИФИ», Университет ИТМО, Самарский государственный аэрокосмический университет, Московский физико-технический институт, Алматинский университет Менеджмента, Компания Наутех (прим. переводчика – так в оригинале), Национальный технический университет Украины «КПИ». Кроме того, MIPSfpga был представлен на четырех мероприятиях в России и Казахстане: Microchip Masters Russia, на конференции в Казахском национальном техническом университете, конференции SECR, а также лекциях Nanometer ASIC в Национальном исследовательском технологическом университете «МИСиС». Данные мероприятия привлекли широкий круг участников. Начиная от студентов, имеющих некоторый опыт программирования встраиваемых систем, но без опыта разработки аппаратного обеспечения. И заканчивая опытными специалистами по проектированию ASIC, которые для своих экспериментов с программно-аппаратным кодом ищут недорогую платформу, основанную на ПЛИС, имеющую коммерческое ядро и зрелую поддержку со стороны средств разработки.

Семинары 2015 года послужили подтверждением того, что погружение в MIPSfpga проходит гораздо продуктивнее, если студенты уже знакомы с основами цифровой схемотехники, архитектуры компьютера и микроархитектуры. Перед знакомством с MIPSfpga обучаемые (к примеру, с использованием упрощенного ядра MIPS из [5]) должны изучить такие базовые темы, как структура процессора, конвейер, приостановки (stalls) и пересылка данных через байпас (forwarding). И только после этого они могут с использованием MIPSfpga начать эксперименты с коммерческим ядром, наблюдая за его конвейером, работой кэша, добавляя сопроцессоры, периферийные устройства в СнК, конструируя многоядерные системы. Данный подход был положительно принят университетами (какими как МИЭТ, ТИМО и КПИ), в которых преподавание уже построено с использованием несложных процессорных ядер, написанных на HDL. В числе отзывов, полученных на семинарах, прозвучало предложение исследователей из Московского государственного университета по использованию кода MIPSfpga в качестве исчерпывающего теста для новых EDA инструментов. Отдельные идеи, прозвучавшие при обсуждении, были учтены в версии MIPSfpga 2.0. Такие как: возможность снижения тактовой частоты (до 1 Гц), загрузка программ в синтезированную СнК с использованием USB-UART конвертера, что исключает необходимость использования аппаратного отладчика Bus Blaster, а также новые лабораторные работы, акцентированные на внутренней работе процессорного ядра и CorExtend.

Семинары 2016 года были объединены с другими курсами. В Алматинскам университете Менеджмента занятия по MIPSfpga проводились в конце вводного курса разработки на HDL — начинающим разработчикам было продемонстрировано решение отраслевого уровня. На семинарах Nanometer ASIC MIPSfpga использовался для прототипирования системы на кристалле, после чего описывался маршрут проектирования ASIC на примере MIPS M5150 (родственное по отношению к MIPS microAptiv UP ядро, которое предлагается в рамках Europractice). И, наконец, в Национальном техническом университете Украины был организован хакатон [8], где группы студентов интегрировали MIPSfpga с датчиками, работающими по протоколам SPI, I2C и иным. Мероприятие оказалось успешным и подтвердило корректность поставленной задачи: половина участвующих собрали работающие решения и попутно познакомились с RTL-разработкой и системной интеграцией.

Результатом этих семинаров стало формирование в России и Украине большой группы разработчиков, делающих свой вклад в появляющееся сообщество MIPSfpga. К примеру, двумя группами были разработаны CorExtend сопроцессоры ([9] и группа в МИЭТ, г. Зеленоград). Ряд расширений для MIPSfpga разработаны Станиславом Жельнио: интерфейсный модуль работы с SDRAM; контроллер прерываний; интегрированный с Visual Studio Code отладочный интерфейс; добавлена поддержка UART16550 с прицелом на запуск Linux на плате Terasic DE10-Lite (прим. переводчика: работа по созданию платформонезависимой периферии для MIPSfpga ведется в рамках проекта MIPSfpga-plus [L3], подробно эта активность, а также использование данной СнК описаны в статьях [L4]-[L13]). Некоторые из проектов будут представлены на конференции NGC-17 в Томске, включая проекты по интеграции MIPSfpga с популярной системной шиной Wishbone (МИЭТ) и добавлению в систему VGA-контроллера (Борис Ивашинников из Комсомольского-на-Амуре государственного технического университета). Кроме того, несколько преподавателей, в том числе Илья Кудрявцев из Самарского Национального исследовательского университета, обсудят интеграцию таких проектов в русло университетской программы.

4. Аналогичные проекты

В данном разделе представлен анализ существующих soft-микропроцессоров и описаны другие материалы, доступные при обучении архитектуре компьютера. Каждый из альтернативных проектов кратко сравнивается с MIPSfpga 2.0

4.1. Другие soft-микропроцессоры

Компаниями Xilinx и Altera предлагаются их собственные soft-микропроцессоры Nios/Nios II [10] и MicroBlaze [11] соответственно, специально адаптированные под ПЛИС. Однако них есть свои недостатки: закрытые исходные коды, что существенно ограничивает их использование, они не построены на промышленных/коммерческих ядрах и не поддерживают применяемый в коммерческих решениях набор команд, им не хватает документации, ориентированной на учебный процесс. Также существует альтернатива от ARM c закрытыми исходными кодами: Cortex M0 Design Start [12] – низкопроизводительное ядро начального уровня (8K gates). Его код обфусцирован, а отсутствие EJTAG ограничивает возможности отладки. Не обеспечена возможность реализации в кремнии для академических нужд. При этом есть набор обучающих материалов.

Существуют также несколько ядер с открытыми исходными кодами. Наиболее известными альтернативными являются семейства ядер OpenSPARC [13] (разработка Oracle и Sun Microsystems) и LEON [14] (разработка Aeroflex Gaisler и Европейского Космического Агентства). Не смотря на то, что это интересные ядра, к ним отсутствуют хорошие обучающие материалы, а реализованный набор команд (SPARC RISC) не так широко распространен в академической среде как MIPS. Две другие заслуживающие упоминания альтернативы с открытым исходным кодом: RISC-V [15], разработанный в Калифорнийском университете Беркли, и openRISC, разработанный на opencores.org [16]. Эти ядра не поддерживают применяемый в коммерческих решениях набор команд, как и в предыдущих случаях есть некие учебные материалы.

С другой стороны, в MIPSfpga отсутствуют все упомянутые выше ограничения. Это промышленное процессорное ядро с открытым исходным кодом, не подвергнутом обфускации, используемое в коммерческих устройствах типа микроконтроллера PIC32MZ компании Microchip. В нем реализован набор инструкций (MIPS32r3) широко используемый в академической среде и описанный в литературе. Проектом MIPSfpga предоставляется обширная документация, включая большое количество обучающих материалов и лабораторных работ. Что, как показано в данной статье, идеально соответствует темам типовых учебных курсов по архитектуре компьютера. Ядро MIPSfpga поддерживается на всех платформах ПЛИС, включая как Xilinx, так и Altera и может быть легко портировано на ПЛИС других производителей.

4.2. Иные материалы для изучения архитектуры компьютера

В работе [17] представлено HIP-окружение (прим.переводчика: скорее всего речь о Hypothetical processor), на примере которого студенты изучают как работает конвейер процессора. В нем используется 5-ступенчатая реализация soft-микропроцессора, которая напоминает ранние ядра MIPS-архитектуры. Отладочная плата с ПЛИС, на которую загружено ядро, подключена к компьютеру, где в графическом интерфейсе отображается текущее состояние ядра на каждом шаге. Набор инструкций данного ядра включает 52 инструкции, чему далеко до полной поддержки MIPS32r3, присутствующей в MIPSfpga. Кроме того, в составе данного проекта отсутствует набор лабораторных работ, а книга, описывающая ядро доступна только на словенском языке. С другой стороны, у MIPSfpga отсутствует графический интерфейс, зато у преподавателей и обучаемых есть неограниченный доступ к исходным кодам ядра, что позволяет получить значение любого сигнала или регистра внутри процессора с помощью инструментов симуляции.

Авторы работы [18] представили проект BZK.SAU — симулятор архитектуры компьютера. Его набор инструкций включает 59 реализованных команд. Простейшие ядра, наподобие этого позволяют студентам экспериментировать с некоторыми изучаемыми ими концепциями, но они не преодолевают разрыв между книжной теорией и промышленной практикой. Кроме того, последняя работа основана исключительно на симуляции, в том смысле, что студенты не могут загрузить скомпилированный проект в ПЛИС и экспериментировать «на железе».

В лабораторных работах CNP, представленных в [19], на одном не сложном окружении проводится обучение основам архитектуры компьютера, компиляторам и сетевым технологиям. Центральной частью данного пакета является MinIPS – конвейерный процессор, в котором реализован усеченный набор инструкций MIPS. В соответствии с этим набором команд спроектирован и идущий в комплекте компилятор — Tiny C. Не смотря на то, что лабораторные работы MIPSfpga не ориентированы на изучение компиляторов или сетевых технологий, ничто не мешает преподавателю данных предметов использовать MIPSfpga при проведении практических занятий.

Набор инструкций MIPS32r3 широко известен и хорошо документирован, поэтому преподаватель может реализовать свой собственный компилятор или выбрать один из существующих и поддерживающих MIPS, таких как: Codescape MIPS SDK, gcc, или LLVM. Кроме того, пример пакета MIPSfpga-SoC показывает, что подключение к ядру MIPSfpga контроллера Ethernet – является вполне реализуемой задачей.

И, наконец, в работе [20] представлен курс по продвинутой многоядерной архитектуре. Этот курс выходит за первоначальные рамки MIPSfpga, но, как уже упоминалось ранее, преподаватели могут адаптировать MIPSfpga GSG под свои нужды, как это показано в [6].

4.3. Выводы

В этой статье представлен анализ последней версии MIPSfpga, выпущенной в июне 2017 г. и ее применение для проведения семинаров и учебных курсов. Как показано в данной публикации, учебная инфраструктура MIPSfpga идеально соответствует темам, преподаваемым в рамках курсов архитектуры компьютера. Более того, при использовании MIPSfpga в процессе обучения, студенты сталкиваются с проблемами, аналогичными тем, которые должен решать инженер-разработчик.

Среди них можно упомянуть: интеграцию периферийных устройств в СнК, добавление новых инструкций, как с использованием стандартного интерфейса (такого как CorExtend), так и путем внесения изменений в коммерческое ядро (такое как microAptiv); оценку различных конфигураций и политик работы кэша с использованием счетчиков производительности; построение законченной СнК, основанной на коммерческом ядре и периферийных модулях Xilinx с запуском на нем ОС Linux. Упрощенный подход к обучению (к примеру, представленный в [5] и основанный на сильно примитивном ядре), возможно, больше подходит для начальных курсов бакалавриата. Вместе с тем, переход на использование в преподавании решений промышленного уровня имеет преимущество, так как решаемые при этом проблемы сильно близки к тем, с которыми студентам придется столкнуться в реальном мире. Что делает MIPSfpga прекрасно подходящим решением для обучения старших курсов бакалавриата и магистратуры.

5. Благодарности

Авторы выражают благодарность за вклад в Imagination University Program следующим лицам и организациям: the University of Nevada, Las Vegas, Imperial College London (UK), the ArTeCS group at University Complutense of Madrid (UCM), the Spanish government research contracts TIN2015-65277-R and TIN2015-65316-P, Munir Hasan (IMG UK), Prashant Deokar (IMG India), Mahesh Firke (IMG India) Parimal Patel (Xilinx), Kent Brinkley (IMG USA), Rick Leatherman (IMG USA), Chuck Swartley (IMG USA), Sean Raby (IMG UK), Michio Abe (IMG Japan), Bingli Wang (IMG China), Sachin Sundar (IMG USA), Alex Wong (Digilent Inc.), Matthew Fortune (IMG UK), Jeffrey Deans (IMG UK), Laurence Keung (IMG UK), Roy Kravitz (Portland State University), Dennis Pinto (UCM), Tejaswini Angel (Portland State University), Christian White, Gibson Fahnestock, Jason Wong, Cathal McCabe (Xilinx), and Larissa Swanland (Digilent)

6. Ссылки

[1] CE2016 — Curriculum Guidelines for Undergraduate Degree Programs in Computer Engineering. IEEE and ACM, 2016

[2] Imagination University Program — Resources

[3] Harris, S., Harris, D., Chaver, D., et al.: "MIPSfpga: Using a Commercial MIPS Soft-Core in Computer Architecture Education". IET Circuits, Devices and Systems, 2017.

[4] Imagination Technologies Ltd., "MIPS32 microAptiv UP Processor Core Family Datasheet", July 31, 2013

[5] Harris, D., and Harris, S., "Digital Design and Computer Architecture" (Elsevier Science and Technology, 2007, 2nd edn. 2012)

[6] Kumar H B, C., Ravi, P., Modi, G., Kapre, N..: "120-core microAptiv MIPS Overlay for the Terasic DE5-NET FPGA board", Int. Symp. On Field-Programmable Gate Arrays, Monterey, USA, February 2017

[7] Intro HDL design

[8] NTUU Hackathon

[9] CorExtend Interface

[10] Altera — NIOS-II Processor, February 2017

[11] Xilinx — MicroBlaze Soft Processor Core, accessed February 2017

[12] ARM — Cortex M0 Design Start, accessed February 2017

[13] Oracle — OpenSPARC, Feb-2017

[14] Aeroflex Gaisler — LEON series Softcores, accessed February 2017

[15] Waterman, A., Lee, Y., Patterson, D.A., et al., "The RISC-V Instruction Set Manual, Volume I: User-Level ISA", version 2.0, 2014

[16] OpenCores OpenRISC, accessed February 2017

[17] Buli´c, P., Guˇstin, V., ˇSonc, D., and ˇ Strancar, A,.: "An FPGA-based integrated environment for computer architecture", Computer Applications in Engineering Education, 2013, 21, (1), pp. 26-35

[18] Oztekin, H., Temurtas, F., Gulbag, A.: "BZK.SAU: Implementing a hardware and software-based computer architecture simulator for educational purpose". Proc. 2nd Int. Conf. Computer Design and Applications, Qinhuangdao, China, June 2010, pp. 490-497

[19] Abe, K., Tateoka, T., Suzuki, M., Maeda, Y., Kono, K., Watanabe, T.: "An integrated laboratory for processor organization, compiler design and computer networking", IEEE Trans. Education, 2004, 47, (3)

[20] Petit, S., Sahuquillo, et. al: "A research-oriented course on Advanced Multicore Architecture: Contents and active learning methodologies", Journal of Parallel and Distributed Computing, Elsevier, 2017

Дополнительные ссылки

[L2] MIPSfpga и внутрисхемная отладка

[L3] Проект MIPSfpga-plus

[L4] MIPSfpga и SDRAM

[L5] MIPSfpga и прерывания

[L6] MIPSfpga и UART

[L7] Текущая активность вокруг MIPSfpga и не только

[L8] Поднимаем Linux на MIPSfpga и ПЛИС Altera

[L9] Портирование MIPSfpga на другие платы и интеграция периферии в систему

[L10] Подключение периферийных модулей к MIPSfpga, на примере клавиатуры Pmod KYPD

[L11] Подключение периферийных модулей к MIPSfpga, на примере ультразвуковых датчиков расстояния

[L12] MIPSfpga: вне канона

[L13] Как начать работать с MIPSfpga