В архитектуре x86-платформ возникли два течения, взаимно дополняющие друг друга. По одной версии, нужно двигаться в сторону интеграции в одном кристалле вычислительных и управляющих ресурсов. Второй подход исповедует распределение обязанностей: процессор оснащается производительной шиной, формирующей периферийную масштабируемую экосистему. Он положен в основу топологии системной логики Intel C620 для высокоуровневых платформ.

Принципиальное отличие от предыдущего чипсета Intel C610 состоит в расширении канала коммуникации процессора с периферией, входящей в состав микросхемы PCH, за счет использования PCIe-линков наряду с традиционной DMI-шиной.

Рассмотрим подробнее новшества южного моста Intel Lewisburg: какими эволюционными и революционными подходами расширены его полномочия в коммуникации с процессорами?

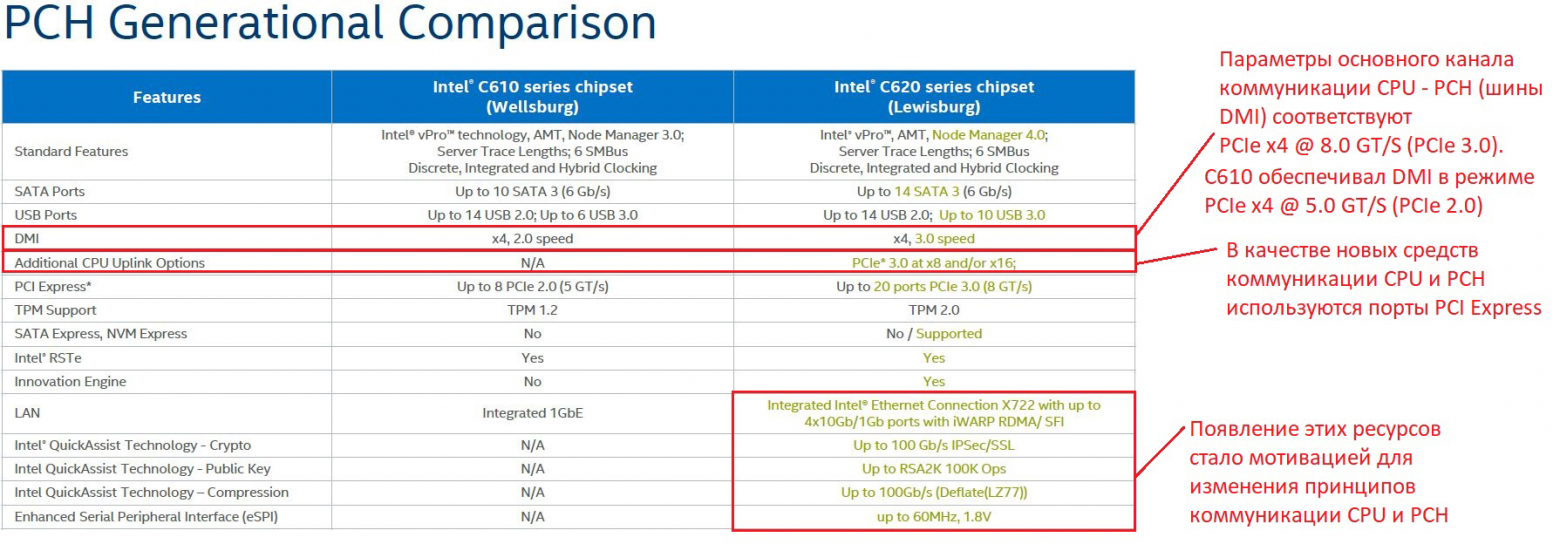

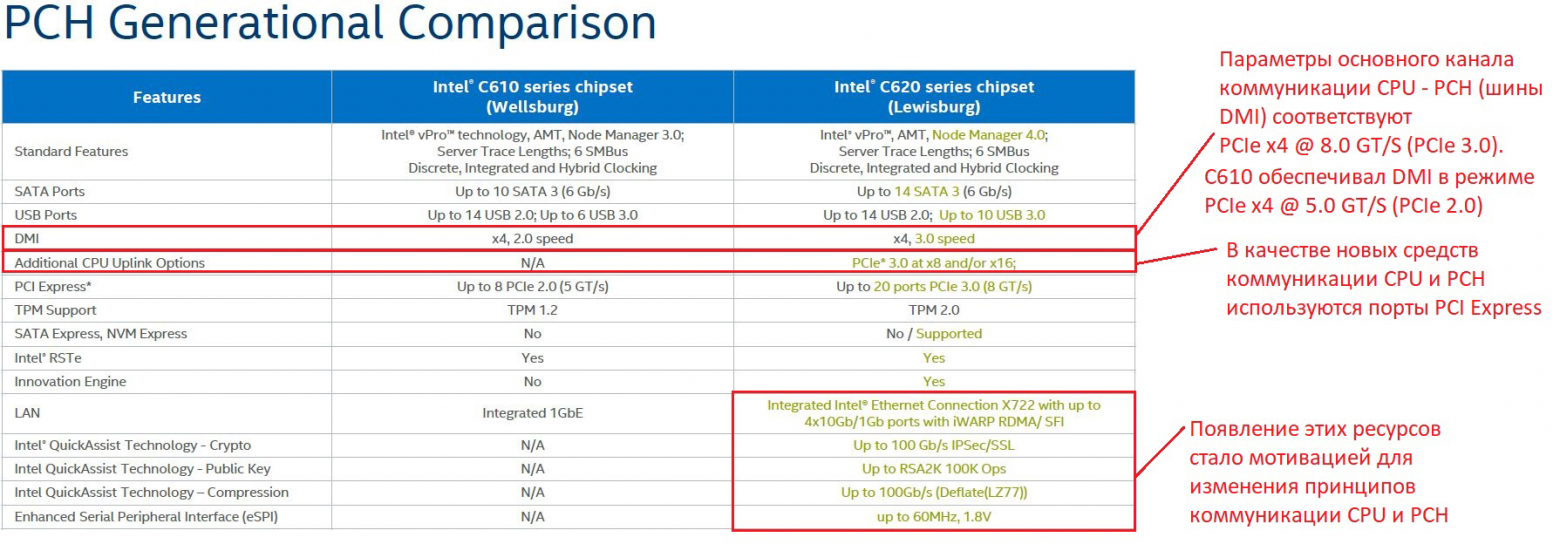

В рамках эволюционного подхода основной канал связи CPU с южным мостом, каковым является шина DMI (Direct Media Interface), получил поддержку режима PCIe x4 Gen3 с производительностью 8.0 GT/S. Ранее, в Intel C610 PCH коммуникация процессора и системной логики выполнялась в режиме PCIe x4 Gen 2 в полосе пропускания 5.0 GT/S.

Сравнение функциональности системной логики Intel C610 и C620

Заметим, эта подсистема значительно консервативнее, чем встроенные PCIe-порты процессора, обычно используемые для подключения GPU и NVMe накопителей, где уже давно применяется PCIe 3.0 и намечен переход к PCI Express Gen4.

К революционным изменениям можно отнести добавление новых PCIe-каналов коммуникации CPU-PCH, называемых Additional Uplinks. Физически, это два порта PCI Express, работающие в режимах PCIe x8 Gen3 и PCIe x16 Gen3, оба — 8.0 GT/S.

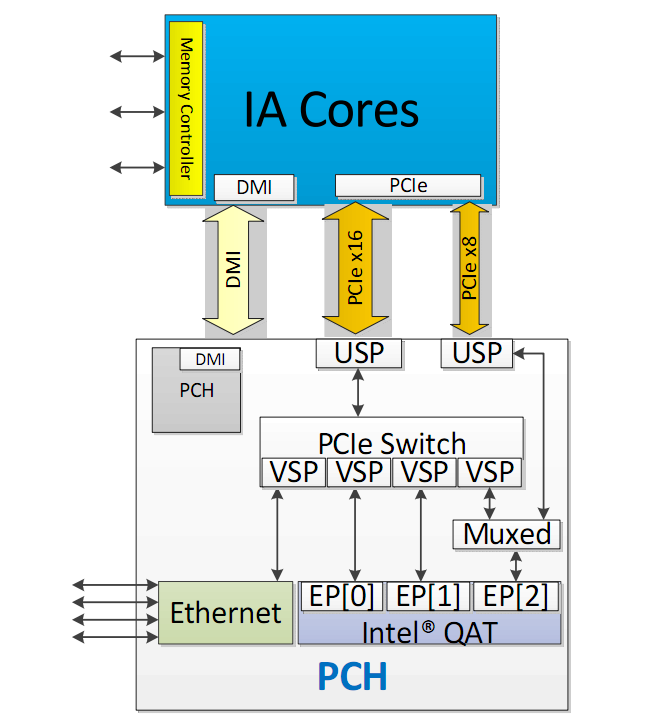

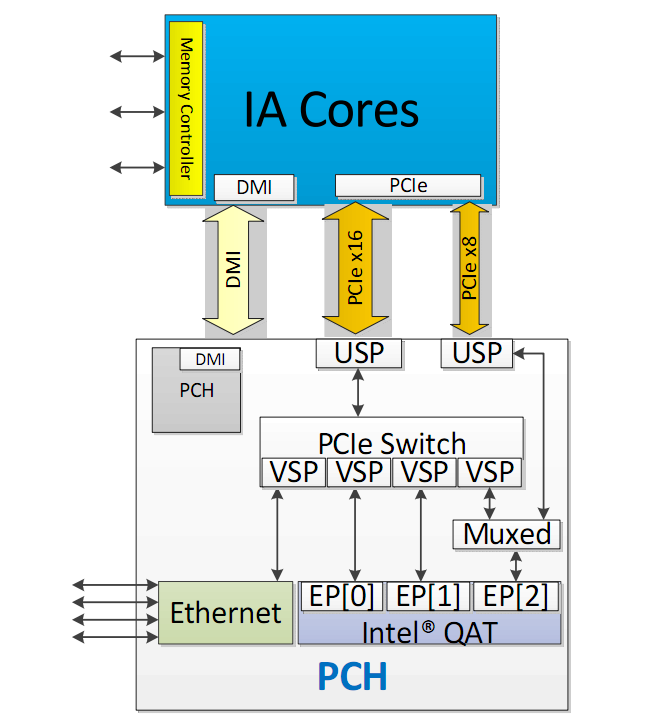

Для взаимодействия CPU и Intel C620 PCH используются 3 шины: DMI и два порта PCI Express

Ради чего потребовался пересмотр существующей топологии коммуникаций с Intel C620? Во-первых, в составе PCH может быть интегрировано до 4x сетевых контроллеров 10GbE с функциональностью RDMA. Во-вторых, за шифрование сетевого трафика и обмена с подсистемой хранения отвечает новое и более быстрое поколение сопроцессоров Intel QuickAssist Technology (QAT), обеспечивающие аппаратную поддержку компрессии и криптования. И, наконец, «двигатель инноваций» — Innovation Engine, который будет доступен только для OEM-производителей.

Важным свойством является возможность опционального выбора не только топологии подключения PCH, но и приоритетов внутренних ресурсов микросхемы в доступе к скоростным каналам связи с центральным процессором (процессорами). Кроме того, в специальном режиме EPO (EndPoint Only Mode), подключение PCH осуществляется в статусе обычного PCI Express устройства, содержащего ресурсы 10 GbE и Intel QAT. При этом классический интерфейс DMI, а также ряд Legacy-подсистем, показанных на диаграмме черным цветом, отключены.

Внутренняя архитектура микросхемы Intel C620 PCH

Теоретически, это дает возможность использовать в системе более одной микросхемы Intel C620 PCH, масштабируя функциональность 10 GbE и Intel QAT в соответствии с требованиями производительности. При этом Legacy функции, нужные лишь в единственном экземпляре, могут быть включены только у одной из установленных микросхем PCH.

Итак, финальное слово в дизайне будет принадлежать разработчику платформы, действующему на основании как технологических, так и маркетинговых факторов в соответствии с позиционированием каждого конкретного продукта.

Принципиальное отличие от предыдущего чипсета Intel C610 состоит в расширении канала коммуникации процессора с периферией, входящей в состав микросхемы PCH, за счет использования PCIe-линков наряду с традиционной DMI-шиной.

Рассмотрим подробнее новшества южного моста Intel Lewisburg: какими эволюционными и революционными подходами расширены его полномочия в коммуникации с процессорами?

Эволюционные изменения в коммуникации CPU-PCH

В рамках эволюционного подхода основной канал связи CPU с южным мостом, каковым является шина DMI (Direct Media Interface), получил поддержку режима PCIe x4 Gen3 с производительностью 8.0 GT/S. Ранее, в Intel C610 PCH коммуникация процессора и системной логики выполнялась в режиме PCIe x4 Gen 2 в полосе пропускания 5.0 GT/S.

Сравнение функциональности системной логики Intel C610 и C620

Заметим, эта подсистема значительно консервативнее, чем встроенные PCIe-порты процессора, обычно используемые для подключения GPU и NVMe накопителей, где уже давно применяется PCIe 3.0 и намечен переход к PCI Express Gen4.

Революционные изменения в коммуникации CPU-PCH

К революционным изменениям можно отнести добавление новых PCIe-каналов коммуникации CPU-PCH, называемых Additional Uplinks. Физически, это два порта PCI Express, работающие в режимах PCIe x8 Gen3 и PCIe x16 Gen3, оба — 8.0 GT/S.

Для взаимодействия CPU и Intel C620 PCH используются 3 шины: DMI и два порта PCI Express

Ради чего потребовался пересмотр существующей топологии коммуникаций с Intel C620? Во-первых, в составе PCH может быть интегрировано до 4x сетевых контроллеров 10GbE с функциональностью RDMA. Во-вторых, за шифрование сетевого трафика и обмена с подсистемой хранения отвечает новое и более быстрое поколение сопроцессоров Intel QuickAssist Technology (QAT), обеспечивающие аппаратную поддержку компрессии и криптования. И, наконец, «двигатель инноваций» — Innovation Engine, который будет доступен только для OEM-производителей.

Масштабируемость и гибкость

Важным свойством является возможность опционального выбора не только топологии подключения PCH, но и приоритетов внутренних ресурсов микросхемы в доступе к скоростным каналам связи с центральным процессором (процессорами). Кроме того, в специальном режиме EPO (EndPoint Only Mode), подключение PCH осуществляется в статусе обычного PCI Express устройства, содержащего ресурсы 10 GbE и Intel QAT. При этом классический интерфейс DMI, а также ряд Legacy-подсистем, показанных на диаграмме черным цветом, отключены.

Внутренняя архитектура микросхемы Intel C620 PCH

Теоретически, это дает возможность использовать в системе более одной микросхемы Intel C620 PCH, масштабируя функциональность 10 GbE и Intel QAT в соответствии с требованиями производительности. При этом Legacy функции, нужные лишь в единственном экземпляре, могут быть включены только у одной из установленных микросхем PCH.

Итак, финальное слово в дизайне будет принадлежать разработчику платформы, действующему на основании как технологических, так и маркетинговых факторов в соответствии с позиционированием каждого конкретного продукта.