Хабр Курсы для всех

РЕКЛАМА

Практикум, Хекслет, SkyPro, авторские курсы — собрали всех и попросили скидки. Осталось выбрать!

Спасибо! Хотелось бы также освещения следующих тем:

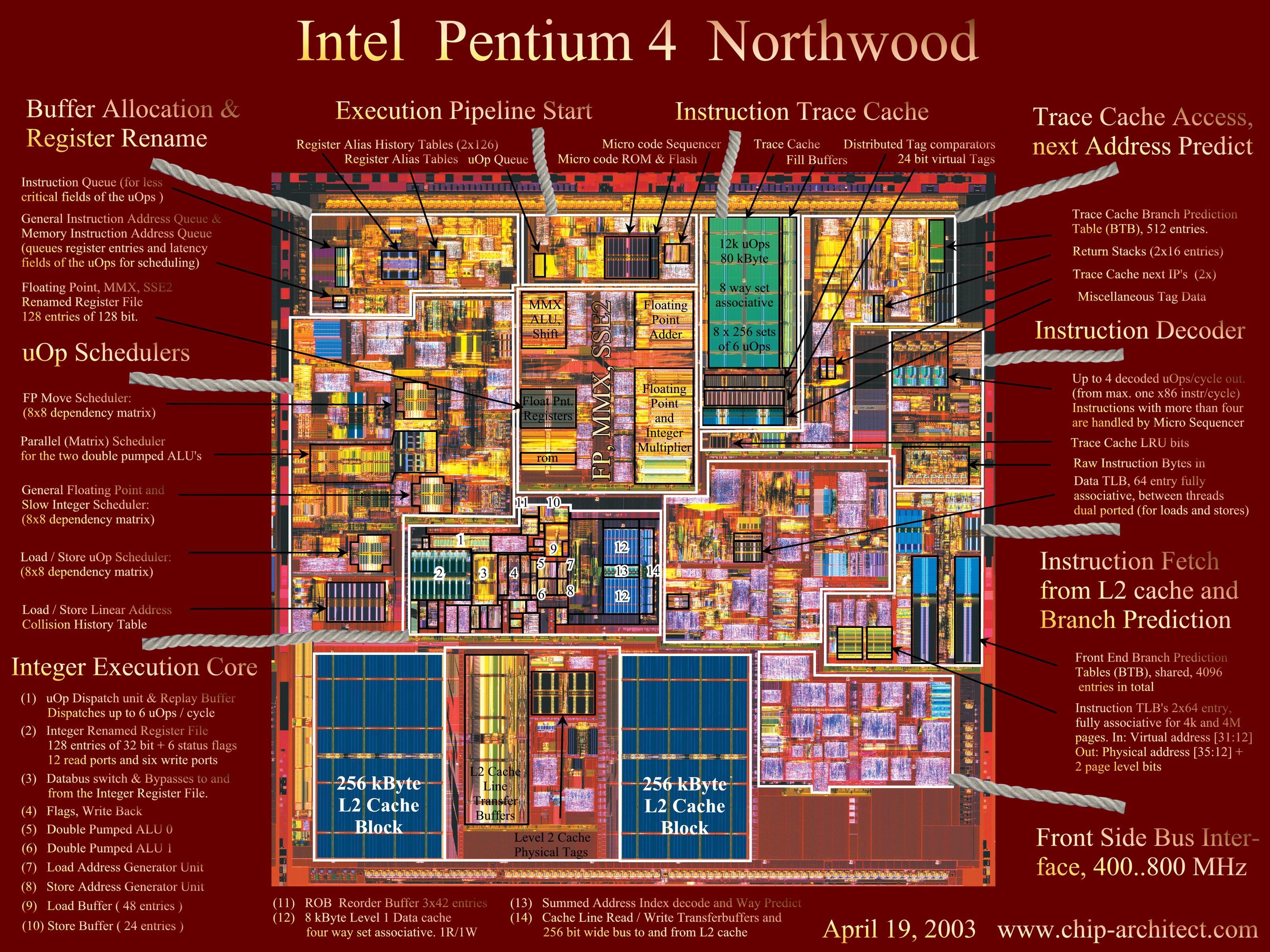

а) Кэш инструкций (вы рассказали только про кэши данных)

б) Архитектура VLIW (Эльбрус)

в) Более подробно про современные архитектуры AMD и Intel

Если процессор видит, что к выполнению готовы две инструкции, и между ними нет зависимости, то он не ждёт, пока они завершатся по отдельности, а выполняет их одновременно. Одна из популярных реализаций такой архитектуры называется Simultaneous Multithreading (SMT) и также известна, как Hyper-Threading.

Знаменитая атака Spectre эксплуатирует баги в предсказании и упреждении переходов. Атакующий использует специально подобранный код, чтобы заставить процессор упреждающе выполнить код, благодаря чему происходит утечка значений из памяти.

Что именно происходит внутри миллиардов транзисторов, благодаря которым работает компьютер? В нашей новой мини-серии из четырёх статей мы рассмотрим процесс создания архитектуры компьтерного оборудования и расскажем о принципах его работы.

Архитектура x86 проприетарна и никто не знает, сколько всего инструкций в ней есть. Обычно считается, что существует несколько тысяч инструкций x86, но точное число никто не публикует.А разработчики компиляторов с помощью шаманского бубна и древних заклинаний в эти самые инструкции наши высокоуровневые эсперанто переводят?

Был даже проект по поиску инструкций, распознаваемые декодером — https://github.com/xoreaxeaxeax/sandsifter

https://dustri.org/b/files/papers/31dd6431a3dd0d26814b4ff4d453c20e8d1292eef2f3ec1f777b8e4ee1852d08_domas_breaking_the_x86_isa_wp.pdf "Breaking the x86 ISA" 2017 — Hidden Instructions

Как разрабатываются и производятся процессоры: основы архитектуры компьютеров