The team developing a set of portable SystemVerilog examples decided to organize the first event in Silicon Valley on Sunday, January 14 from 2PM till 5PM at Hacker Dojo in Mountain View, CA. If the first event is successful we are going to make it recurrent. You can register for the event on Meetup or LinkedIn.

The current directions of the group:

1. Scripts for abstracting FPGA boards to develop board-independent and toolchain-independent SystemVerilog examples. This allows for teaching university courses and running educational seminars with a variety of boards available at a given place. The current state is in basics-graphics-music GitHub repository.

2. Integration of the peripherals to make the classes more interesting. Adding sound generation and recognition, computer graphics and sensors, also with an abstraction level to allow the students to use different microphones and display interfaces with different numbers of color bits per pixel.

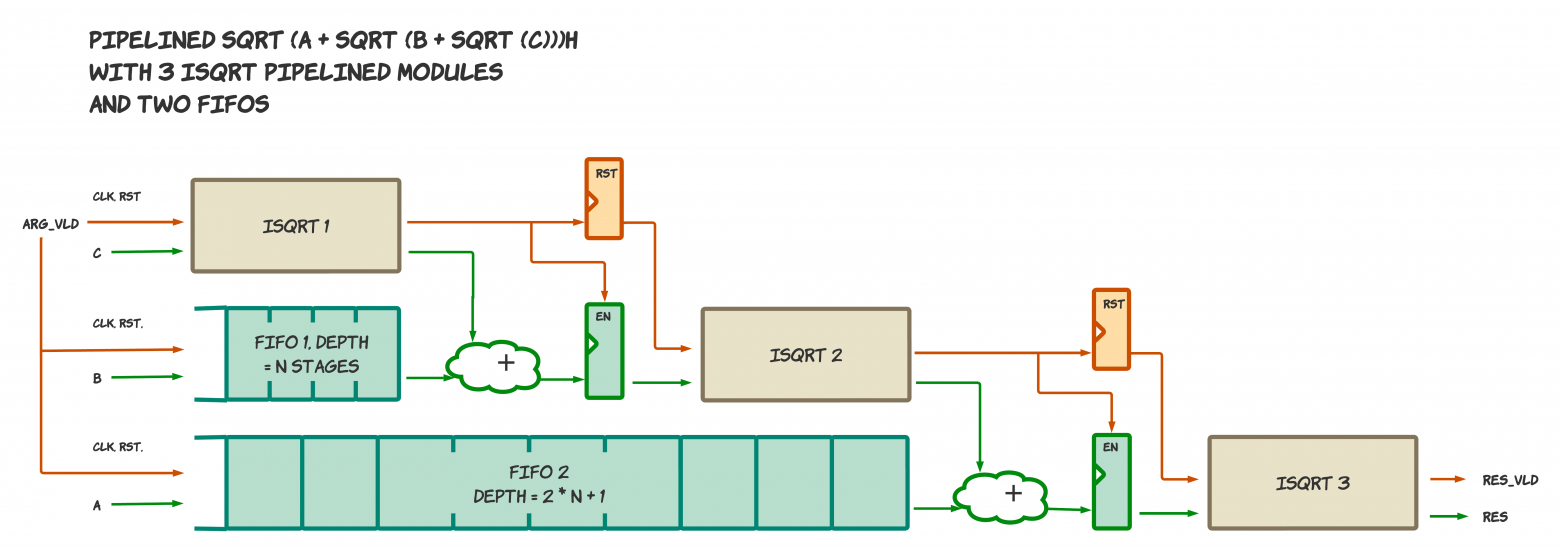

3. The examples and homework exercises to teach the students the mechanics of Register-Transfer Level (RTL) design methodology, the basics of pipelining, flow control, and microarchitectural primitives, such as FIFOs and arbiters. The current public (without solutions) repositories include systemverilog-homework and valid-ready-etc .

4. Wrapping various RISC-V CPU cores in the board-independent platform to give the students an opportunity to compare different microarchitectures, from a simplified single-cycle implementation of a subset of RISC-V architecture - to cache-less MCU-level cores - to more complicated cores with caches, TLB MMU, superscalar execution and the ability to run Linux. The examples we have worked with so far included schoolRISCV and yrv-plus .

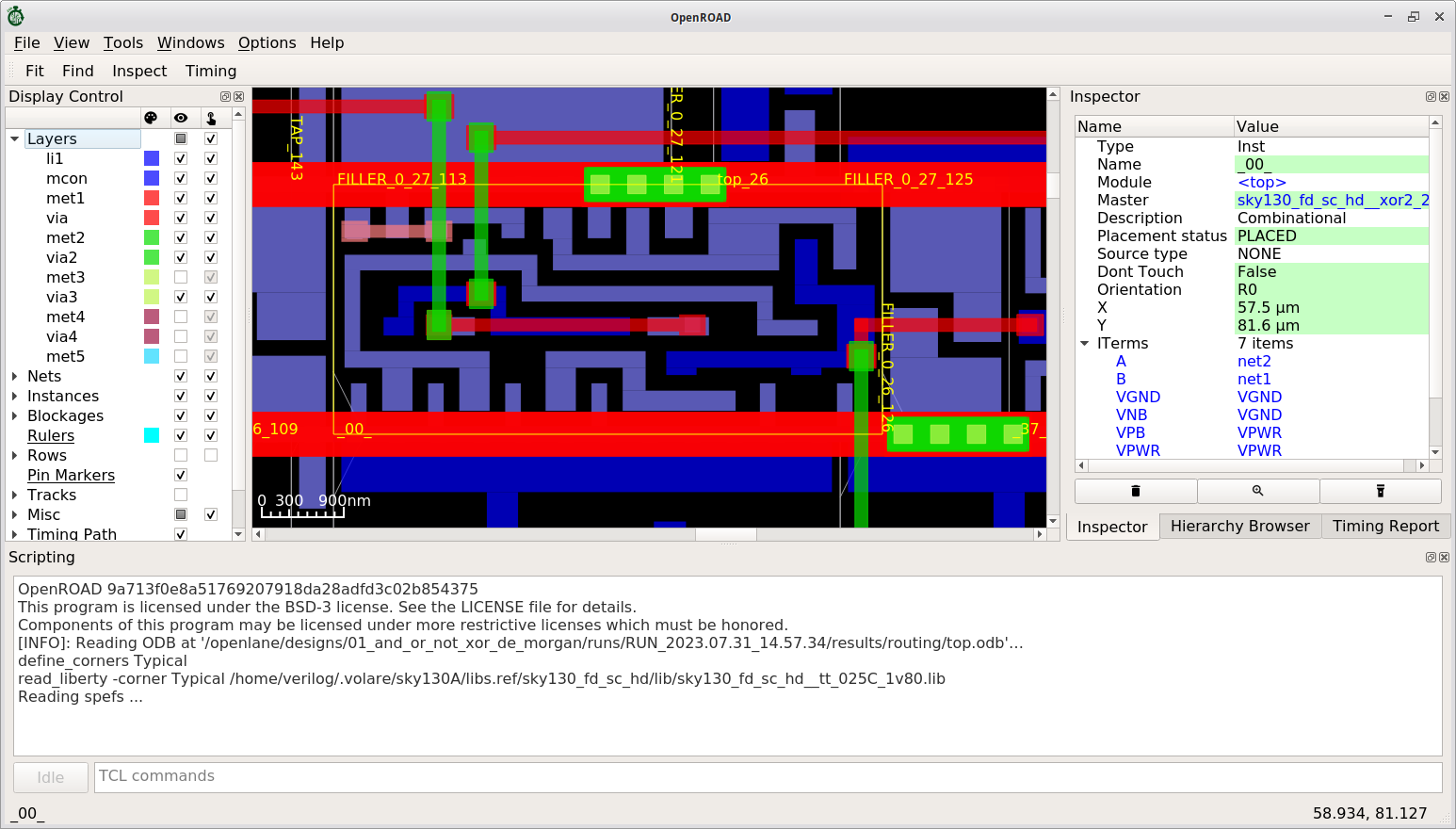

5. Connecting FPGA-based training to ASIC design. Making sure all the microarchitectural and CPU-based examples are synthesizable with Open Lane ASIC synthesis, demonstrating how microarchitecture decisions affect ASIC timing, exploring ASIC platforms like Efabless Caravel, etc.

Altera: RzRd, Piswords-6, Saylinx, Zeowaa, EPI-MiniCY4.

Xilinx: Digilent Basys3, Nexys4, Nexys4-DDR, Nexys A7.

Gowin: Tang Primer 20K Dock.

More details about the scripts for abstracting FPGA boards:

We implemented a push-button synthesis and simulation platform for a set of SystemVerilog examples. The platform is written in a way that the same SV source code works with any of the supported 30 FPGA boards, 5 synthesis toolchains (Altera, Xilinx, Gowin, Lattice, Yosys) and 2 simulators (Icarus and Questa).

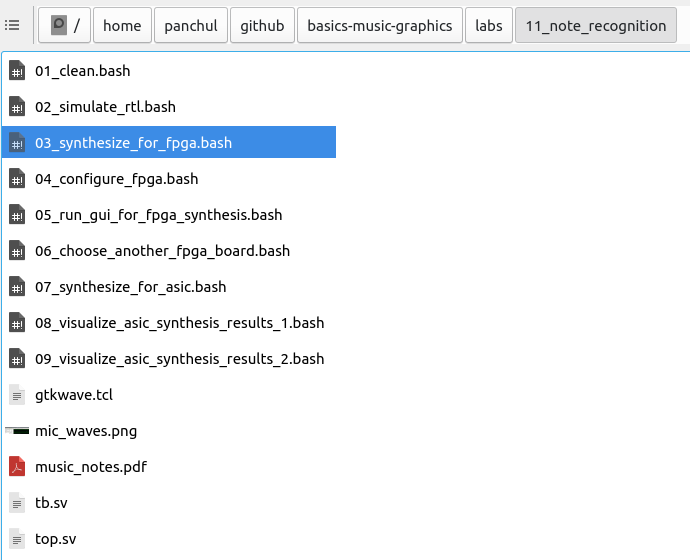

No complicated setup or scripting is required on the part of the platform user. He should install the necessary toolchains to their default locations, clone the example repository, select the board, go to the example directory and run a script, such as 03_synthesize_for_fpga.bash.

The script automatically locates the necessary EDA and board configuration software, creates the project files, runs the synthesis and configures the FPGA on the selected board. The script produces meaningful error messages, so the user does not have to dig through the log files and scripts.

The scripts work under Linux and Windows. For Windows, we are using bash shell from Git. The scripts could be adopted for Windows Subsystem for Linux (WSL), but it was not done yet. If you attempt to run it under WSL, it will ask to run either under true Linux or under true Windows with Git bash.

More details on integration of the peripherals to make the classes more interesting: right now our examples support the following parts:

INMP441 and Pmod MIC3 microphones

I2S audio output via Pmod AMP3 and HiLetgo PCM5102

VGA connectors Pmod VGA and VGA666

External I/O module based on TM1638 chip

TODO: It is necessary to improve support for VGA by adding the parameters for RGB channel width, from 1 to 8 bits per channel.

It is necessary to test and adopt the following peripherals:

HiLetgo and Adafruit I2S MEMS Microphone based on SPH0645LM4H

I2S audio output based on CJMCU-1334 chip.

TM1638-based external I/O module (7-segment, buttons, LEDs) with keyboard matrix.

USB-to-UART interfaces for the examples that require communication of FPGA board with a computer.

HDMI support

Rotary encoder - this is a good task for an exam

Ultrasonic Distance Sensor based on HC-SR04 - this is a good task for an exam

Infrared receiver

We elaborate on board-specific topics in the follow-up article.

Note that FPGA board and periphery support is only a part of the planned activity. It is suitable for those who wants to start or explore another FPGA toolchain. But the more we move we are going to focus on microarchitectural and CPU examples, as well as making sure the code is compatible with Open Lane ASIC synthesis toolchain.

The related posts about the event: