Недавно я все-таки сделал свой первый шаг к ПЛИС и призвал вас за собой. Мое фанатическое увлечение ПЛИС и идея о том, что ПЛИС является лучшей платформой для создания любых устройств приобрела религиозный характер. Моя секта ПЛИСоводов проповедует полный отказ от микроконтроллеров, а особо экстремистская ветвь проповедует отказ не только от софт процессоров, но и вообще от последовательных вычислений!

Недавно я все-таки сделал свой первый шаг к ПЛИС и призвал вас за собой. Мое фанатическое увлечение ПЛИС и идея о том, что ПЛИС является лучшей платформой для создания любых устройств приобрела религиозный характер. Моя секта ПЛИСоводов проповедует полный отказ от микроконтроллеров, а особо экстремистская ветвь проповедует отказ не только от софт процессоров, но и вообще от последовательных вычислений!Как всегда, постижению истин помогло решение реальных задач. В сегодняшней проповеди я хотел бы рассказать об испытаниях, которые выпадают на долю молодого ПЛИСовода. Преодолевая испытания мы постигаем истину. Но остаются вопросы, на которые я не нашел ответов. Поэтому я бы очень хотел, чтобы братья-хабровчане — ПЛИСоводы с опытом, поучаствовали в обсуждении, протянули руку помощи своим младшим собратьям.

Эта статья для новичков. В ней я опишу типичные проблемы, вопросы, заблуждения, ошибки, которые могут появиться в самом начале обучения (потому что они появились у меня). Однако, контекст статьи ограничен тем, что разработка ведется на ПЛИС от Altera в среде Quartus на языке Verilog.

Трудно жить ничего не делая, но мы не боимся трудностей!

Одна из причин, по которой многие не начинают изучать Verilog вот прямо сейчас — это отсутствие реальной ПЛИС. Кто-то не может заказать, потому что дорого, а кто-то потому, что не знает, что именно взять (вопрос выбора рассмотрен в предыдущей статье). Кому-то ПЛИС пока еще едет по почте.

Но в своих разработках я пришел к тому, что наличие реальной ПЛИС мне требуется уже на финальном этапе разработки, когда нужно протестировать проект «в железе». Речь о том, что бóльшую часть времени я провожу в отладке своего кода с помощью симуляторов.

Но в своих разработках я пришел к тому, что наличие реальной ПЛИС мне требуется уже на финальном этапе разработки, когда нужно протестировать проект «в железе». Речь о том, что бóльшую часть времени я провожу в отладке своего кода с помощью симуляторов.Поэтому мой совет: отсутствие ПЛИС — это не повод бездействовать. Пишите и отлаживайте модули для ПЛИС в симуляторах!

Симулятор для Verilog

Итак, чем же развлечь себя скучными длинными рабочими днями (если они таковыми являются)? Конечно же освоеним ПЛИС! Но как же затащить на работу целую среду разработки от Altera, если она весит 3 ежемесячных рабочих лимита интернета? Можно принести на флешке! Но если предметом изучения является Verilog, то можно ограничиться блокнотом, компилятором IcarusVerilog, а результат смотреть в GTK Wave.

Попробовать прямо сейчас

Для начала работы в среде Windows, достаточно скачать по ссылке http://bleyer.org/icarus/ файл установки iverilog-20130827_setup.exe (development snapshot) [11.2MB]

Установка трудностей не вызывает. Теперь немного забежим вперед: создадим папку для проекта и в ней пару файлов с пока что не понятным содержимым:

В файле bench.v описан тестовый модуль testbench, в нем создан тестовый источник сигнала clk (меандр). Другие модули будут создаваться в отдельных файлах, либо логику можно протестировать сначала в этом модуле, а потом вынести в отдельный модуль. Потом в модуль testbench будут добавляться экземпляры этих модулей, где мы будем подавать на их входы тестовые сигналы и получать из них результаты. Из модулей мы можем строить иерархию, думаю это понятно всем.

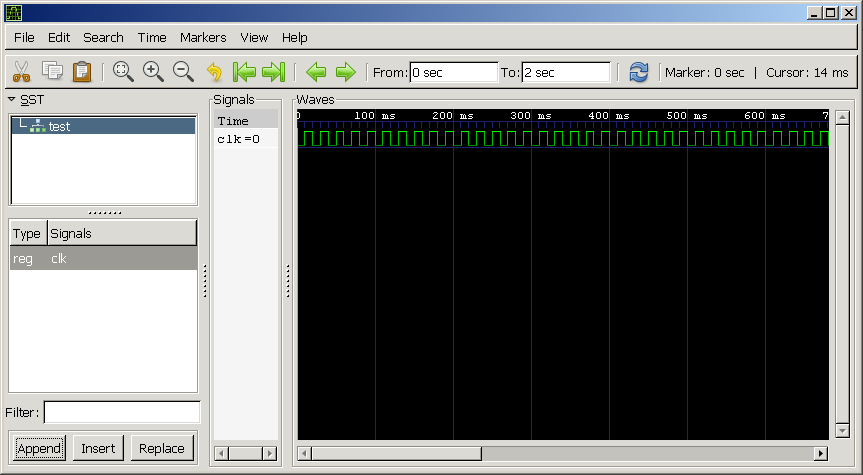

После запуска этого файла мы увидим на экране текст, заданный в $display (это отладочный вывод), значение же сигналов и регистров схемы будут находиться в файле test.vcd. Кликаем по файлу и выбираем программу для просмотра — GTKWave (в моем случае D:\iverilog\gtkwave\bin\gtkwave.exe). Еще пару кликов и мы увидим наш clk.

Установка трудностей не вызывает. Теперь немного забежим вперед: создадим папку для проекта и в ней пару файлов с пока что не понятным содержимым:

Файл-модуль с кодом для тестирования модулей - bench.v

`timescale 1ns / 100 ps module testbench(); reg clk; initial begin $display("start"); $dumpfile("test.vcd"); $dumpvars(0,testbench); clk <= 0; repeat (100) begin #10; clk <= 1; #10; clk <= 0; end $display("finish"); end

В файле bench.v описан тестовый модуль testbench, в нем создан тестовый источник сигнала clk (меандр). Другие модули будут создаваться в отдельных файлах, либо логику можно протестировать сначала в этом модуле, а потом вынести в отдельный модуль. Потом в модуль testbench будут добавляться экземпляры этих модулей, где мы будем подавать на их входы тестовые сигналы и получать из них результаты. Из модулей мы можем строить иерархию, думаю это понятно всем.

BAT Файл, который скомпилирует и просимулирует главный модуль, добавив другие модули из текущей папки - makev.bat

iverilog -o test -I./ -y./ bench.v vvp test pause

После запуска этого файла мы увидим на экране текст, заданный в $display (это отладочный вывод), значение же сигналов и регистров схемы будут находиться в файле test.vcd. Кликаем по файлу и выбираем программу для просмотра — GTKWave (в моем случае D:\iverilog\gtkwave\bin\gtkwave.exe). Еще пару кликов и мы увидим наш clk.

Практически, каждый свой новый модуль я создаю в блокноте и отлаживаю IcarusVerilog. Следующим этапом после такой отладки идет проверка модулей в Quartus. Хотя в Quartus тоже есть свой симулятор, но я его использую реже. Причина в простоте обновления кода и просмотра результата в IcarusVerilog: сохранил изменения в файле, запустил BAT, нажал кнопку «обновить» в GTKWave — все! В ModelSim для этого требуется чуть больше движений, но он тоже не плох, особенно на данных сложных структур.

Практически, каждый свой новый модуль я создаю в блокноте и отлаживаю IcarusVerilog. Следующим этапом после такой отладки идет проверка модулей в Quartus. Хотя в Quartus тоже есть свой симулятор, но я его использую реже. Причина в простоте обновления кода и просмотра результата в IcarusVerilog: сохранил изменения в файле, запустил BAT, нажал кнопку «обновить» в GTKWave — все! В ModelSim для этого требуется чуть больше движений, но он тоже не плох, особенно на данных сложных структур.После симуляции наступает пора запуска Quartus. Но загружать прошивку в ПЛИС пока еще рано. Нужно убедиться, что божественная вычислительная машина правильно поняла, какую схему мы хотим получить, изложив свои мысли в виде Verilog'а.

Разница между симуляцией и работой в реальном железе

Первое время я, подобно слепому котенку, бился головой об косяки. Казалось бы правильный код, не работает совсем, либо работает не так, как предполагаешь. Либо вот только что работал, а теперь внезапно перестал!

Пытливый котенок, начинает искать взаимосвязь между своими действиями и результатом («голубиное суеверием»).

Самая большая драма

Ниже будет список странностей, но сначала самая большая драма, с которой я столкнулся: не все конструкции Verilog могут быть синтезированы в железе. Это связано с тем, что на Verilog описывается не только аппаратная логика, которая объединяется в модули и работает в железе. На том же Verilog описываются тестовые модули, которые объединяют тестируемые модули, подают на их входы тестовые сигналы и в целом существуют только для проверки на компьютере. Изменение значений сигналов во времени задается конструкциями, содержащим знак "#" в тексте Verilog. Такой знак означает задержку во времени. В примере выше именно так генерируется сигнал CLK. И я грешным делом думал, что таким же образом внутри настоящей ПЛИС можно генерировать, к примеру, последовательность бит для отправки сообщения по RS232. Ведь на вход ПЛИС подан сигнал от генератора 50 МГц! Может быть она как-то на него ориентируется. Как оказалось, я не единственный, кто надеялся на чудо: 1, 2, 3, 4, 5. Реальность как всегда оказывается более суровой: ПЛИС это набор логики и временная задержка в ней может появиться при использовании счетчика, значение которого увеличивается тактами от генератора до заданной величины, либо как-то иначе (но всегда аппаратно).

Список найденных странностей

Удивительные вещи, однако, прочтение книг [1,2] проливает свет на эту бесовщину. Более того, обретается благодать.

Если обозначить reg, то не факт, что он будет создан

Как я пришел к проблеме? Допустим есть один модуль, на вход которого я должен подавать значение (по типу параметра). В перспективе, этот параметр должен будет изменяться во времени в зависимости от каких-то внешних событий. Поэтому значение должно хранится в регистре (reg). Но реализация приема внешних событий пока не реализована, поэтому я регистр не меняю, а просто задаю ему изначальное значение, которое в дальнейшем не меняется.

//задаю 8 битный регистр reg [7:0] val; //инициирую его значением initial val <= 8'd0240; //wire к которому подключим выход из модуля wire [7:0] out_data; //неведомый модуль, называется bbox //экземпляр этого модуля называется bb_01 //будем считать, что в модуле есть входной порт in_data и выходной out_data //во входной порт подаем значение с регистра val, а выход подключаем к wire - out_data bbox bb_01(.in_data(val), .out_data(out_data));

Казалось бы в чем подвох? В императивных ЯП мы часто задаем переменные в качестве констант и потом ни разу их не меняем и все работает. Что же мы видим в железе?

Во-первых, мы не видим регистра. Во-вторых, на вход модуля подано 8'hFF вместо наших 8'd0240! И этого уже достаточно для того, чтобы схема заработала не так, как мы планировали. То, что регистра нет — это нормально. В Verilog можно описывать логику разными способами, в то же время, синтезатор всегда оптимизирует аппаратную реализацию. Даже если написать блок always и в нем работать с регистрами, но при этом выходное значение всегда будет определяться входными, то применение регистра тут окажется лишним и синтезатор его не поставит. И наоборот, если при каких то значениях входных данных выходное значение не меняется, то тут никак не обойтись без регистра-защелки и синтезатор его создаст. (Книга 1 стр. 88-89). Что из этого следует? Если мы начнем менять значение регистра, например, в зависимости от нажатии кнопок, то геристр уже будет создан и все будет работать так, как нужно. Если же окажется, что кнопки ничего не меняют, то синтезатор его опять же выкинет и опять все поломается. Что же делать с константой? Нужно подать ее напрямую на вход модуля:

bbox bb_01(.in_data(8'd0240), .out_data(out_data));

Теперь на входе модуля мы имеем правильное значение:

Остается загадкой, почему при сокращении регистра, его значение в initial не подставляется на вход модуля.

Размерность wire лучше задавать самому.

При разработке в среде Quartus, допускается не задавать линии wire заранее. В этом случае они будут созданы автоматически, но об этом будет выдано предупреждение (warning). Проблема заключается в том, что разрядность wire будет 1-бит, а если порты будут иметь разрядность больше 1 бита, то значение не будет передано.

bbox bb_01(.in_data(8'd0240), .out_data(int_data)); other_bbox bb_02(.in_data(int_data), .out_data(out_data));

Предупреждение

Warning (10236): Verilog HDL Implicit Net warning at test.v(15): created implicit net for "int_data"

Результат:

Как видим, один бит подключен, а остальные 7 бит получаются не подключены (NC). Чтобы такой проблемы не было — нужно создать wire самостоятельно. Не зря компилятор IcarusVerilog выдает не warning, а ошибку, если wire не задан заранее.

wire [7:0] int_data; bbox bb_01(.in_data(8'd0240), .out_data(int_data)); other_bbox bb_02(.in_data(int_data), .out_data(out_data));

Компьютер не будет лазать по модулям, смотреть, какая разрядность портов. К тому же, разрядность может оказаться разной, а на вход модуля или с выхода берутся не все биты, а какие-то определенные.

Нельзя использовать выход логической функции, в качестве тактового сигнала

Иногда в проекте требуется снизить тактовую частоту, либо ввести временную задержку в N тактов. Новичёк может применить счетчик и дополнительную схему определения достижения счетчиком определенного значения (схема сравнения). Однако, если напрямую использовать выход со схемы сравнения в качестве тактового, то могут возникнуть проблемы. Это связано с тем, что логической схеме требуется некоторое время для установки стабильного значения на выходе. Эта задержка смещает фронт сигнала, проходящего через разные части логической схемы относительно тактового, в итоге получаются гонки, метастабильность, асинхронщина. Даже довелось однажды услышать реплику об этом в качестве критики ПЛИС: «с ПЛИС постоянные проблемы — гонки сигналов».

Если прочитать хотя бы парочку статей:

Метастабильность триггера и межтактовая синхронизация

Пару слов о конвейерах в FPGA

то становится ясно, каким образом разрабатываются устройства на ПЛИС: вся задача делится на аппаратные блоки, а данные между ними движутся по конвеерам, синхронно защелкиваясь в регистрах по тактовому сигналу. Таким образом, зная общую тактовую частоту, синтезатор рассчитывает максимальную частоту работы всех комбинаторных схем, определяет, укладывается ли их скорость к период такта и делает вывод — будет или не будет работать схема в ПЛИС. Все это происходит на этапе синтеза. Если схемы укладываются в параметры, то можно прошивать ПЛИС.

Для полного понимания, стоит прочитать Altera handbook на предмет «clock domains», а так же разобраться с тем, как задавать параметры рассчета TimeQuest для проекта.

Таким образом, для разработчиков устройств на базе ПЛИС созданы все необходимые методологии, и если их придерживаться, то проблем не будет.

А что, если я хочу пойти против системы?

Порядок разработки и поведение синтезатора схем подводит нас к выводу о том, что же такое ПЛИС на аппаратном уровне. Это синхронные схемы. Поэтому, среди целей синтезатора — уложиться во временные интервалы. Для этого он, к примеру, упрощает логические выражения, выбрасывает из синтеза части схем, которые не используются другими схемами и не привязаны к физическим выводам ПЛИС. Асинхронные решения и аналоговые трюки не приветствуются, потому что их работа может быть непредсказуемой и зависеть от чего угодно (напряжение, температура, техпроцесс, партия, поколение ПЛИС), а поэтому не дает гарантированного, повторяемого, переносимого результата. А всем же нужен стабильный результат и общие подходы к проектированию!

Но что же делать, если вы не согласны с мнением синтезатора о том, что нужно выкидывать неизменяемые регистры, сокращать логические схемы? Как быть, если хотите делать схемы с асинхронной логикой? Нужна тонкая настройка? А может быть вы сами хотите собрать схему на низкоуровневых компонентах ПЛИС? Легко! Спасибо разработчикам Altera за такую возможность и подробную документацию!

Как это сделать? Можно попробовать графический редактор схем. Вы, возможно, слышали о том, что Quartus позволяет рисовать схемы? Можно самому выбрать стандартные блоки и соединить их. Но это не решение! Даже нарисованная схема будет оптимизирована синтезатором, если на это будет возможность.

В итоге мы приходим к старой истине: если ничего не помогает — прочитайте инструкцию. А именно «Altera Handbook» часть под названием «Quartus II Synthesis Options».

Начнем с того, что описывая архитектуру на Verilog определенным образом, можно получить определенный результат. Вот примеры кода для получения синхронного и асинхронного RS триггера:

//модуль синхронного RS триггера module rs(clk, r, s, q); input wire clk, r,s; output reg q; always @(posedge clk) begin if (r) begin q <= 0; end else if (s) begin q <= 1; end end endmodule

В этом случае получится синхронный триггер.

Если не брать во внимание тактовый сигнал и переключаться в зависимости от любых изменений r и s, то в результате получится элемент с асинхронной установной значений — защелка (latch).

//пример модуль асинхронного RS триггера module ModuleTester(clk, r, s, q); input wire clk, r,s; output reg q; always @(r or s) begin if (r) begin q <= 0; end else if (s) begin q <= 1; end end endmodule

Но можно пойти еще дальше и самому создать защелку из примитива (примитивы доступны так же, как любой другой модуль Verilog):

module ModuleTester(clk, r, s, q); input wire clk, r,s; output reg q; DLATCH lt(.q(q), .clrn(~r), .prn(~s)); endmodule

В итоге, весь «обвес» на входе защелки, который синтезатор посчитал ненужным, исчезнет и мы получим именно то, что хотели:

Список существующих примитивов можно посмотреть на сайте Altera.

А теперь небольшой пример про асинхронность и сокращение. Задумал я, к примеру, сделать генератор по тому же принципу, как это было принято делать раньше, но только на ПЛИС:

Но для увеличения периода я возьму 4 элемента, но только один из них будет с инверсией:

module ModuleTester(q); output wire q; wire a,b,c,d; assign a = b; assign b = c; assign c = d; assign d = ~a; assign q = a; endmodule

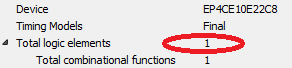

Но получается сокращение (1 элемент, вместо четырех). Что логично. Но мы то задумывали линию задержки.

Но если поставить синтезатору условие, что линии a,b,c,d не сокращать, то получится то, что мы задумали. Для подсказки синтезатору применяются директивы. Один из способов указания — это текст в комментарии:

module ModuleTester(q); output wire q; wire a,b,c,d /* synthesis keep */; // ^^^--- это директива для синтезатора assign a = b; assign b = c; assign c = d; assign d = ~a; assign q = a; endmodule

А вот и результат — цепочка из четырех элементов:

И это далеко не все! Оставлю на радость самостоятельного изучения: работу с case и директиву для реализации его в качестве RAM/ROM или логической схемой; работу со встроенными блоками памяти (RAM/ROM); выбор реализации умножения — аппаратным умножителем или логической схемой.

Выводы

Цитируя статью, хочу сказать, что «ПЛИС-ы / FPGA — не процессоры, «программируя» ПЛИС (заполняя конфигурационную память ПЛИС-а) вы создаете электронную схему (хардвер), в то время как при программировании процессора (фиксированного хардвера) вы подсовываете ему цепочку написанных в память последовательных инструкций программы (софтвер)».

Причем, как бы мне изначально не хотелось сильно не привязываться к конкретной железяке, но иногда, чтобы более эффективно и экономно использовать ресурсы, приходится работать на низком уровне. Часто этого можно избежать, если правильно разрабатывать синхронные схемы. Однако совсем забыть, что это железо — не получается.

Еще хочу сказать, что фанатизма и максимализма со временем поубавилось. Сначала я стремился все действия и рассчеты на ПЛИС выполнять за один такт, потому что ПЛИС это позволяет. Однако, это требуется далеко не всегда. Вычислительные ядра софт процессоров мне пока не довелось использовать, однако применение state machines для работы по определенному алгоритму — стало нормой. Вычисления не за 1 такт, временные задержки в несколько тактов из за применения конвееров — это норма.

Книги, которые мне очень помогли

1. В.В. Соловьев — Основы языка проектирования цифровой аппаратуры Verilog. 2014

2. Altera: Quartus II Handbook

3. Altera: Advanced Synthesis Cookbook

4. Altera: Designing with Low-Level Primitives

Статьи по тематике ПЛИС, Altera и Verilog

Новости ПЛИС индустрии

Microsoft переходит на процессоры собственной разработки

Intel собирается выпустить серверные процессоры Xeon со встроенной FPGA

Intel планирует выкупить Altera

РБК:Intel купила производителя чипов Altera за $16,7 млрд

Поиск Bing оптимизировали с помощью нейросети на FPGA

Поиск Bing оптимизировали с помощью нейросети на FPGA

Процессоры Intel Xeon оснастили FPGA Altera

Теория

Разработка цифровых устройств на базе СБИС программируемой логики

Аппаратные особенности

Метастабильность триггера и межтактовая синхронизация

Временной анализ FPGA или как я осваивала Timequest

Пару слов о конвейерах в FPGA

Verilog. Обертки RAM и зачем это нужно

Проектирование синхронных схем. Быстрый старт с Verilog HDL

Примеры

Делаем таймер или первый проект на ПЛИС

Часы на ПЛИС с применением Quartus II и немного Verilog

Как я делал USB устройство

Цветомузыка на базе ПЛИС

Программирование ПЛИС. Изучение явления «дребезг контактов» и метод избавления от него(VHDL!)

Реализация на Verilog цифрового БИХ-фильтра

Verilog. Цифровой фильтр на RAM

ПЛИС это просто или АЛУ своими руками

VGA адаптер на ПЛИС Altera Cyclone III

Исследование процессора и его функциональная симуляция

NES, реализация на FPGA

Генерация видео математической функцией на ПЛИС

Аппаратный сортировщик чисел на verilog-е

Простой SDR приёмник на ПЛИС

Автономный SDR приёмник на ПЛИС

Взгляд на 10G Ethernet со стороны FPGA разработчика

Простой радиопередатчик FM диапазона на основе ПЛИС

Делаем тетрис под FPGA

Minesweeper на FPGA

Делаем IBM PC на FPGA

PS

Спасибо всем, кто прочитал до этого места. Надеюсь, что что с этой статьей принцип работы и использования ПЛИС станет хотя бы немного ближе и понятнее. А в качестве примера применения в реальном проекте,