Comments 19

Харрис и Харрис читали, там куча всякого, что было бы вам интересно и помогло бы улучшить результат.

Почему MIPS-подобный RISC, а не собственная реализация RISC-V? Там было бы практически то же самое, точно без проблем с авторскими правами и потенциально с кучей поддержки, вплоть до работающего линукса.

В ПЛИС пробовали заливать? )

Почему MIPS-подобный RISC, а не собственная реализация RISC-V?

Ну это же, вероятно, курсовик или диплом, тут важен факт выполнения, а не содержание. :)

Здравствуйте,

Конвейер делали?

Пока нет.

Харрис и Харрис читали, там куча всякого, что было бы вам интересно и помогло бы улучшить результат.

Спасибо большое за наводку.

Почему MIPS-подобный RISC, а не собственная реализация RISC-V

Не сильно знаком с RISC-V. Изучения MIPS был частью университетского курса.

В ПЛИС пробовали заливать? )

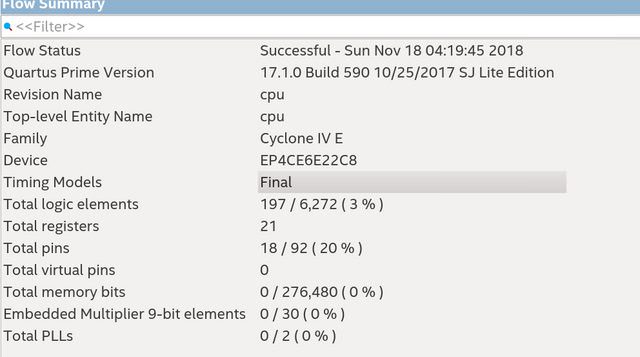

Пробовал заливать в Cyclone 4. Столкнулся с некоторыми проблемами.

По поводу конвейера, не могу не прорекламировать проект под названием SchoolMIPS (https://github.com/MIPSfpga/schoolMIPS). Кроме конвейера там имеется сопроцессор и шина AHB-lite в топовой ветке. Плюс он реализован по цифровой схемотехнике от Харрис и Харрис. И собственно из него черпаю вдохновение для своего ядра, правда на основе risc-v. И ещё по поводу ресурсов, попробуйте синтезировать только ALU, ресурсов потребуется сразу же больше.

Реализация на HDL

*Вы находитесь здесь*

Испытания на FPGA

Написание бэкенда к LLVM

Привлечение сообщества

Выпуск ASIC / продажи лицензии

…

PROFIT!

У меня лежит так и не доведенный до ума MISС с 16-бит словом. 4 бита на код инструкции это весело, да. Решение пришло

А вот мозгов и усидчивости выучить verilog и реализовать задуманное у меня как не было так и нет. Завидую тем, у кого голова работает и руки из нужного места растут.

Складывается впечатление что у каждого второго электронщика есть своя «великая и гениальная» архитектура процессора. Обычно она лежит в голове или в заметках где-нибудь внутри «Новая папка (3)» на файлопомойке.Как у каждого второго программиста есть великая и гениальная операционка.

Юношеский максимализм и желание сдвинуть горы для студента-старшекурсника — это не только нормально, но и правильно. Главное потом эту энергию использовать в мирных целях.

Здравствуйте, опередили однако) (сам недавно сел за описание небольшого ядра). Интересно сколько занимает Ваш проект на циклоне 4 или на любой другой ПЛИС, ибо увидел пару операций в АЛУ, которые "съедают" достаточно много ресурсов (/ и %)?

Рискну дать непрошенный совет автору:

— clock gating в стиле «assign g_clk = cond & clk»

— неблокирующие присваивания в комбинаторной логике

Обе конструкции нормально не работают нигде: ни в симуляции, ни в FPGA, ни в ASIC.

Зато они создают опасную иллюзию корректно работающей схемы и дарят часы отладки дельта-циклов. В качестве конструктива, в плане clock gating'a в ПЛИС проще (а для незамороченных проектов — лучше) использовать вход «En» в самом триггере. В таком духе: «if(condition) q <= d»

Здраствуйте, спасибо за советы.

Можете, пожалуйста, рассказать поподробнее, почему такие конструкции некорректно работают?

По clock gating'у:

В ПЛИС есть несколько выделенных линий тактовых сигналов (6, чтоли, в недорогих циклонах?) и управлять можно только всей линией целиком.

Возможно, в новых дорогих ПЛИСах с этим проще, но в любом случае на синтезатор полагаться не стоит — нужно напрямую указывать библиотечный компонент.

Ну, или делать enable во всех интересующих последовательностных блоках (а еще, можно вообще забить: ну не потребует собственный процессор принудительного охлаждения:)

В ASIC такой gating не работает потому что enable всегда задержан относительно тактового сигнала в зависимости от температуры и напряжения. Поэтому чтобы не было просечек, что-либо переключать лучше тогда, когда clk == 0. Сделать это можно, например, комбинацией гейта и защелки.

А в симуляторе причина та же, по которой не стоит использовать неблокирующие присваивания в комбинаторной логике.

Неблокируемость означает, что конкретно в этом цикле симуляции обновлять зависимые блоки не нужно, а новое значение еще не действует.

Ну то есть, последовательностная логика, работающая от тактового сигнала увидит изменения на следующем этого тактового сигнала. С комбинационной сложнее, и тут возможны варианты, в зависимости от того, что написано в других блоках. Если их нет, то все даже будет работать. А вот если есть, могут появиться спецэффекты: в waveform'ах вы увидите правильное поведение логики, но триггеры будут защелкивать неконсистентное состояние. С синтезом — как повезет. Скорее всего, проканает :) С gating'ом тактового сигнала та же история. Если все работает от gated clock — ну так и будет работать. А вот если в тестбенч clock обычный, а в дизайне — gated, то будут точно такие же спецэффекты, что и выше.

Написание простого процессора и окружения для него