Небольшое вступление:

Идея написания собственного ядра появилась после прохождения школы-семинара по цифровой схемотехнике в городе Томске. На данном мероприятии проводилось знакомство с текущими языками описания аппаратуры (Verilog HDL и VHDL), а также с небольшим процессорным ядром schoolMIPS. Для понимания устройства ядер было принято решение изобрести собственный велосипед, следуя по пути развития schoolMIPS, но взяв за основу другую систему команд. Вследствие роста популярности RISC-V и открытости его системы команд (MIPS на момент на��ала написания ядра не имел открытую систему команд) для осуществления разработки будущего ядра был выбран набор инструкций RISC-V, а именно RV32I. RV32I имеет небольшой набор базовых инструкций (37 без учёта специальных) и при желании его можно расширить, например, добавив инструкции целочисленного умножения и деления (RV32M) или поддержку сокращённых инструкций (compressed instructions) (RV32C). Также данный проект задумывался как образовательный, поэтому было решено по максимуму увеличить наглядность работы ядра для эффективной демонстрации его работы.

По аналогии с schoolMIPS были реализованы следующие версии ядра:

- Однотактная версия (00_simple_risc_v_cpu).

- Однотактная версия с поддержкой инструкций lw/sw (load word/store word) (01_simple_risc_v_cpu_lwsw).

- Конвейерная версия (5-ти стадийный конвейер) (02_pipe_risc_v_cpu).

На текущий момент описывается следующая версия ядра (03_pipe_risc_v_cpu_fc) с полным набором команд RV32I (без учёта некоторых специальных).

Краткая информация:

В ходе описания ядра продумывались пути повышения наглядности работы, отладки и верификации. На данный момент реализованы следующие методы:

Добавление отладочного текстового VGA модуля (для двух однотактных веток ядра). Включение данного модуля позволяет одновременно отслеживать значение 32 регистров на экране монитора, что не возможно при использовании вывода информации на семисегментные индикаторы. На рисунках представленных снизу ядро выполняет подсчёт чисел Леонардо и производится вывод информации на соответствующий отладочный модуль;

hex_display and DebugScreenCore

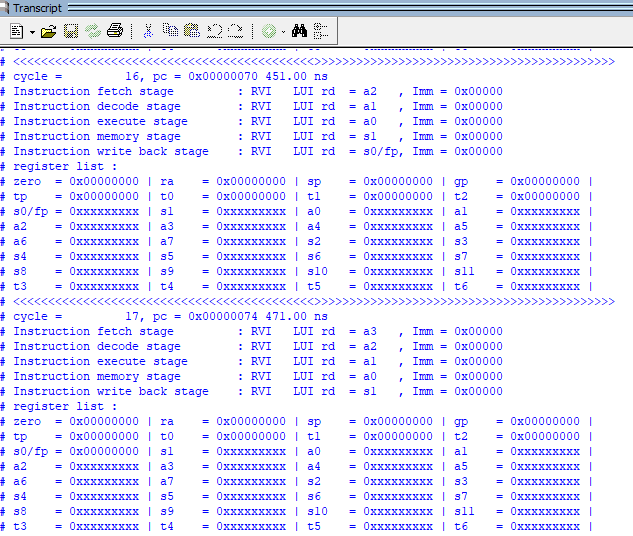

Добавление вывода сообщений в терминал симулятора о состоянии регистрового файла и исполняемых на текущий момент инструкциях. Данный метод позволяет лучше анализировать работу ядра на первых стадиях разработки, но не всегда является удобным;

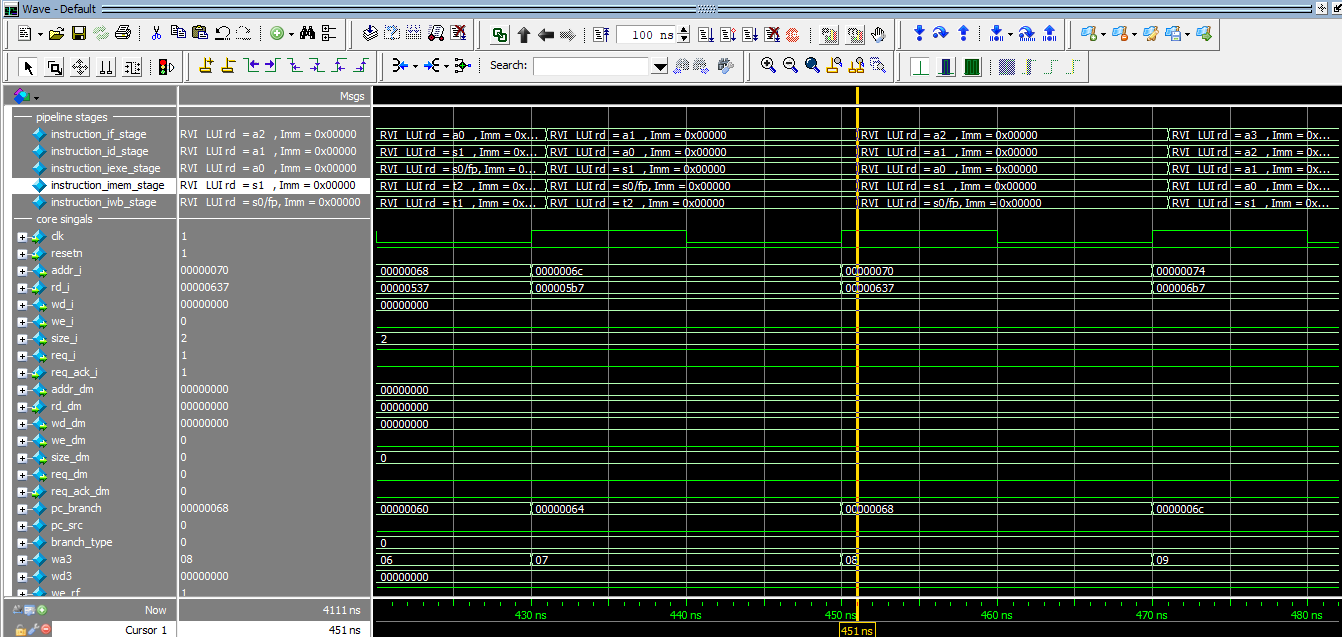

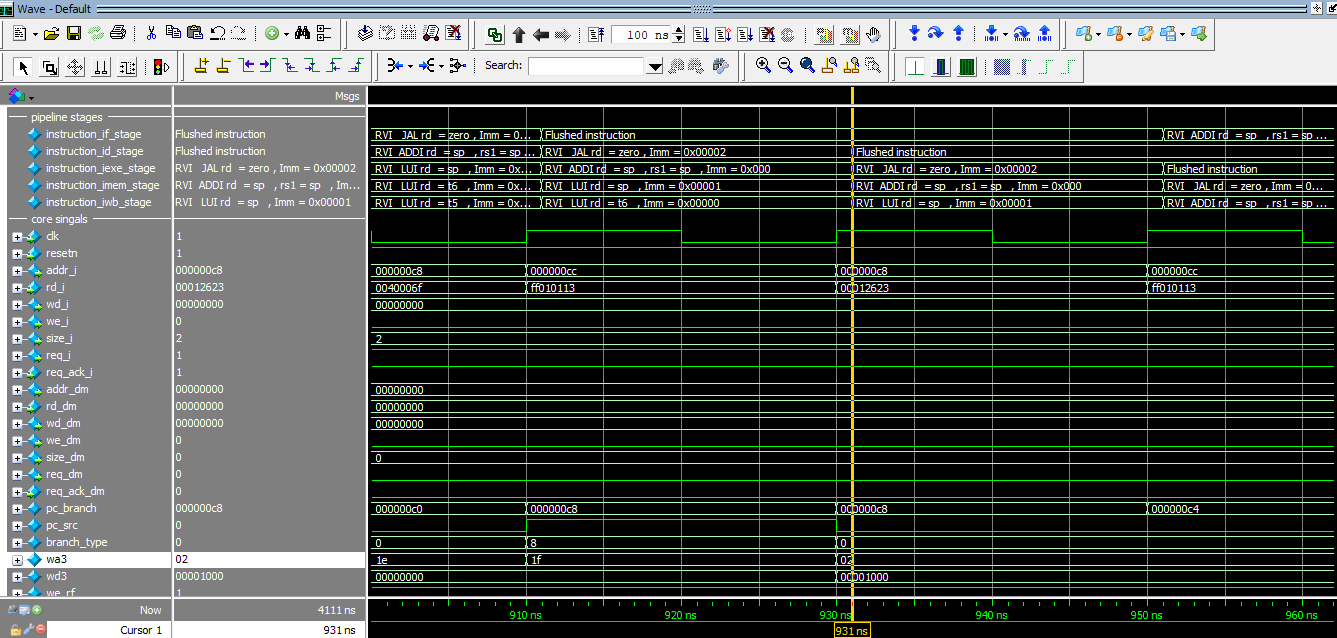

Добавление строковых переменных на waveform с отображением исполняемых инструкций. При помощи этих строковых переменных разработчик может отслеживать правильное выставление управляющих сигналов на всех стадиях конвейера;

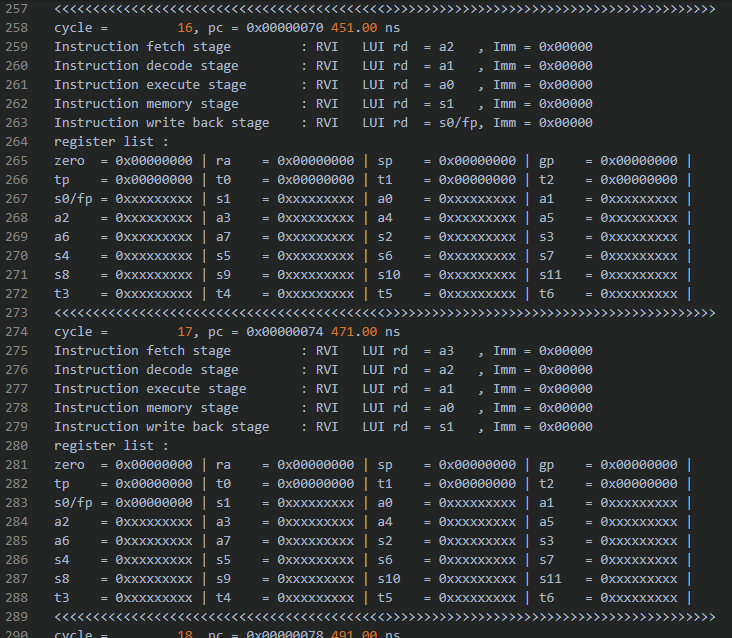

Добавление возможности записи отладочной информации о состоянии ядра в текстовый файл. Состояние регистрового файла представляется в табличном виде, а также обозначается инструкция/инструкции, выполняемые на текущий момент ядром. Является аналогом 2 пункта, но позволяет производить больше манипуляций с полученной информацией;

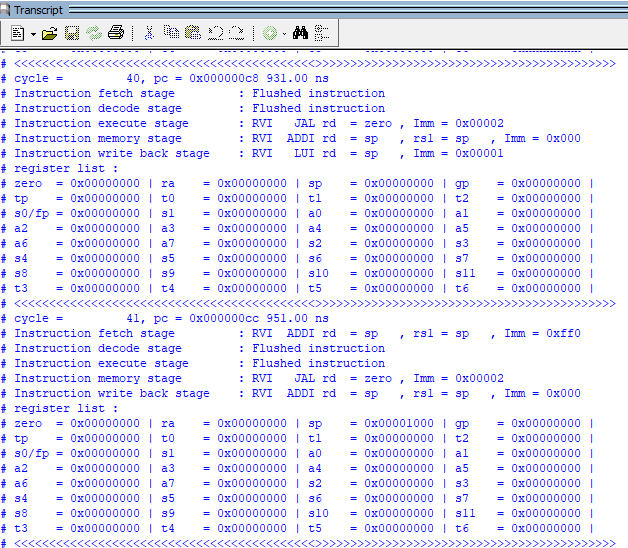

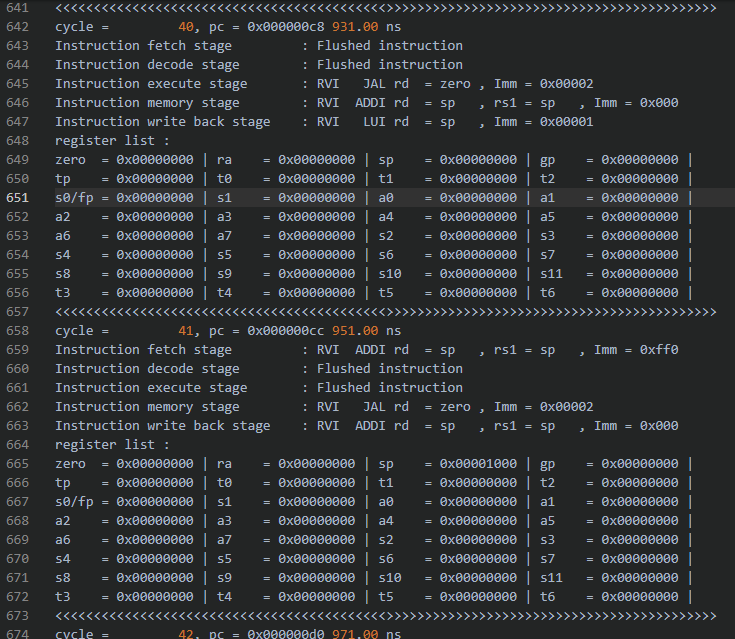

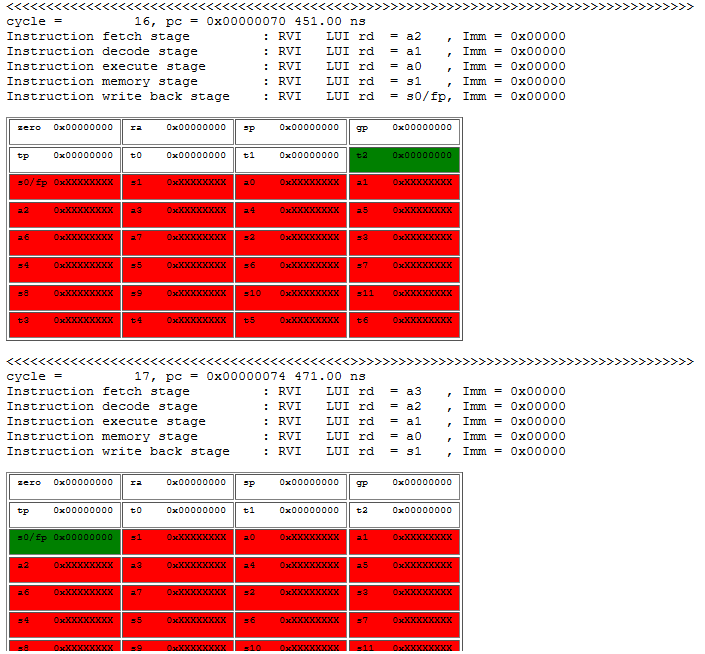

Добавление возможности записи отладочной информации о состоянии ядра в HTML файл. Состояние регистрового файла представляется в табличном виде с пометками об изменении значений ячеек, а также выводятся инструкции, выполняемые на текущий момент ядром. Является аналогом пунктов 2 и 4, но в дополнении к ним позволяет удобно указывать на изменение данных. Как можно видеть на картинках снизу в случае, если значение регистра было не определено, то подсветка регистров осуществляется красным цветом ( регистры s0/fp — t6 ). На 17 цикле значение регистра s0/fp изменяется и ячейка подсвечивается зелёным цветом.

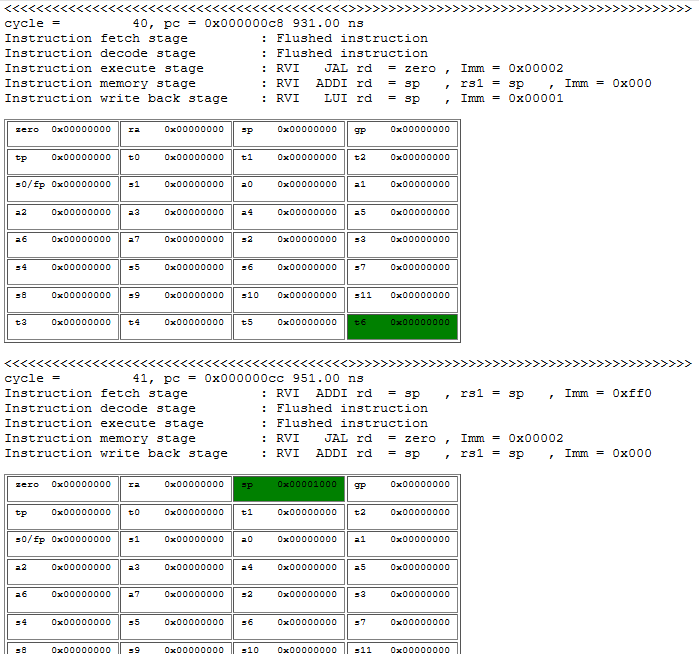

На 41 цикле в регистр sp загружается значение 0x00010000.

Поддерживаемые инструкции ядра на текущий момент для разных веток:

| Инструкция | 00_simple_risc_v_cpu | 01_simple_risc_v_cpu_lwsw | 02_pipe_risc_v_cpu |

|---|---|---|---|

| add | + | + | + |

| and | - | - | + |

| sll | - | - | + |

| or | + | + | + |

| addi | + | + | + |

| ori | - | - | + |

| slli | + | + | + |

| lw | - | + | + |

| jalr | - | - | + |

| lui | + | + | + |

| beq | + | + | + |

| bne | - | - | + |

| sw | - | + | + |

| jal | - | - | + |

| sub | + | + | - |

Поддерживаемая периферия:

| Периферия | 00_simple_risc_v_cpu | 01_simple_risc_v_cpu_lwsw | 02_pipe_risc_v_cpu |

|---|---|---|---|

| RAM | - | + | + |

| PWM | - | + | + |

| GPIO | - | + | + |

| UART | - | - | + |

Поддерживаемые языки для написания программ:

| Язык | 00_simple_risc_v_cpu | 01_simple_risc_v_cpu_lwsw | 02_pipe_risc_v_cpu |

|---|---|---|---|

| Assembler | + | + | + |

| C | - | - | + |

Необходимые ресурсы ПЛИС для ядра (nf_cpu):

EP4CE22F17C6 (de0_nano):

| 01_simple_risc_v_cpu_lwsw | 02_pipe_risc_v_cpu | 03_pipe_risc_v_cpu_fc | |

|---|---|---|---|

| Total memory bits | 0 / 608,256 ( 0 % ) | 2,048 / 608,256 ( < 1 % ) | 2,144 / 608,256 ( < 1 % ) |

| Total logic elements | 3,645 / 22,320 ( 16 % ) | 1,739 / 22,320 ( 8 % ) | 2,058 / 22,320 ( 9 % ) |

| Total combinational functions | 2,653 / 22,320 ( 12 % ) | 1,472 / 22,320 ( 7 % ) | 1,838 / 22,320 ( 8 % ) |

| Dedicated logic registers | 1,055 / 22,320 ( 5 % ) | 575 / 22,320 ( 3 % ) | 606 / 22,320 ( 3 % ) |

10M50DAF484C7G (de10_lite):

| 00_simple_risc_v_cpu | 01_simple_risc_v_cpu_lwsw | 02_pipe_risc_v_cpu | 03_pipe_risc_v_cpu_fc | |

|---|---|---|---|---|

| Total memory bits | 0 / 1,677,312 ( 0 % ) | 0 / 1,677,312 ( 0 % ) | 2,048 / 1,677,312 ( < 1 % ) | 2,144 / 1,677,312 ( < 1 % ) |

| Total logic elements | 2,851 / 49,760 ( 6 % ) | 2,881 / 49,760 ( 6 % ) | 1,629 / 49,760 ( 3 % ) | 1,927 / 49,760 ( 4 % ) |

| Total combinational functions | 2,613 / 49,760 ( 5 % ) | 2,653 / 49,760 ( 5 % ) | 1,473 / 49,760 ( 3 % ) | 1,849 / 49,760 ( 4 % ) |

| Dedicated logic registers | 1,055 / 49,760 ( 2 % ) | 1,055 / 49,760 ( 2 % ) | 575 / 49,760 ( 1 % ) | 606 / 49,760 ( 1 % ) |

Развитие проекта.

Что планируется сделать в будущем:

- добавить все инструкции RV32I (на стадии описания);

- реализовать отладку;

- добавить DMA (ПДП) контроллер;

- добавить поддержка других шин AXI, Avalon, Wishbone;

- добавить cache (КЭШ) память;

- интегрировать различную периферию (SPI, TWI (I2C), Ethernet(10 base-t));

- добавить контроллер прерываний;

- портировать разные версии на другие отладочные платы;

- добавить другие методы повышения наглядности работы ядра;

- запуск RTOS, например zephyr.

Также принимаются рекомендации и предложения по развитию ядра.

Ссылка на репозиторий: nanoFOX.