Junior FPGA Design Engineer: как стать?

11 min

Всем привет!

Иногда начинающие разработчики не очень хорошо представляют, какую литературу надо читать для серьезного изучения того или иного языка.

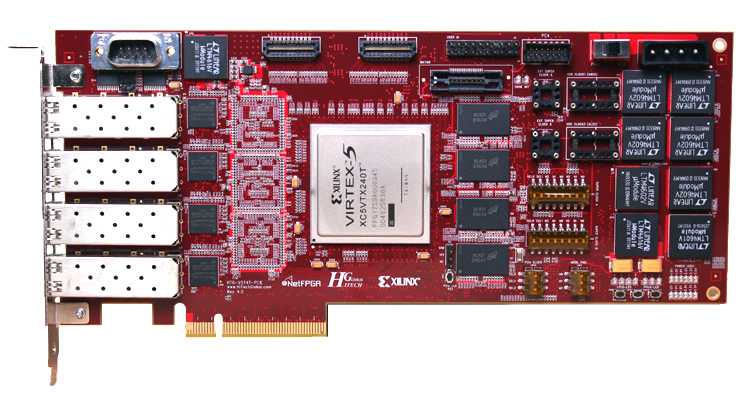

Разработка под FPGA (ПЛИС) — это не просто какой-то язык. Это очень объемная область, с огромным количеством подводных камней и нюансов.

В этой статье вы найдете:

Добро пожаловать под кат!

Иногда начинающие разработчики не очень хорошо представляют, какую литературу надо читать для серьезного изучения того или иного языка.

Разработка под FPGA (ПЛИС) — это не просто какой-то язык. Это очень объемная область, с огромным количеством подводных камней и нюансов.

В этой статье вы найдете:

- список тем, которые должен освоить начинающий разработчик под FPGA

- рекомендуемую литературу по каждой из тем

- набор тестовых вопросов и лабораторных работ

- классические ошибки новичков (и советы по исправлению)

Добро пожаловать под кат!

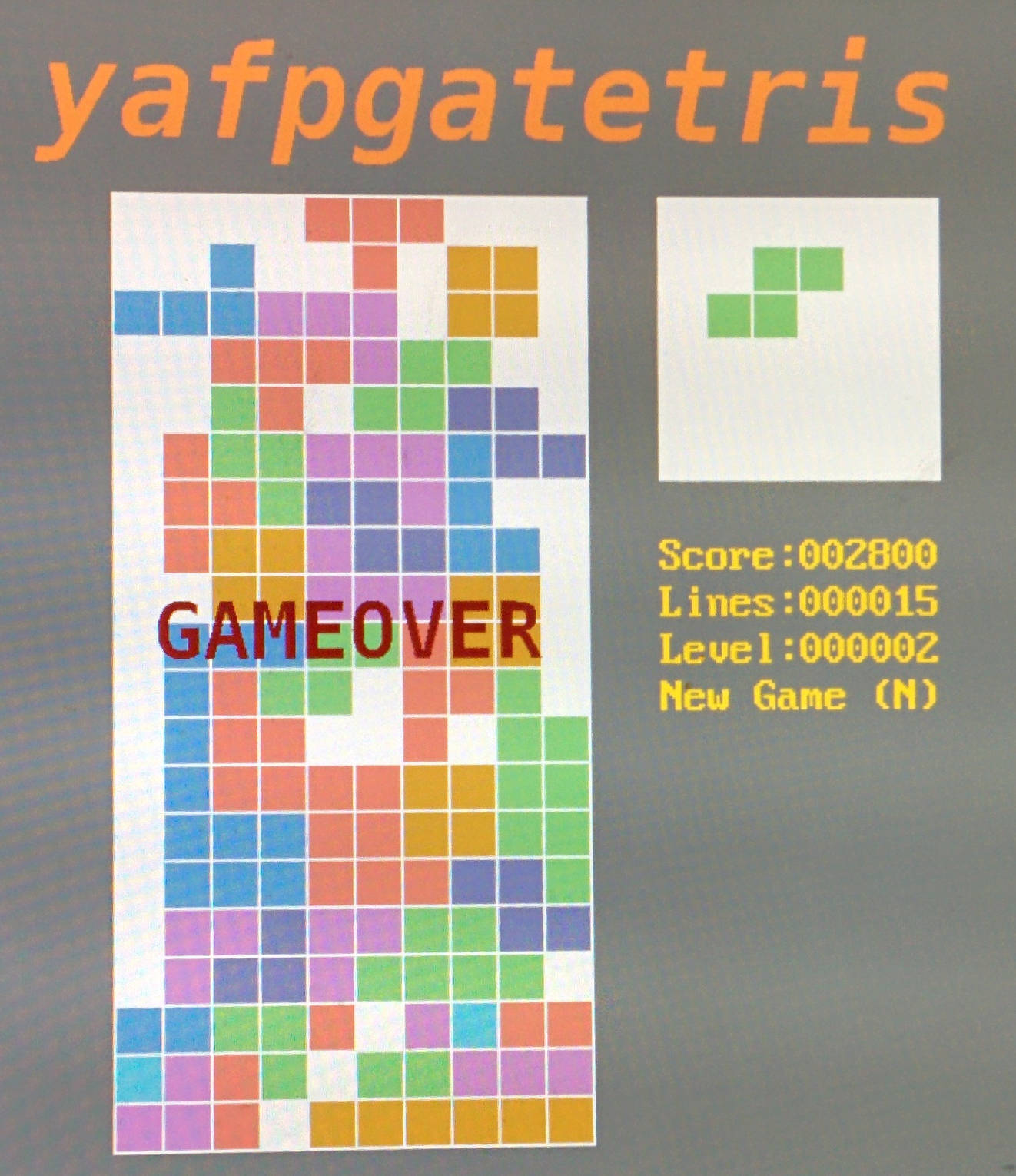

На этих долгих новогодних выходных я задался вопросом: насколько легко написать какую-то простенькую игрушку на FPGA с выводом на дисплей и управлением с клавиатуры. Так родилась еще одна реализация тетриса на

На этих долгих новогодних выходных я задался вопросом: насколько легко написать какую-то простенькую игрушку на FPGA с выводом на дисплей и управлением с клавиатуры. Так родилась еще одна реализация тетриса на