Симуляция высокоскоростных приёмопередатчиков с динамической реконфигурацией для ПЛИС Intel серии 10

В этой статье мы подошли к самому "свежему" поколению ПЛИС фирмы Intel, а именно 10 поколение. И теперь мы будем создавать проект в среде симуляции для Arria 10.

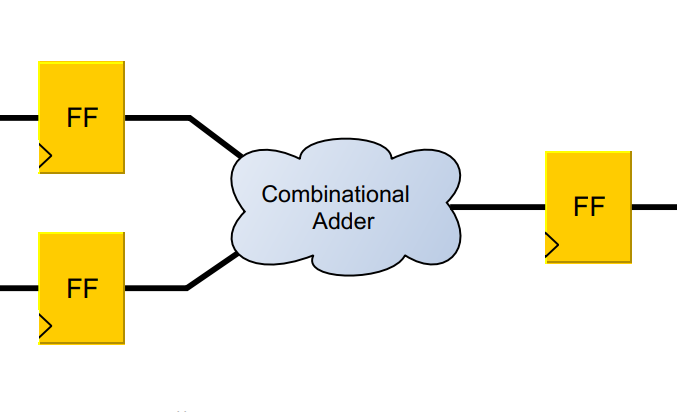

Напомню, что высокоскоростные приёмопередатчики - это пара RX и TX, встроенные в ПЛИС, которые позволяют преобразовать параллельную шину данных на низкой частоте в последовательную на высокой при передаче данных и из последовательной в параллельную при получении данных. Они необходимы для реализации различных протоколов передачи данных. А динамическая реконфигурация в данном случае необходима для "автосогласования" скорости работы интерфейсов, например 1 / 2,5 /10 Gb Ethernet.