Комментарии 51

Вот кстати давно хотел узнать: а почему нет единого документа, в котором было бы нарисовано когда вышла та или иная архитектура, какие новые фичи и наборы команд появились, как через CPUID эту архитектуру определить. В итоге о BMI2 я узнал совершенно случайно, а мог бы сразу видеть что где есть :-)

Вот кстати давно хотел узнать: а почему нет единого документа, в котором было бы нарисовано когда вышла та или иная архитектура, какие новые фичи и наборы команд появились

Пожалуй, самая полная историческая справка о датах выхода и доступности разных фич в процессорах доступна в Википедии, как это ни удивительно. Про единый документ — чуть ниже.

как через CPUID эту архитектуру определить

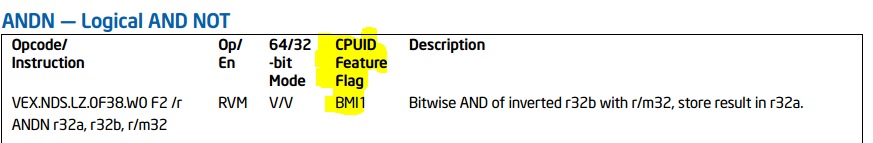

Какой бит используется в CPUID для индикации наличия определённой инструкции или класса инструкций всегда можно понять из описания инструкции в мануале Intel SDM. Например, для

ANDN из расширения BMI1:

Далее смотрим в том же мануале (может быть, в другом его томе), что ассоциируется с флагом BMI1 в CPUID.

В итоге о BMI2 я узнал совершенно случайно

Есть такой интересный документ: Intel® Architecture Instruction Set Extensions Programming Reference. В нём описываются инструкции, ещё не включенные в реальную продукцию, но планируемые быть доступными в не столь далёком будущем. Обновляется он достаточно часто (я один раз обнаружил, что имею у себя устаревшую локальную версию и из-за этого не в курсе, что вообще происходит). Его части со временем переезжают в Intel SDM, когда инструкции перестают быть «новыми». Очень полезный документ для писателей компиляторов, симуляторов и других программистов системного уровня.

Анонсы новых наборов случаются, кстати, и делаются на сайте Intel Developer Zone. Например, для Intel Haswell New Instructions, Intel RTM.

Есть замечательная структурированная сборка официальной документации по Intel + AMD:

www.sandpile.org/x86/ref_docs.htm

www.sandpile.org/x86/ref_docs.htm

В каком документе перечислены все имеющиеся архитектуры Intel? :-)

В каком документе перечислены все имеющиеся архитектуры Intel? :-)

Немножко придерусь к словам. Если Вам интересны именно «архитектуры», т.е. видимые системному программисту абстракции и связанные с ними наборы команд, то их не очень много, и ещё меньше из них ныне здравствуют. Поддерживаются, наверное, только Itanium и IA-32, но я не выяснял точно. Остальные уже упомянуты в этом треде: 4004, 8008, iAPX 432 и т.д. Забыли, правда, про StrongARM/XScale.

Если же подразумевались «микроархитектуры», т.е. внутренние реализации архитектур, то обычно эту их имена не используют для целей рекламы. По крайней мере с именами микроархитектур не ассоциируют предлагаемые функциональные особенности/преимущества. Для этих нужд используют маркетинговое имя, вроде Intel® Core (tm). Просто для того, чтобы оставить за собой пространство для манёвра, типа «вот описание архитектуры, а как она сделана внутри — это может поменяться без предварительного уведомления». Список микроархитектур для IA-32 ну очень длинный, я вынужден снова отослать интересующихся в Википедию.

Кстати, официальная база данных для сравнения выпущенных продуктов Intel называется ARK. С датами выхода, поддерживаемыми наборами команд, размерами и рекомендуемой ценой для партии. Есть даже Андроид приложение :-)

Intel IA-64. Является полным синонимом термина «Intel Itanium».Ещё Itanic :-)

…

Кстати, и для Itanium есть ещё одно обозначение — IPF.

А что значит буква А в префиксе IA-64? Архитектура?

Официально не расшифровывается, но подразумевается Architecture.

Вполне официально расшифровывается как Intel Architecture. Создавалась как замена x86, которую переименовали в IA-32, и которая исчерпала свой потенциал по тогдашним представлениям самой Intel. Но внедрить принципиально новую и полностью несовместимую со старой технологию у них не получилось — подсуетилась AMD со своим 64-битным расширением к x86, под которую адаптировать софт и ОСы оказалось намного проще. Поэтому пришлось отказаться от IA-64 и бросить все силы в погоню за AMD. Вернули название x86, добавили EM64T (называть архитектуру IA-32 64-bit как-то глупо :) а название IA-64 уже было занято, пришлось изголяться), вот так и получилась x86-64 и прочая чехарда с названиями.

Это маркетинговое название, которое не расшифровывается.

Ваша версия романтична, поэтична и очень красива, но не отражает действительность чуть более, чем полностью. Главная ошибка в ваших рассуждениях заключается в том, что вы предполагаете, что процессор от идеи до железа может быть реализован буквально за пол года в качесвте ответа на шаги конкурента. Это, к сожалению, не так. Примерно за два года до выхода железа публикуется его ISA — набор команд. На этот момент всё планирование, все эксперименты и багфикс в наборах инструкций уже завершён и осталось только отладить железячную часть. В этот момент можно напрячься и добавить кэшей, чуть увеличить тактовую частоту, но архитектура как таковая готова и команда работает уже давно над новыми чипами.

Итак, работа на Итаниумом началась ещё с лохматого 1989 года. Что, простите там было у AMD в тот момент? Чип делали долго и тщательно. Выверяли набор инструкций, проводили научные диспуты и старались сделать красивую архитектуру. В 2001 году сделали. Архитектура получилась красивая, стройная и лично мне она очень нравится. Но к сожалению, с некоторыми фундаментальными недостатками. Один из которых, заключается в том, что архитектура in-order и требует очень хорошей компиляторной поддержки для достижения хорошей или даже хотя бы приемлемой производительности. Ещё одним недостатком были проблемы с увеличением частоты из-за архитектурных особенностей, которые вовремя не смогли починить и частота долгое время была ахилесовой пятой этой архитектуры.

В это время х86 развивался и рос. Увеличивалось окно Out-Of-Order буфера, росло количество исполнительных устройств, взрослели векторные инструкции. Всё это сводило на нет преимущества широкого слова (Itanium2 способен за такт исполнять до 6 инструкций, правда если ограничения на инструкции одного типа).

В то время внедрение 64 битов в x86 не было насущной проблемой, они там были конечно нужны, но не то чтобы уж сильно. Непосредственно 64 бита несут скорее накладные расходы, чем преимущества — поинтеры-то длиннее, хранить их и гонять по памяти надо больше ресурсов. Вся прелесть 64 битов была в новых регистрах, которых стало больше и в новых инструкциях работы с ними — за счёт них и был прирост производительности. Но выпуск такого чита не был насущной необходимостью, у архитектуры были другие резервы увеличения производительности.

Естественно, в Интеле над 64 битами работали, но АМД обогнал на повороте и первым опубликовал свою спецификацию и первым выпустил чип. Это был умный и хитрый шаг. Но чип от Интел появился не сильно позже, что подтверждает, что он был и так практически готов. Но вот пришлось срочно переделывать имеющееся на ту спецификацию, которую выпустил АМД, ибо создавать ад для софтверной экосистемы в виде двух версий 64 битных чипов никто не хотел.

Заметьте, с Итаниумом это вообще никак не связано, он продолжал жить своей жизнью. Только вот с именованием получилась путаница и 64 битную версию x86 пришлось назвать Intel64, а IA-64 оставить за Итаниумом.

Ваша версия романтична, поэтична и очень красива, но не отражает действительность чуть более, чем полностью. Главная ошибка в ваших рассуждениях заключается в том, что вы предполагаете, что процессор от идеи до железа может быть реализован буквально за пол года в качесвте ответа на шаги конкурента. Это, к сожалению, не так. Примерно за два года до выхода железа публикуется его ISA — набор команд. На этот момент всё планирование, все эксперименты и багфикс в наборах инструкций уже завершён и осталось только отладить железячную часть. В этот момент можно напрячься и добавить кэшей, чуть увеличить тактовую частоту, но архитектура как таковая готова и команда работает уже давно над новыми чипами.

Итак, работа на Итаниумом началась ещё с лохматого 1989 года. Что, простите там было у AMD в тот момент? Чип делали долго и тщательно. Выверяли набор инструкций, проводили научные диспуты и старались сделать красивую архитектуру. В 2001 году сделали. Архитектура получилась красивая, стройная и лично мне она очень нравится. Но к сожалению, с некоторыми фундаментальными недостатками. Один из которых, заключается в том, что архитектура in-order и требует очень хорошей компиляторной поддержки для достижения хорошей или даже хотя бы приемлемой производительности. Ещё одним недостатком были проблемы с увеличением частоты из-за архитектурных особенностей, которые вовремя не смогли починить и частота долгое время была ахилесовой пятой этой архитектуры.

В это время х86 развивался и рос. Увеличивалось окно Out-Of-Order буфера, росло количество исполнительных устройств, взрослели векторные инструкции. Всё это сводило на нет преимущества широкого слова (Itanium2 способен за такт исполнять до 6 инструкций, правда если ограничения на инструкции одного типа).

В то время внедрение 64 битов в x86 не было насущной проблемой, они там были конечно нужны, но не то чтобы уж сильно. Непосредственно 64 бита несут скорее накладные расходы, чем преимущества — поинтеры-то длиннее, хранить их и гонять по памяти надо больше ресурсов. Вся прелесть 64 битов была в новых регистрах, которых стало больше и в новых инструкциях работы с ними — за счёт них и был прирост производительности. Но выпуск такого чита не был насущной необходимостью, у архитектуры были другие резервы увеличения производительности.

Естественно, в Интеле над 64 битами работали, но АМД обогнал на повороте и первым опубликовал свою спецификацию и первым выпустил чип. Это был умный и хитрый шаг. Но чип от Интел появился не сильно позже, что подтверждает, что он был и так практически готов. Но вот пришлось срочно переделывать имеющееся на ту спецификацию, которую выпустил АМД, ибо создавать ад для софтверной экосистемы в виде двух версий 64 битных чипов никто не хотел.

Заметьте, с Итаниумом это вообще никак не связано, он продолжал жить своей жизнью. Только вот с именованием получилась путаница и 64 битную версию x86 пришлось назвать Intel64, а IA-64 оставить за Итаниумом.

Я не очень понял ваше замечание про in-order. В IA-64 модель памяти слабее чем в x86/x64, есть value speculation, что дает больше возможностей по выполнению инструкций Out-Of-Order.

Множите пояснить свою точку зрения?

Множите пояснить свою точку зрения?

Архитектуры бывают in-order, когда на первой же команде, у которой нет данных мы стоим и ждём пока всё будет для неё готово и только после этого выполняем её и продолжаем выполнение последующих команд, и out-of-order, когда процессор идёт дальше и смотрит чтобы ещё можно выполнить из потока команд, пока данные для проблемой инструкции будут готовы.

При этом всё происходит в динамике, всё делает железо.

Итаниум — in-order. Но для того чтобы как-то решить соответствующие проблемы с производительностью, вызванные этим прискорбным фактом, в наборе команд есть много разных очень занимательных уловок, в том числе механизмы спекуляции. Но обо всё этом должен заботиться компилятор. А это значит две вещи 1) компилятор должен проделать очень сложную работу, по выявлению того, что требует спекуляции. 2) компилятору доступна только статическая информация — что происходит в динамике он предсказать не может во многих случаях даже теоретически.

При этом всё происходит в динамике, всё делает железо.

Итаниум — in-order. Но для того чтобы как-то решить соответствующие проблемы с производительностью, вызванные этим прискорбным фактом, в наборе команд есть много разных очень занимательных уловок, в том числе механизмы спекуляции. Но обо всё этом должен заботиться компилятор. А это значит две вещи 1) компилятор должен проделать очень сложную работу, по выявлению того, что требует спекуляции. 2) компилятору доступна только статическая информация — что происходит в динамике он предсказать не может во многих случаях даже теоретически.

С другой стороны, компилятор должен проделать очень сложную работу один раз (и не важно, сколько времени эта работа займёт), а OoO-процессор такую работу вынужден проделывать каждый раз (и притом умопомрачительно быстро).

Так что вполне ещё может стать, что на очередном витке технологического прогресса хитрозадость компиляторов обгонит хитрозадость процессоров, и использование VLIW станет оправданным.

Так что вполне ещё может стать, что на очередном витке технологического прогресса хитрозадость компиляторов обгонит хитрозадость процессоров, и использование VLIW станет оправданным.

VLIW совсем не означает in-order. Это разные вещи.

У компилятора не достаточно информации в принципе, нужна динамическая информация — грубо говоря на одних данных всё может быть хорошо, а на других всё плохо.

К тому же вся машинерия ОоО практически не тормозит выполнение команд, она включается когда данные не готовы. Но она усложняет ядро, это факт. Возможно без неё получилось бы чуть-чуть разогнать основной путь исполнения, но не сильно. А вот энергию она жрёт, это да. Поэтому в мобильных решениях до недавнего времени OoO можно было встретить очень редко.

У компилятора не достаточно информации в принципе, нужна динамическая информация — грубо говоря на одних данных всё может быть хорошо, а на других всё плохо.

К тому же вся машинерия ОоО практически не тормозит выполнение команд, она включается когда данные не готовы. Но она усложняет ядро, это факт. Возможно без неё получилось бы чуть-чуть разогнать основной путь исполнения, но не сильно. А вот энергию она жрёт, это да. Поэтому в мобильных решениях до недавнего времени OoO можно было встретить очень редко.

> С другой стороны, компилятор должен проделать очень сложную работу один раз (и не важно, сколько времени эта работа займёт)

Не в тему, но проблема долгой компиляции была из главных причин появления языка Go.

Не в тему, но проблема долгой компиляции была из главных причин появления языка Go.

А AMD x64 out-of-order?

Вопрос не совсем корректный, то короткий ответ — да.

Я был немного неточен в формулировках. Я сказал, что архитектуры бывают in-order и out-of-order. На самом деле не архитектуры, а реализации архитектур. Но с Итаниумом всё просто — равлизации out-of-order нет и не предвидится. Но там OoO так просто не прикрутишь, он изначально не предполагался.

Все же современные x86 чипы десктопного и производительного мобильного класса (включая 64 битные вариации) out-of-order. Почему я сделал оговорку про класс процессора — потому что Atom in-order. Но со следующего поколения будут OoO. Амдшные же мобильные процессоры вроде все OoO — по крайней мере Bobcat и Jaguar.

Я был немного неточен в формулировках. Я сказал, что архитектуры бывают in-order и out-of-order. На самом деле не архитектуры, а реализации архитектур. Но с Итаниумом всё просто — равлизации out-of-order нет и не предвидится. Но там OoO так просто не прикрутишь, он изначально не предполагался.

Все же современные x86 чипы десктопного и производительного мобильного класса (включая 64 битные вариации) out-of-order. Почему я сделал оговорку про класс процессора — потому что Atom in-order. Но со следующего поколения будут OoO. Амдшные же мобильные процессоры вроде все OoO — по крайней мере Bobcat и Jaguar.

Няп, замечание про in-order касалось выполнения команд, а не модели памяти.

С жесткой моделью памяти вы не построите out-of-order выполнение команд.

Почему, собственно?

Представьте что у вас самая жесткая модель памяти — любые перестановки запрещены. Как вы сделаете любую оптимизацию out-of-order если порядок чтений и записей жестко задан?

Вот вам первая же ссылка из гугла:

It’s true that a x86/64 processor can execute instructions out-of-order, but that’s a hardware implementation detail – what matters is that it still keeps its memory interactions in-order, so in a multicore environment, we can still consider it strongly-ordered.

Разговоры про «жёсткость» модели памяти — это очень тонкий вопрос и, честно говоря, не связанный с OoO напрямую. Если под «жёсткостью» IA-32 подразумевается т.н. sequential consistency, то это не так. Официальная спецификация (Intel IA-32 SDM, том 3А, секция 8.2.2) описывает ситуации, когда чтения и записи могут быть переупорядочены. Вот, приведу полный список.

Для однопроцессорных систем:

• Reads are not reordered with other reads.

• Writes are not reordered with older reads.

• Writes to memory are not reordered with other writes, with the following exceptions:

— writes executed with the CLFLUSH instruction;

— streaming stores (writes) executed with the non-temporal move instructions (MOVNTI, MOVNTQ,

MOVNTDQ, MOVNTPS, and MOVNTPD); and

— string operations (see Section 8.2.4.1).

• Reads may be reordered with older writes to different locations but not with older writes to the same location.

• Reads or writes cannot be reordered with I/O instructions, locked instructions, orserializing instructions.

• Reads cannot pass earlier LFENCE and MFENCE instructions.

• Writes cannot pass earlier LFENCE, SFENCE, and MFENCE instructions.

• LFENCE instructions cannot pass earlier reads.

• SFENCE instructions cannot pass earlier writes.

• MFENCE instructions cannot pass earlier reads or writes.

Для многопроцессорных систем:

• Individual processors use the same ordering principles as in a single-processor system.

• Writes by a single processor are observed in the same order by all processors.

• Writes from an individual processor are NOT ordered with respect to the writes from other processors.

• Memory ordering obeys causality (memory ordering respects transitive visibility).

• Any two stores are seen in a consistent order by processors other than those performing the stores

• Locked instructions have a total order.

Для того, чтобы при необходимости запретить переупорядочивание доступов в память, были введены инструкции LFENCE, SFENCE и MFENCE.

Для однопроцессорных систем:

• Reads are not reordered with other reads.

• Writes are not reordered with older reads.

• Writes to memory are not reordered with other writes, with the following exceptions:

— writes executed with the CLFLUSH instruction;

— streaming stores (writes) executed with the non-temporal move instructions (MOVNTI, MOVNTQ,

MOVNTDQ, MOVNTPS, and MOVNTPD); and

— string operations (see Section 8.2.4.1).

• Reads may be reordered with older writes to different locations but not with older writes to the same location.

• Reads or writes cannot be reordered with I/O instructions, locked instructions, orserializing instructions.

• Reads cannot pass earlier LFENCE and MFENCE instructions.

• Writes cannot pass earlier LFENCE, SFENCE, and MFENCE instructions.

• LFENCE instructions cannot pass earlier reads.

• SFENCE instructions cannot pass earlier writes.

• MFENCE instructions cannot pass earlier reads or writes.

Для многопроцессорных систем:

• Individual processors use the same ordering principles as in a single-processor system.

• Writes by a single processor are observed in the same order by all processors.

• Writes from an individual processor are NOT ordered with respect to the writes from other processors.

• Memory ordering obeys causality (memory ordering respects transitive visibility).

• Any two stores are seen in a consistent order by processors other than those performing the stores

• Locked instructions have a total order.

Для того, чтобы при необходимости запретить переупорядочивание доступов в память, были введены инструкции LFENCE, SFENCE и MFENCE.

Естественно, в Интеле над 64 битами работали, но АМД обогнал на повороте и первым опубликовал свою спецификацию и первым выпустил чип.

Из ваших слов вытекает, что 2 компании которые параллельно разрабатывали свои архитектуры получили почти одинаковые результаты, и что Intel надо было просто чуть чуть переделать спецификацию(что как я понимаю просто бумажка с названими регистров и команд итп.)

Верится с трудом. Все таки на мой взгляд Интел разрабатывала свои чипы по АМДшной спецификации. Просто я так думаю они ее получили, не в тот момент когда она официально ушла в паблик, а раньше)

Переделать в авральном режиме ISA можно, а вот архитектуру быстро не сделаешь.

Я не знаю как всё было и не обладаю инсайдерской информацией (это дисклеймер), но что-то мне подсказывает, что если бы Интел узнал о планах АМД выпустить 64 битную ISA, то за неделю бы сваял свою спеку и опубликовал бы первым.

Я не знаю как всё было и не обладаю инсайдерской информацией (это дисклеймер), но что-то мне подсказывает, что если бы Интел узнал о планах АМД выпустить 64 битную ISA, то за неделю бы сваял свою спеку и опубликовал бы первым.

> Используется для обозначения 64-битной архитектуры, несовместимой ни с IA-32, ни с 64-битным её вариантом ни по набору команд, ни по принципам работы.

«Её» — кого? IA-32 или IA-64?

«Её» — кого? IA-32 или IA-64?

За ним были 8088, 80186, 80286, 80386 (плюс вариации), 80486 (плюс вариации). Легко заметить, что (почти) все эти числовые имена оканчиваются на две цифры 86, что дало название всей серии x86.

Странная выборка какая-то, как минимум 80188 не представлен.

Ну и понимания «откуда взялись цифры 86» такая выборка всё равно не добавляет.

80186/80188 по-моему не сыграли значимой роли в индустрии. стоит ли про них вспоминать?

Интереующиеся могут открыть вики

ru.wikipedia.org/wiki/80186

ru.wikipedia.org/wiki/80188

Понимания почему именно 86 может добавить тот факт, что непосредственно до процессора 8086 был (что удивительно!) процесор 8085, а еще ранее 8080 (о 8081/8082/8083/8084 упоминаний не нашлось). Скорее всего это практичестки ничего не значащее название-индекс, которое уже потом стало брендом.

Почему Боинг-727 / -737 / -747? (везде кончается на 7)

Почему ИЛ-76 / -86 / -96? (везде кончается на 6)

Почему Ту-104 / -134 / -144 / -154 / -204? (везде кончается на 4)

Интереующиеся могут открыть вики

ru.wikipedia.org/wiki/80186

ru.wikipedia.org/wiki/80188

Понимания почему именно 86 может добавить тот факт, что непосредственно до процессора 8086 был (что удивительно!) процесор 8085, а еще ранее 8080 (о 8081/8082/8083/8084 упоминаний не нашлось). Скорее всего это практичестки ничего не значащее название-индекс, которое уже потом стало брендом.

Почему Боинг-727 / -737 / -747? (везде кончается на 7)

Почему ИЛ-76 / -86 / -96? (везде кончается на 6)

Почему Ту-104 / -134 / -144 / -154 / -204? (везде кончается на 4)

8086 создавался как временный 16-битный «костыль» для 8-битной архитектуры 8080 (ее усовершенствованной версии в виде процессора 8085), пока разрабатывалась опять же «принципиально новая» :) 32-битная архитектура iAPX 432, целью которой было заменить 8080. С iAPX 432 у Intel тоже не сложилось, а архитектура x86 продолжила развиваться.

Да, лучше было бы упомянуть AMD Am5x86, Cyrix Cx5x86, IBM 5x86 и похоже именованные модели постарше и помладше от этих и других производителей.

Они были реально очень распространены (первые два — даже в отечественной рознице, с ценой заметно ниже интеловских).

Они были реально очень распространены (первые два — даже в отечественной рознице, с ценой заметно ниже интеловских).

Я так понимаю, АМД успела первой с 64-разрядной архитектурой и ее названием, тем самым забив жирный гвоздь в задницу интелу. Вроде уже и прижился и не болит, а все равно иногда ноет… Отсюда и множество других названий.

Заслуга AMD в том, что они внедрили 64-битное расширение в архитектуру х86, чего Intel делать не собиралась (делая ставку на IA-64). Intel собиралась отказаться от более чем 20-летного (на тот момент) наследия архитектуры x86 и внедрить принципиально новую IA-64, однако для рынка более дешевое решение от AMD оказалось намного более привлекательным. Теперь, благодаря AMD, мы имеем обросшую миллионом костылей архитектуру, недавно отметившую свое 35-летие :)

Тем временем, я недавно осознал, что Core 2 Quad и core i7 это, несмотря на разницу во времени года так в 4, практически идентичные процессоры. И зачем платить больше, спрашивается? Ах да, поддержка аппаратной виртуализации. Специально чтобы приложения для Windows Phone разрабатывать.

Как минимум, в i7 есть HyperThreading, а в Core2Quad нету, если мне не изменяет память :)

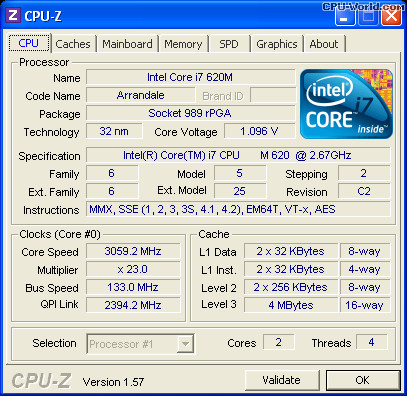

У меня в i7 нету HyperThreading :(

Это в каком это Core i7 отсутствует поддержка HT? =)

M 620

Intel Core i7-620M

ark.intel.com/products/43560

www.cpu-world.com/CPUs/Core_i7/Intel-Core%20i7%20Mobile%20I7-620M%20CP80617003981AH.html

Intel Hyper-Threading Technology — Yes

ark.intel.com/products/43560

www.cpu-world.com/CPUs/Core_i7/Intel-Core%20i7%20Mobile%20I7-620M%20CP80617003981AH.html

Intel Hyper-Threading Technology — Yes

Совершенно никакой разницы, вы правы. Только производительность в 3 раза выше. И это при том что TDP топовых 2квад было 130, а у нынешних i7 — 84. А нижний вариант так и вовсе 35 при потери всего где то 30% производительности.

В 3 раза, откуда информация? Вот сравнение на Anandtech, в большинстве случаев разница минимальна. На практике я ранизицы по производительности не ощущаю вообще.

Почему вы сравниваете с i7 пятилетней давности? Новый i7 4770K выигрывает у Quad в 1.5 — 3 раза.

«Intel Core i7» — это торговая марка, которая используется Intel уже для ряда продуктов, основанных на различных микроархитектурах и техпроцессах: Nehalem, Westmere, Sandy Bridge, Ivy Bridge, Haswell (вроде ничего не забыл).

Смешивать Core i7 разных поколений — это примерно то же самое, что считать, что Pentium и Pentium IV — это примерно одно и то же. Или считать что Intel Xeon (тоже торговая марка) времён Pentium II — это почти равно Intel Xeon выпуска 2012 года.

Смешивать Core i7 разных поколений — это примерно то же самое, что считать, что Pentium и Pentium IV — это примерно одно и то же. Или считать что Intel Xeon (тоже торговая марка) времён Pentium II — это почти равно Intel Xeon выпуска 2012 года.

Современный процессор может в обычном режиме работать в пределах 1-2 Вт. Графика — до 0.5 Вт. Не было такого в прекрасных Core 2 Quad.

Простите за подъем, а что за обозначение у дистрибутива линукс i586?

SERVER-X86_64.ISO SERVER-I586.ISO

SERVER-X86_64.ISO SERVER-I586.ISO

Зарегистрируйтесь на Хабре, чтобы оставить комментарий

Десять имён для одной архитектуры