Каждый год мы видим очереди фанатов, которым не терпится первыми прикоснуться к только что выпущенному новому айфону. А хотите узнать, как выглядит смартфон за два года до начала его продаж в магазине? Он в это время уже существует, как набор файлов в компьютерах проектировщиков его системы на кристалле.

Что же видит проектировщик Apple на своем экране? Завесу над этой тайной поможет над приоткрыть знаменитый в узких кругах блоггер Джон Кули (John Cooley), который начал свой вебсайт deepchip.com еще в 1990-е годы. Джон собирает всякие слухи, сливы и мнения тысяч инженеров больших электронных компаний, стартапов и контракторов, которые потом все это с большим интересом читают.

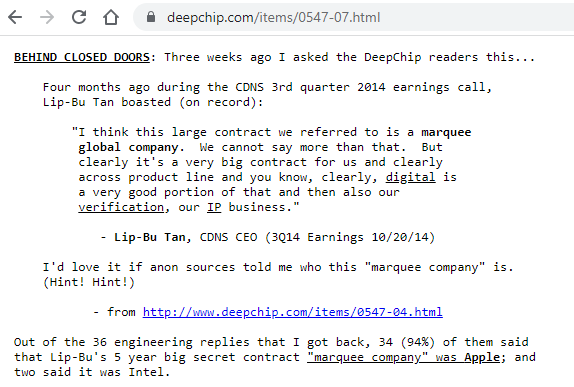

Когда-то в 2015 году, Джон опубликовал заметку "За закрытыми дверями", на основе анонимных емейлов от 36 инженеров. Аккурат в это время Apple переходил на собственные версии CPU и GPU (до этого Apple использовал готовые ядра от ARM и Imagination Technologies). Заметка выглядела так:

Согласно выводам Джона, Apple в указанный момент перешел от использования проектировочного софта от компании Synopsys к проектировочному софту от компании Cadence, по крайней мере в некоторых проектах.

Такой софт нельзя просто скачать. Это вам не ардуина. Он стоит реально бешенные деньги. Если вы считаете бешенными деньгами скромные $5000 за платную версию Intel FPGA Quartus, то для ASIC design приготовьтесь к следущему уровню бешенности. Еще в 1990-е лицензия на Synopsys Design Compiler стоила в районе 80 тысяч долларов. Потом где-то была цифра что одно инженерное место с Synopsys IC Compiler стоило в ~2010 году $300K, а вот можно нагуглить, что годовая подписка на ICC в 2015 году стоила $735 тысяч долларов. Обычно крупные электронные компании покупают сразу сотни плавающих лицензий и заключают с Cadence и Synopsys сделки на десятки миллионов долларов.

Что же делать, если у вас в кармане нет таких сумм? Хочется, условно говоря, сделать кружок по стадиону на Макларене или Ламборгини, не покупая его? В эту субботу 5 февраля такая возможность у вас будет. Сколковская Школа Синтеза Цифровых Схем договорилась с Московским Институтом Электронной Техники, который договорился с Cadence Design Systems, что мы дадим желающим порулить.

Пока на действо записалось 38 человек (21 которые ходят на школу офлайн и 17 которые участвуют онлайн), а Cadence выделяет нам на один день 20 лицензий. Главное занятие будет с 12.00 до 15.00, но помимо него будет наверное еще две-три смены. Кроме этого, пока одни пользуются скажем синтезом (Genus), другие могут скажем использовать размещение и трассировку (Innovus) а третьи посмотреть как работает симулятор SimVision, которые предпочитают многие про.

Занятие проведёт Александр Швец, доцент кафедры ИЭМС МИЭТ. Записаться можно сегодня (в четверг) до вечера. Зарегистрируйтесь на сайте школы и пошлите емейл Александру Биленко на info@chipexpo.com . Для доступа вам нужно получить от МИЭТ специальный VPN, а также использовать программу VNC для доступа к удаленным линуксным серверам, на которых будут работать все программы. Вообще этот софтвер регулируется не только обычными законами о копирайте, но и экспортным контролем, поэтому даже не думайте использовать его скажем на Кубе или в Северной Корее - экспорт туда такого софта строго запрещен.

Что же будет на занятии? Сначала мы возмем код простейшего процессора schoolRISCV на языке описания аппаратуры Verilog. Этот предельно минималистический процессор для обучения написал Станислав Жельнио, разработчик и взрослых процессоров в российcкой компании Syntacore.

Код schoolRISCV - это всего 300 строк, их может прочитать и понять даже школьник, который знает основы верилога и обладает олимпиадным типом мышления. При этом мы будем делать с ним те же самые операции, что и проектировщик реального смартфона, хотя процессорр в реальном смартфоне в ~тысячу раз больше.

Вообще во встроенном OoO процессоре мобильного класса несколько сот тысяч строк кода на верилоге только для ядра, потом есть еще код для менеджера когерентности кэшей, и по мелочи - контроллера прерываний итд. Далее еще есть отдельная тема с GPU, в котором еще больше кода чем в CPU. Дальше код для интерконнекта, для встроенного DSP, для нейроускорителя. Помимо кода для самого дизайна на уровне регистровых передач есть еще код для верификации и куча разнообразных скриптов для генерации верилога и для интеграции. То есть речь идет о миллионах строк на Verilog, VHDL и разных скриптовых языках чтобы скормить этот код синтезатору и программе физического синтеза.

Конечный результатом является файл в формате GDSII, который состоит из геометрических примитивов - изображений слоев кремния с примесями, которые составляют транзисторы, и дорожек из меди. Тут есть тоже отличие между занятием в субботу и последними сматфонами - на занятии мы используем учебную библиотеку примитивов (ASIC standard cell library) с технологией 40 нанометров, в то время как современные смартфоны проектируются на 3 нанометра.

Вот несколько скриншотов с того, что вы будете делать в субботу. Итак мы начинаем вот с такого кода. Это модуль ALU, один из подблоков процессора schoolRISCV:

module sr_alu ( input [31:0] srcA, input [31:0] srcB, input [ 2:0] oper, output zero, output reg [31:0] result ); always @ (*) begin case (oper) default : result = srcA + srcB; `ALU_ADD : result = srcA + srcB; `ALU_OR : result = srcA | srcB; `ALU_SRL : result = srcA >> srcB [4:0]; `ALU_SLTU : result = (srcA < srcB) ? 1 : 0; `ALU_SUB : result = srcA - srcB; endcase end assign zero = (result == 0); endmodule

Программа логического синтеза Cadence Genus превратит это код в схему - граф из логических элементов. Эта программа покажет, сколько стандартных ячеек требуется для схемы и сделает предварительную оценку, вписывается ли схема в требуемую тактовую частоту, а если не вписывается, то насколько. Если схема не вписывается в тактовую частоту, то вы можете либо оптимизировать логику, либо разбить слишком длинный путь, поместив между логикой элементы памяти - D-триггеры. В последнем случае вы можете построить или последовательный конечный автомат, или конвейер:

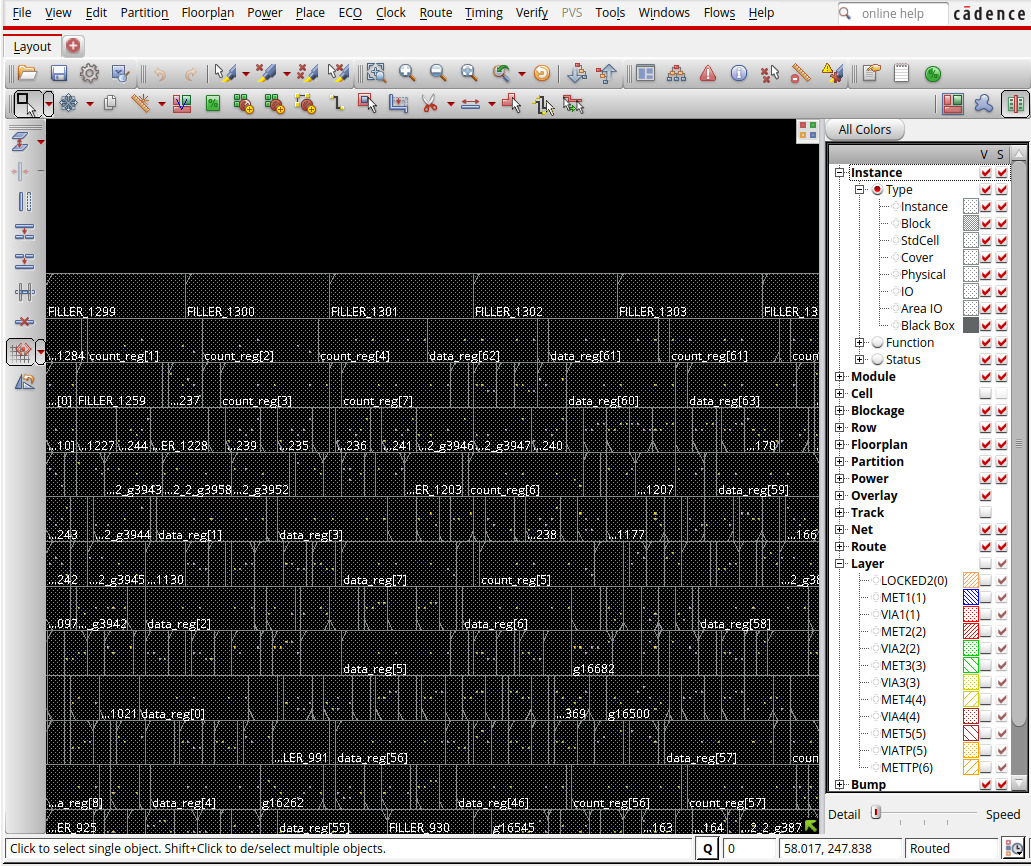

После логического синтеза начинается физический синтез (физическая имплементация), которая выполняется с помощью программы Cadence Innovus. Сначала вы строите план начального размещения (этот процесс делается частично вручную, с некоторой автоматизацией). Затем вы запускаете алгоритм детального размещения, который выстраивает стандартные ячейки вашей схемы рядами, минимизируя расстояния и задержки распостранения сигнала между ними. Ячейки называются стандартными потому, что у них одинаковая высота, и их можно так выстроить:

Потом вы запускаете программу трассировки, которая соединяет ваши стандартные ячейки дорожками. Эти дорожки могут идти в несколько слоев, но программа старается сделать соединения с минимальными задержками и минимальной скученностью, congestion. После размещения и трассировки производится более точная оценка временных задержек в схеме и вписываются ли они в бюджет тактовой частоты.

Одна из самых интересных частей занятия в субботу - это программа Cadence Joules, которая позволяет оценить динамическое энергопотребление. От энергопотребления зависит, сколько времени телефон будет работать на одном заряде батарейки, а также насколько он будет греться.

Энергопотребление схемы состоит из статического и динамического. Статическое энергопотребление пропорционально площади, а динамическое - количеству переключений. Динамическое энергопотребление может сильно меняться в зависимости от программы, которая работает на процессоре. Поэтому чтобы измерить динамическое энергопотребление, нам нужно:

При синтезе схемы извлечь из нее паразитные емкости и сопротивления (parasitic extraction).

Запустить синтезированную схему процессора на симуляторе с тестовым окружением, записывая изменения в его логических элементах во время выполнения тестовой программы.

Скомбинировать parasitics из синтеза с записью изменений во время симуляции и вычислить количество потребляемых милливаттов.

Кстати о симуляции, которая еще чаще, чем для power, применяется для функциональной верификации. В субботу вы мельком увидите среду отладки Cadence SimVision, которая по удобству и фичам наверное лучшая в идустрии. По набору фичей хорош также ее конкурент Synopsys Verdi, но по моему личному опыту Verdi бывает глючит с clipboard, а также немного менее вылизан как GUI в SimVision (но это правда спор а-ля Canon против Nikon). Выглядит SimVision так:

В качестве начальной теоретической базы по RTL (register transfer level) очень рекомендую купить вот такую книжку:

На этом я свою заметку заканчиваю, и напоминаю, что чтобы Россия смогла победить айфон или хотя бы завоевать те или иные ниши на мировом рынке микросхем и электронных устройств вообще - необходимо, чтобы большое количество современной молодежи шли не только в модный ныне data science, но и в проектирование микроэлектроники. И на этом пути твердое владение маршрутом RTL2GDSII (от кода на верилоге до GDSII файла который шлется на фабрику) - это один из пререквизитов. Конечно это не такое мудрое занятие, как создание собственной микроархитектуры или скажем написание собственных средств проектирования (EDA tools). Но набить руку на маршруте надо, как столяру владеть рубанком и стаместками. Поэтому регистрируйтесь на сайте школы, записывайтесь по емейлу Александру Биленко, info@chipexpo.com и приходите!