Design Automation Conference (DAC) - главная выставка софтверных компаний, которые создают средства проектирования чипов. Именно на ней появляются стартапы, которые определяют проектирование через 10-15 лет (например появление Synopsys на рубеже 1980-1990-х привело к появлению iPhone в середине 2000-х).

На DAC помимо выставки и официальных докладов есть также и poster session - молодые исследователи из университетов вывешивают в виде плакатов, чем они занимаются. Я методически сфотографировал все постеры во время последней конференции DAC в Сан-Франциско, и вот перед вами картина маслом:

6 постеров по новой модной теме "Приблизительного компьютинга" ("Approximate Computing"), когда вычислениям разрешается быть неточными (например в нейросетке) если это экономит энергопотребление или делается быстрее.

Более 30 постеров так или иначе трогают тему нейросетей:

16 постеров по аппаратному ускорению нейросетей. Из них:

два по теме ReRAM,

два по нейроморфным процессорам,

один по тематике CGRA (Coarse Grained Reconfigurable Array - это такая матрица из недопроцессоров, по аналогии с FPGA, но ячейки соединяются не сигналами, а шинами, и в каждой ячейке есть сиквенсер, типа маленькая программа),

один толерантный к глюкам от прилетевшего из космоса луча.

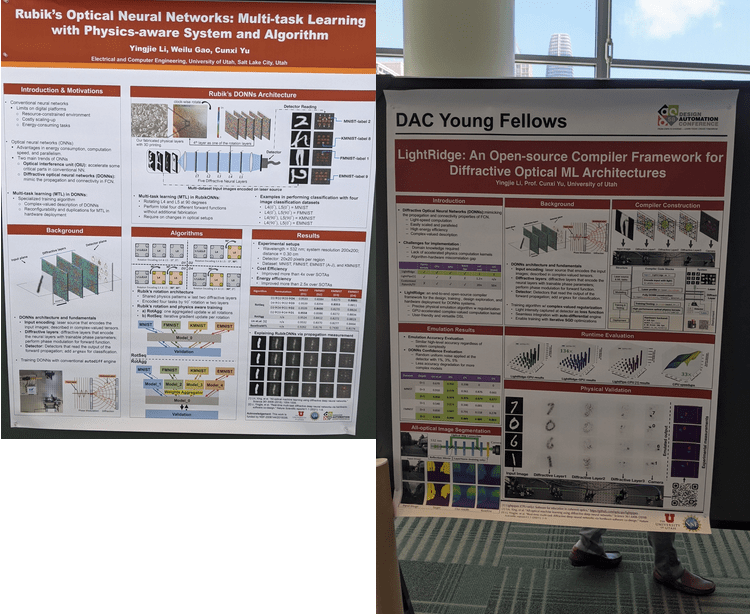

2 постера - по оптическим нейросетям.

3 постера - о нейросетях вообще (без контекста архитектуры ускорителя).

2 постера - о вычислениях в памяти (in memory computing). Не разобрался, что это такое, но это тоже привязывается к нейросетям.

7 постеров - о приложениях нейросетей, в том числе для дронов, сейсморазведки, сбора энергии (energy harvesting - это еще что такое?) и здравоохранения.

2 постера - все о тех же нейросетях, но на краю, то бишь во встроенных устройствах (Edge AI).

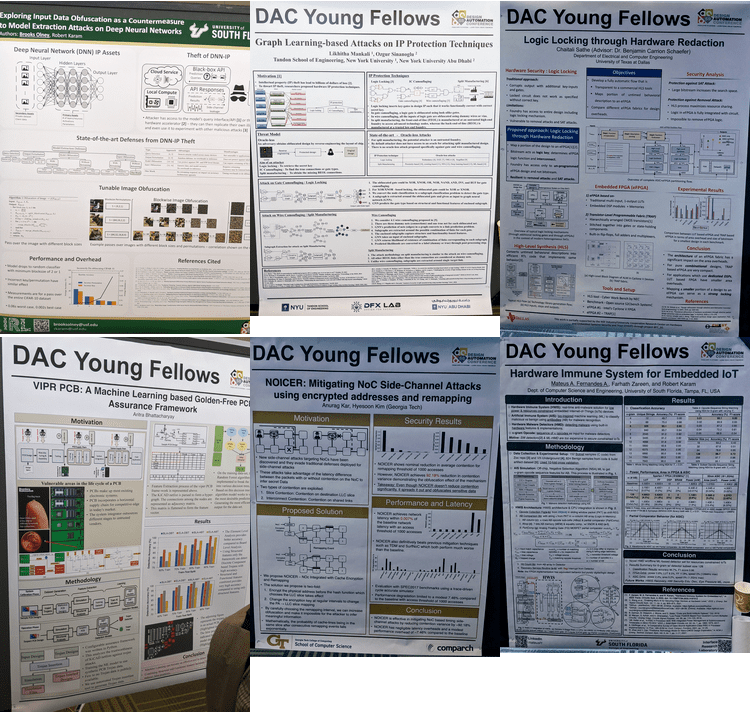

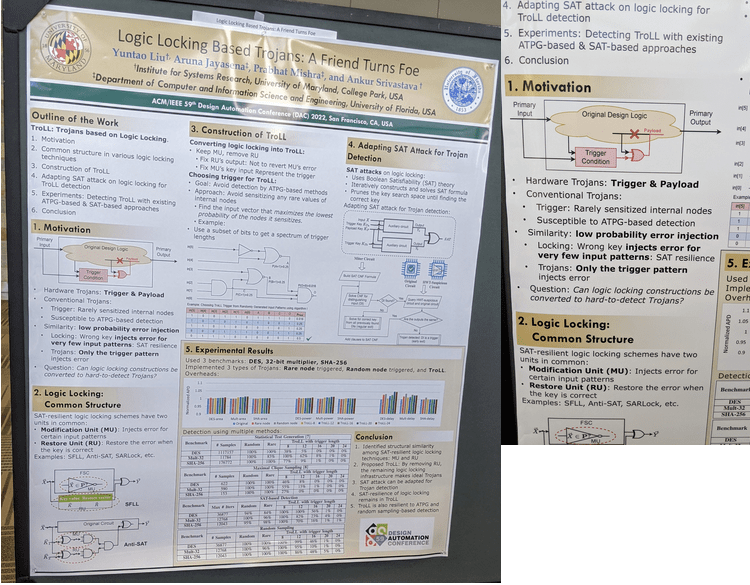

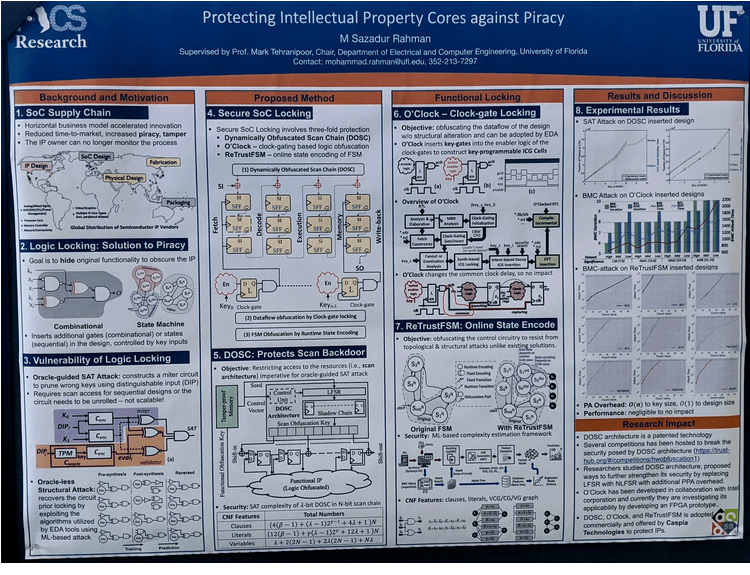

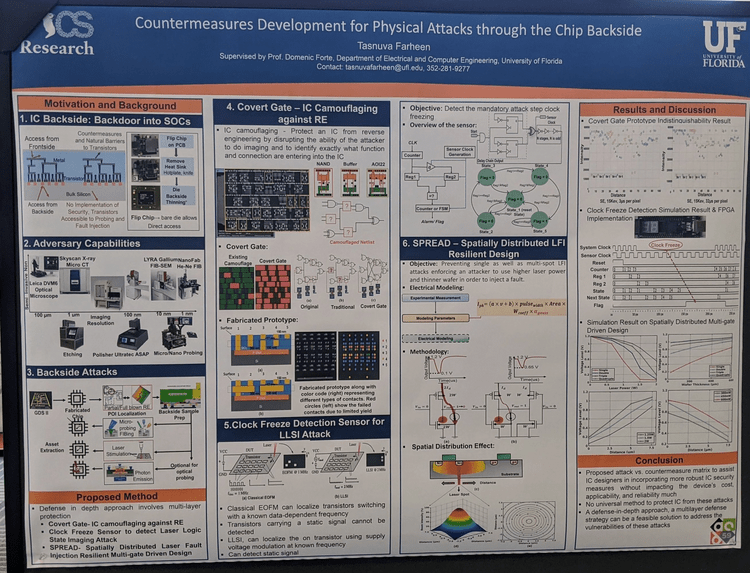

10 постеров про кибербезопасность, в том числе:

про защиту IP блоков,

про аппаратные трояны в микросхемах и платах (а в России говорят "закладок не бывает!"),

side-channel attacks (это было на Хабре) и физические атаки (не понял что это такое)

"аппаратный иммунитет"

нахождение уязвимостей

6 постеров на почтенную тематику физического проектирования, хотя пару раз нейросети влазят и туда:

Постер про энергопотребление

Про проектирование смешанных аналогово-цифровых схем

Про глобальную трассировку (routing) цифровых схем

Про размещение и трассировку цифро-аналоговых преобразователей

2 постера про использование машинного обучения в физическом проектировании

Дальше всего понемножку:

3 постера про высокопроизводительные вычисления (High Performance Computing - HPC)

2 постера про датацентры

1 постер про аппаратный ускоритель, но без слова "нейросеть"

2 постера про моделирование систем на кристалле - System-on-Chip - SoC

1 постер про сети на кристалле

1 постер про сопряжение с биосигналами

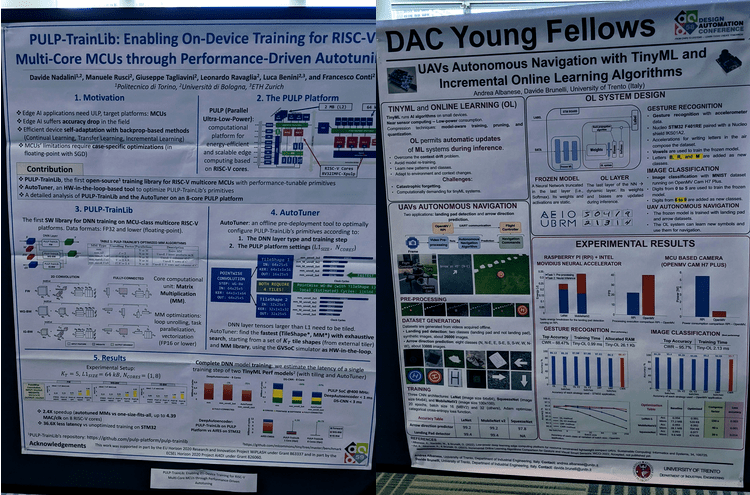

2 постера привязаны к архитектуре RISC-V - это умеренно модно, не так как нейросети и трояны

1 постер про проектирование RISC-ядер (не обязательно с архитектурой RISC-V) как комбинацию из конечных автоматов для стадий конвейера (ну, можно рассматривать и так, хотя это неканоническое изложение)

2 постера про вечно молодую тематику высокоуровневого синтеза, который уже 30 лет грозиться вытеснить обычный за 5 лет

4 постера про совсем низкий уровень - катушки, проходы в микросхемах, устройства статической памяти и сенсоры

2 постера про будущее всего человечества - квантовый компьютинг

Постер про панель дисплея

Постер про сравнение процессоров в Бразилии

Постер про формальную верификацию, в котором упоминается Coq, Haskell, SystemVerilog и контроллеры DRAM памяти

Ну и кто-то еще одну сортировку на FPGA написал - такое на таких конференциях бывает

Все постеры ниже (я также выложил версию этой заметки с большими картинками - если вы хотите покопаться детальнее, а не просто обозреть с птичьего полета, это лучше делать там):

03. Approximate Computing – Compilers for HPC

04. Approximate Computing – Power-efficient multipliers

05. Approximate Computing – Logic Synthesis

06. Approximate Computing – DNN

07. Approximate Computing – DNN

08. Approximate Computing – DNN

09. Neural Networks – Hardware Accelerators

10. Neural Networks – Hardware Accelerators

11. Neural Networks – Hardware Accelerators

12. Neural Networks – Hardware Accelerators

13. Neural Networks – Hardware Accelerators

14. Neural Networks – Hardware Accelerators

15. Neural Networks – Hardware Accelerators

16. Neural Networks – Hardware Accelerators

17. Neural Networks – Hardware Accelerators

18. Neural Networks – Hardware Accelerators

19. Neural Networks – Hardware Accelerators – ReRAM

20. Neural Networks – Hardware Accelerators – ReRAM

21. Neural Networks – Hardware Accelerators – Neuromorphic

22. Neural Networks – Hardware Accelerators – Neuromorphic

23. Neural Networks – Hardware Accelerators – CGRA

24. Neural Networks – Hardware Accelerators – Fault-tolerant

27. Neural Networks – General – Train only on important samples

28. Neural Networks – General – NVidia-based

29. Neural Networks – General – Spiking

30. Neural Networks – In-memory computing

31. Neural Networks – In-memory computing

32. Neural Networks – Applications – Deploying NN on drones

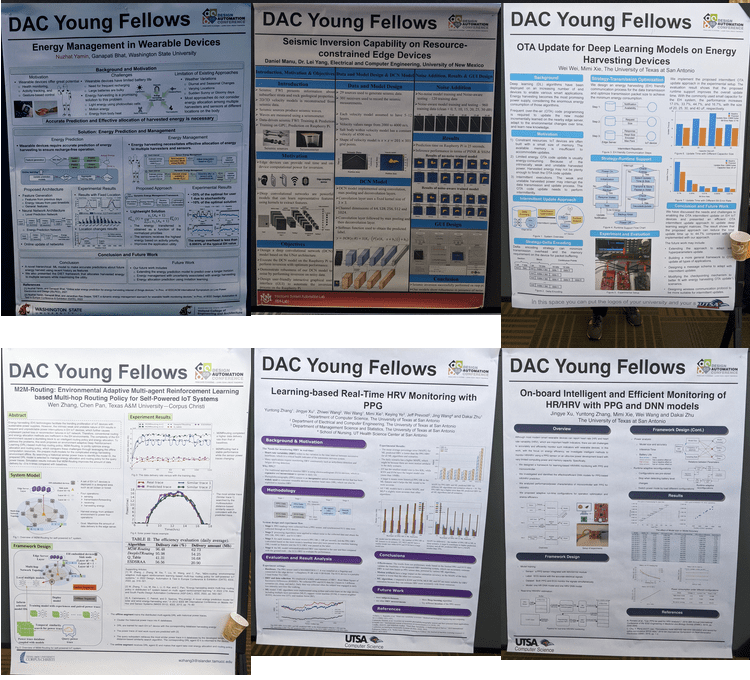

33. Neural Networks – Applications – To predict energy management in wearable devices

34. Neural Networks – Applications – For seismic computations

35. Neural Networks – Applications – For energy harvesting

36. Neural Networks – Applications – For energy harvesting

37. Neural Networks – Applications – Healthcare

38. Neural Networks – Applications – Healthcare

39. Neural Networks – Edge AI – MCU

40. Neural Networks – Edge AI – MCU

47. Security – Hardware trojans in PCB

48. Security – Side-channel attacks

51. Security – Hardware Immune System

45. Security – Hardware trojans in ASIC

46. Security – Hardware trojans in ASIC

49. Security – Physical attacks

52. High-performance computing – Power and thermal management emulation

53. High-performance computing – Reconfigurable smart switches

54. High-performance computing – Combined with ML

57. Hardware accelerators – ASIC

58. System-level design – Simulation

59. System-level design – Simulation

60. System-level design – Biosignal processing

63. RISC-V – Return-Oriented-Programing attacks

64. RISC-V – Representing a generic RISC microarchitecture as multiple state machines

69. Physical Design – Mixed signal

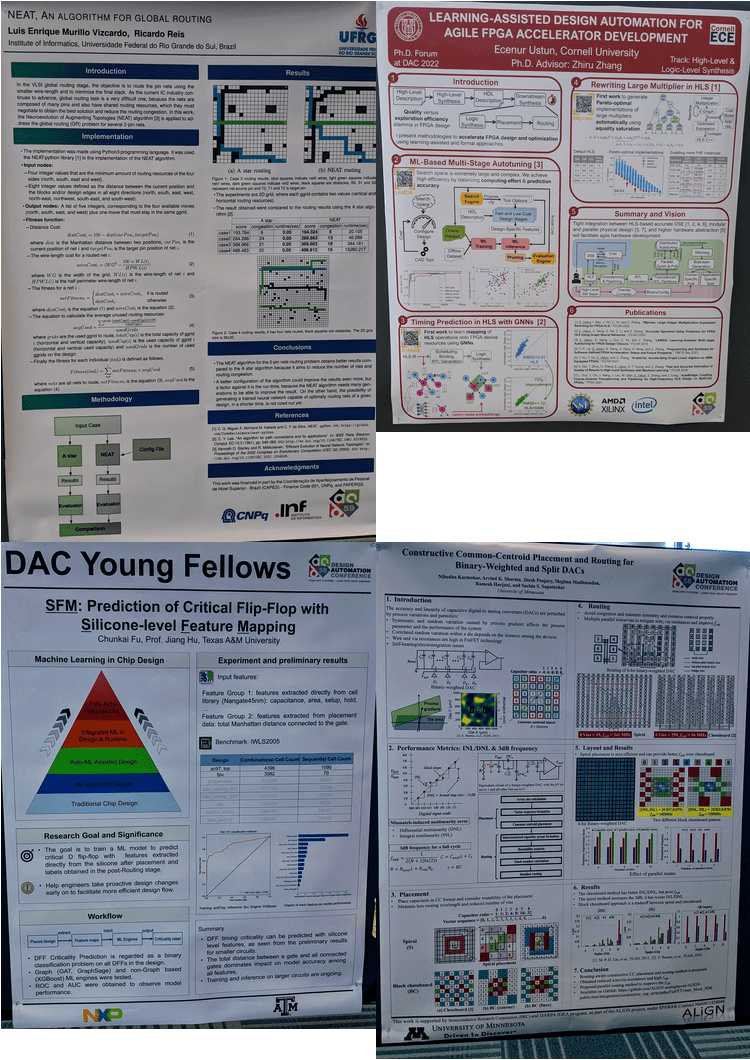

67. Physical Design – Global routing

70. Physical Design – ML-assisted design

71. Physical Design – ML-assisted design

72. Physical Design – PnR for digital-to-analog converters

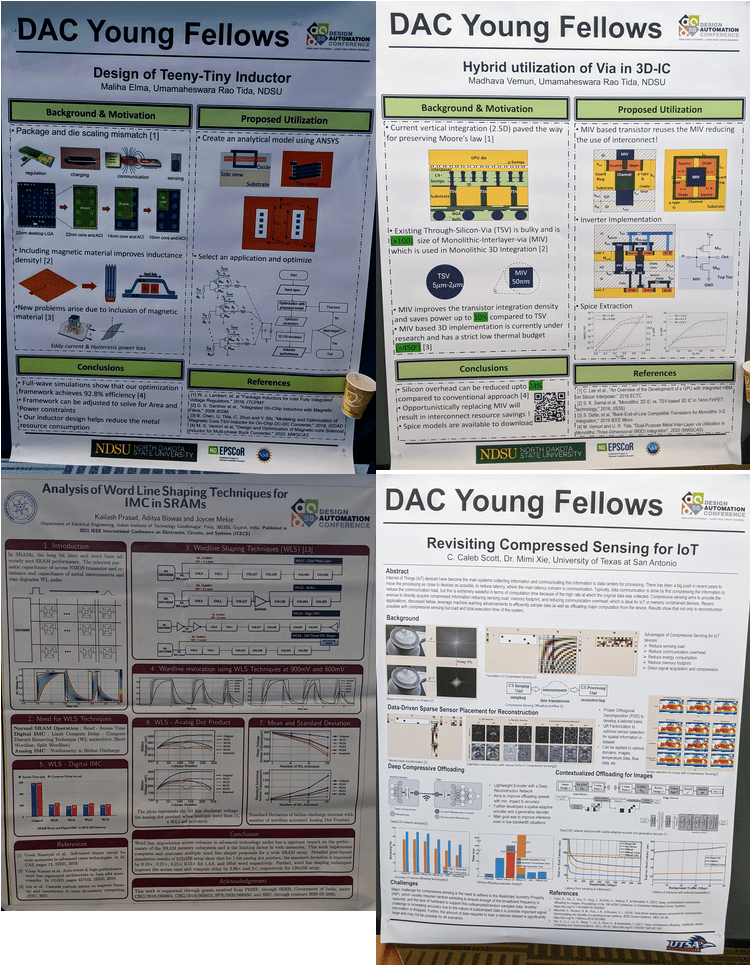

73. IC components on low level – Inductor design

74. IC components on low level – Via utilization

75. IC components on low level – SRAM structure

76. IC components on low level – Sensors for IoT

79. Misc – Display panel development

81. Misc – Formal verification – Coq DRAM controllers Haskell SystemVerilog

82. Misc – Serial sorter on FPGA

Если вы хотите почитать еще про DAC, я написал и другие отчеты, в частности: