В СССР на базе ЕС ЭВМ было создано несколько типов многомашинных и многопроцессорных комплексов, первым из которых стал ВК-1010, объединяющий вместе две ЭВМ ЕС-1030.

Микроконтроллеры, цифровая электроника, ОС…

В СССР на базе ЕС ЭВМ было создано несколько типов многомашинных и многопроцессорных комплексов, первым из которых стал ВК-1010, объединяющий вместе две ЭВМ ЕС-1030.

Заключительная часть серии статей, посвящённой процессору ЭВМ ЕС-1030. Рассматриваются пульт управления, обсуждается (не)эффективность идей, положенных в основу конструкции процессора и организации его микропрограмм, а также анализируется степень соответствия внутреннего устройства этого процессора с процессором машины IBM 360/50.

В предпоследней статье цикла, посвящённого процессору и памяти ЭВМ ЕС-1030, говорится об известных из доступных источников особенностях микропрограмм.

Очередная статья цикла об устройстве процессора ЭВМ ЕС-1030 рассказывает об аппаратном контроле работы ЦП, обработке ошибок и сбоев и о средствах диагностики.

В этой статье рассматривается устройство и логика работы блока обращения к оперативной памяти процессора ЭВМ ЕС-1030.

Продолжение цикла, посвящённого процессору ЭВМ ЕС-1030. Хотя, строго говоря, оперативная память в состав процессора не входит, её характеристики и режимы работы весьма значительно влияют на устройство и работу процессора, а поэтому заслуживают внимания.

Продолжение цикла статьей о процессоре и памяти ЭВМ ЕС-1030. В данной статье собраны доступные сведения о блоке микропрограммного управления и о долговременном запоминающем устройстве — постоянной памяти микропрограмм.

Очередная статья цикла, посвящённого процессору ЭВМ ЕС-1030 и рассказывающая об устройстве наиболее громоздкого (и, возможно, наиболее безумного по конструкции) блока этой машины.

Продолжение цикла статей, посвящённого внутреннему устройству и работе процессора ЭВМ ЕС-1030.

Продолжение начатой ранее серии статей по процессору и памяти ЭВМ ЕС-1030, посвящённое системе синхронизации и блокам внутренней памяти процессора.

Новый цикл статей, посвящённый процессору и памяти хронологически второй и, вероятно, самой неудачной машины Единой системы — ЕС-1030.

Окончание серии статей, посвящённых процессору ЭВМ ЕС-1020. Предыдущие статьи:

• общая структура и система синхронизации;

Продолжение серии статей, посвящённых процессору ЭВМ ЕС-1020. Предыдущие статьи:

• общая структура и система синхронизации;

Продолжение серии статей, посвящённых процессору ЭВМ ЕС-1020. Предыдущие статьи:

* общая структура и система синхронизации;

Продолжение серии статей о внутреннем устройстве процессора ЕС-1020. Предыдущие статьи:

* общая структура и система синхронизации;

Эта небольшая статья продолжает цикл публикаций о внутреннем устройстве процессора ЕС-1020 и описывает его блок регистров. Предыдущие статьи:

* общая структура и система синхронизации;

Продолжаем рассказ о внутреннем устройстве процессора ЭВМ ЕС-1020. Предыдущие статьи посвящены общей структуре и системе синхронизации и микропрограммному управлению.

Продолжение серии статей, посвящённых устройству процессора ЭВМ ЕС-1020. На сей раз речь пойдёт о блоке микропрограммного управления — в первую очередь, о формате и назначении отдельных полей микрокоманды.

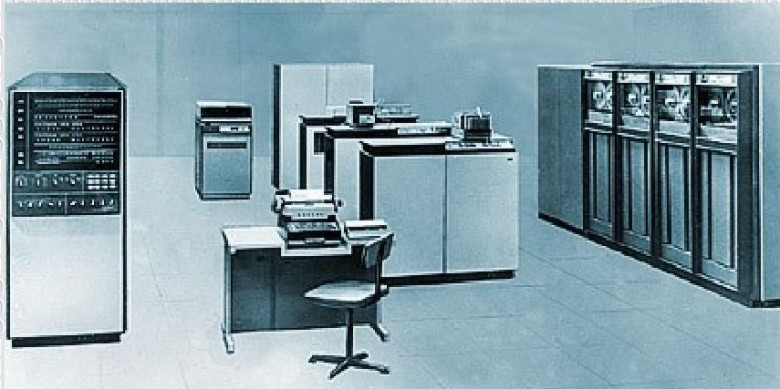

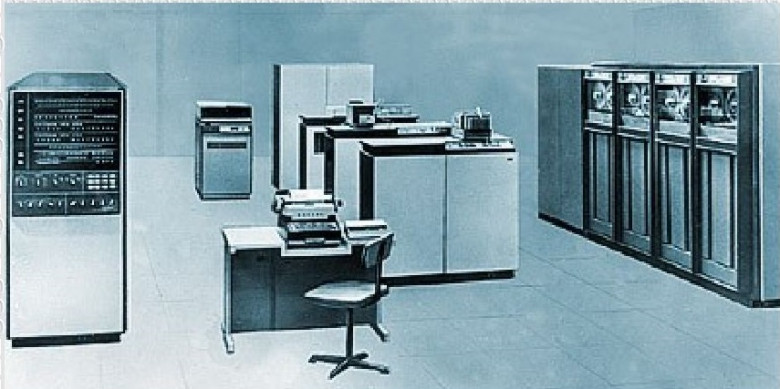

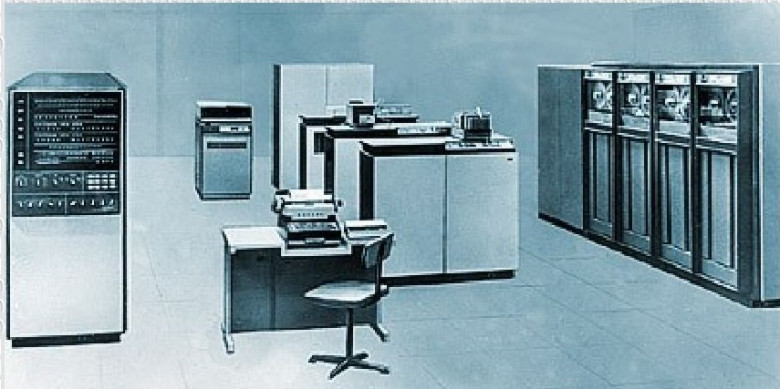

Первая из серии статей, посвящённых внутреннему устройству процессора ЭВМ ЕС-1020, в которой рассматривается система синхронизации. В предшествующих статьях были освещены важнейшие особенности архитектуры и конструктивное исполнение ЕС ЭВМ.

Эта статья продолжает предыдущую. Будучи задуманной как пара вводных абзацев к рассказу об устройстве процессора ЕС-1020, она разрослась до неприличных размеров, а поэтому была раздута ещё больше и превращена в отдельную публикацию. Ну а ЕС-1020 переносится на ближайшее будущее.