Комментарии 68

У меня предвзятое отношение к размеру ЗП в отечественных хардварных компаниях.

Интересно, где больше платят, в разработке ПО

Есть некоторая контора, которая разрабатывает параллельную архитектуру процессора. Год-два назад искали от 45 т.р. программиста на компилятор, фпга-шника в такую же стоимость озвучивали.

Сфера деятельности узкая, потому рабочих мест не много, работодатели сильно манипулируют этим.

Сфера деятельности узкая, потому рабочих мест не много, работодатели сильно манипулируют этим.Казалось бы что это значит наоборот, кандидаты должны ломить ЗП в пять раз больше чем скажем распространенные джависты. Но вместо того что бы пойти в джависты, они видимо прутся куда возьмут.

Казалось бы что это значит наоборот, кандидаты должны ломить ЗПОно так не работает, оно работает примерно так:

Приходишь к работодателю и изрекаешь:

— повысьте ЗП

— а то что?

— уйду

— к кому

— к ххх

— ну хорошо, иди.

Причем это работает во всех узких специализациях (в РФ).

джависты

Ну какая Джава, например, бородатому дядьке под 45 лет, с двумя детьми?

Причем это не сферический конь, а вполне живой бывший коллега.

Насмотрятся таких, вот, Постов и идут в узкую специализацию. Хотя таких специалистов нужно с десяток тысяч на _всю_ планету.

Те кто занимается разработкой вроде как з/п на уровне.

"з/п на уровне" это сколько?

и просьба назвать хотя-бы несколько примеров компаний с такой з/п

Питер: от 60-80

Мск: 60-110

Сложность: 4-6 слоев, DDR(2/3)/ARM7-11, фильтры, linux, драйвера под них и т.п.

Питер: от 60-80Но это же ЗП меньше чем у среднего джависта!?

Мск: 60-110

Ничего удивительного, такие человеко-орекстры мало продуктивны: Тут уже как минимум схемотехник-технолог и программист.

Часто сюда приплетают и разработку корпуса и работа с производством и подбор компонентов и много ещё чего. Нередко такие компании ещё и в убыток работают и компы не новые. А некоторые за 60тр заставляют ещё и участвовать в маркетинге своих поделий или искать клиентов.

На мероприятии будет два отделения:

1. Семинар по обмену опытом преподавания электроники в университетах — программа здесь — https://nanoandgiga.com/ngc2017/documents/digital-design-seminar.pdf

2. Школа для студентов и аспирантов — программа здесь —

https://nanoandgiga.com/ngc2017/documents/digital-design-school.pdf — вместе с практическими упражнениями на FPGA платах

И на одном, и на другом мероприятии будет обсуждатся тематика языков описания аппаратуры, IP-блоки, архитектура и микроархитектура, синтез и верификация, FPGA и ASIC и производство.

Спасибо большое за подборку, выглядит завлекательно.

FPGAs Fundamentals, Advanced Features, and Applications in Industrial Electronics

Кстати, правильно ли я понимаю, что интерпретатор для Верилога — это литографический Степпер? Или я какой-то промежуточный шаг забываю?

Помимо цепочки преобоазований, которая ведет от верилога к литографическому степперу, есть также несколько программных симуляторов Верилога, в том числе бесплатные — Icarus Verilog, Mentor ModelSim, симулятор в Xilinx Vivado и платные — Synopsys VCS, Cadence IUS итд.

Извиняюсь, если сказал какую-нибудь глупость, повторюсь, что только начал вникать в тему, и пока больше теорфизическую оптику вкуриваю.

Mentor ModelSim

Я что-то пропустил и Моделсим стал бесплатным?

Статья как-бы подразумевает, что в нормальные компании вроде Intel или Samsung всё равно с такими знаниями лучше не соваться?

Итого сфера на порядок более сложная и ответственная, чем какое-нибудь веб-программирование, работать придётся на уровне абстракций из 70-х в программах из 90-х, а список реальных работодателей весьма ограничен, при этом никаких тебе bleeding edge проектов как в Intel: будешь пилить то, что уже и так выпускается десятком fabless и не fabless фирм, скорее всего — для какой-нибудь полувоенной "отечественной" конторы со всеми вытекающими…

Ну такое.

В последние несколько лет российские компании стали использовать те же тулы, что и компании в Silicon Valley

Девочка Даша упомянутая в тексте реализовала свой процессор на плате с Altera FPGAa, которая сейчас является частью Интела и вообще переназвана Intel FPGA.

российские компании стали использовать те же тулы, что и компании в Silicon Valley

Я тоже могу себе поставить какой-нибудь Cadence IC, это не сделает меня равным инженерам

Intel :) Тут же нужно образование, и опыт, и культура — вот это всё...

Впрочем сам этот Cadence IC и ему подобные выглядят как артефакты из 90-х, значительно отставая от более современных и удобных средств мейнстримовой разработки. А отсюда и вопрос — стоит ли с этим вообще заморачиваться, за более низкую по сравнению с теми же веб-программистами зарплату и возможность реального трудоустройства в полторы конторы...

Вот погуглите Synopsys Baikal, а потом Synopsys Intel.

В двух метрах от меня на работе сидит бывший инженер Интела. В Интеле есть и русские инженеры, например Амир Аупов www.facebook.com/profile.php?id=100001401986745 или например был Денис Хартиков (он сейчас в NVidia)

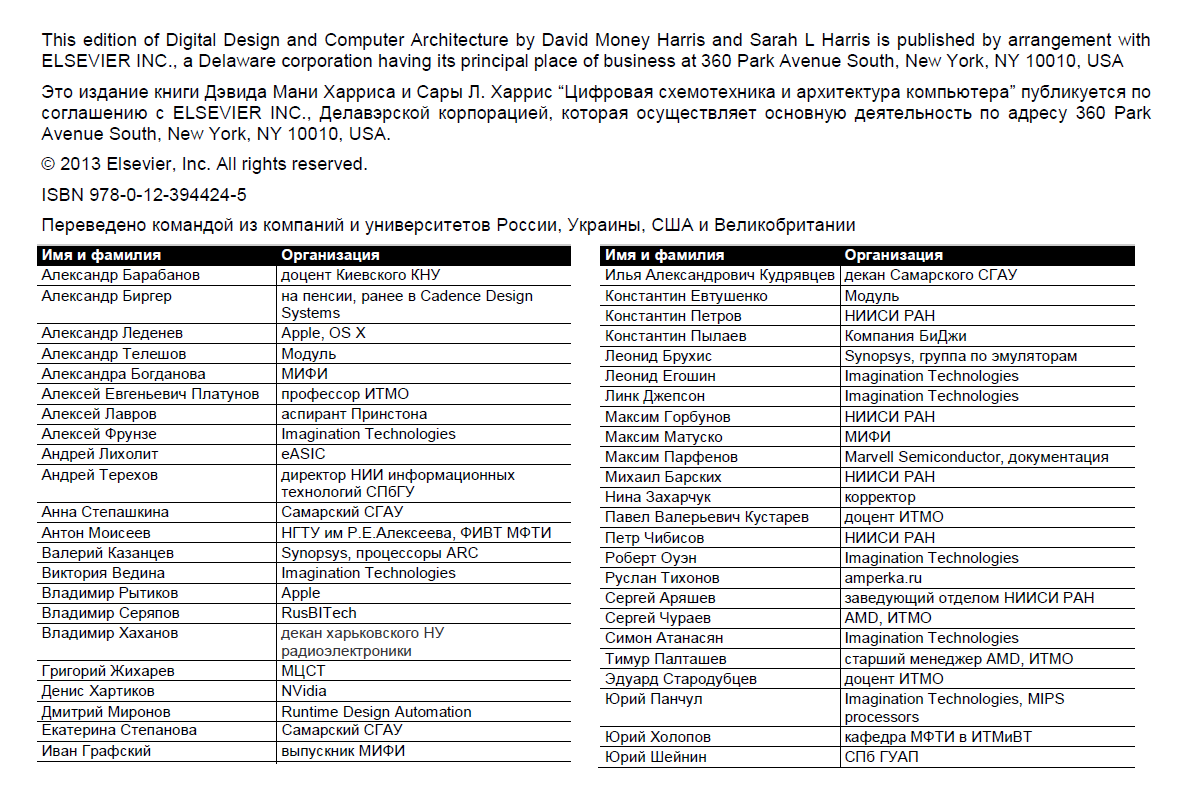

Он был в числе людей, которые участвовали в переводе Харрис & Харрис

Поговорите с ним, насколько все это применимо к интелу — https://www.facebook.com/denis.khartikov

Что вы имеете в виду под «более современными и удобными средствами мейнстримовой разработки»

Давайте я вам видео про Xcode, а вы мне видео про Synopsys что-у-них-там.

В Интеле есть и русские инженеры

Наверное и молдовские есть, и африканские, но каково их процентное соотношение и насколько реалистично устроится в Интел, следуя советам из статьи?

Меня приглашали работать в Интеле, я могу сказать абсолютно точно, что все интеловские инженеры, которые пишут RTL Verilog для реализации микроархитектуры или unit-level тестбенчи, в некоторый момент своего обучения прошли именно то, о чем я пишу в посте — Verilog, синтез, верификация, SystemVerilog, микроархитектура по Хеннесси-Паттерсону итд. А что еще? Это основа их методологии.

Вот первое нагугленое:

Intel Selects Synopsys As Its Primary EDA Supplier

Semiconductor and EDA Leaders Sign Multi-Year Commercial, Collaboration Agreement

news.synopsys.com/index.php?s=20295&item=122371

Вам перевести? Какое слово тут неоднозначно?

И вот про Байкал:

Baikal Electronics Selects Synopsys Solutions to Accelerate the Design and Verification of Their Advanced SoCs

news.synopsys.com/2015-03-16-Baikal-Electronics-Selects-Synopsys-Solutions-to-Accelerate-the-Design-and-Verification-of-Their-Advanced-SoCs

Или вот посмотрите чему учат на кафедре Интела в МФТИ — там работает в частности Павел Крюков https://mipt.ru/drec/about/ilab/projects/current_projects/mipt-mips/

https://mipt.ru/education/chairs/microprocessors/

Я говорю о том, что среды для разработки на Verilog и ему подобном по удобству для программиста отстают от более удобных и активно разрабатываемых мейнстримовых IDE типа Xcode. Также нет их версий под мак и т. п. Всё выглядит сурово и по хардкору, как в 90-х.

Это одно из неудобств жизни, но это не фатально.

В том же Quartus или ModelSim встроенные редакторы действительно ужасны чуть меньше чем полностью. Данный факт коробит ровно до осознания того, что это очень ускоспециализированный софт. Как итог: Verilog разработка у меня живет в любимом VSCode, ModelSim c нужными параметрами запускается из скрипта (a-la makefile), Quartus — только для синтеза.

В качестве аналогии: у gcc вообще нет графического интерфейса, но как компилятор он свою функцию выполняет.

Как-то так.

по удобству для программиста

Может всё дело в том, что для hdl-разработчика в первую очередь важно не то, что для программиста? А то я со стороны железячника тоже много доброго могу написать про отображение регистров процессора в отладчике xcode…

Автодополнение, рефакторинг и сглаженные шрифты точно не важны для разработчика HDL?

И как там по поводу человеческого отображения в Xcode набора регистров процессора при отладке приложения на подключенном устройстве? :)

Xcode не для копания в регистрах. По вашей аналогии среды разработки на HDL не для редактирования кода?

P.S. Всегда пользуюсь для редактирования кода тем редактором, который нравится мне, а не тем, который нравится авторам среды разработки.

список реальных работодателей весьма ограничен

Там ещё куча фишек, что не возьмут в конкурирующую компанию, в случае ухода из одной.

Так что список можно делить смело на три.

Ну такое.

В РФ точно не стоит за такое браться, выгоднее хотя бы ПЫХ программистом, за большие деньги и меньшие проблемы с трудоустройством.

academic.csuohio.edu/chu_p/rtl/index.html

Навеяло темой статьи.

Проза в память о разработчике компьютера Sprinter-2000 с некоторыми техническими деталями при использовании Altera FPGA (некоторое популярное изложение возможностей софт процессоров)

Мак Иван http://litresp.ru/chitat/ru/%D0%9C/mak-ivan/putj-domoj Путь домой

Следущие шаги в черной магии процессоростроения после того, как вы освоили Харрис & Харрис

ЕМНИП, в русском языке есть интересный момент касательно склонения мужских и женских имён собственных с нулевым окончанием. Думаю, правильнее было бы написать «Харриса & Харрис».

Пока держите вчерашнюю фотку, на которое есть в том числе и несколько разработчиков ядра P5600 внутри Байкала:

на edX есть два курса где лабораторные работы делаются на реальных платах:

www.edx.org/course/embedded-systems-shape-world-multi-utaustinx-ut-6-20x

www.edx.org/course/embedded-systems-shape-world-utaustinx-ut-6-10x

www.edx.org/course/real-time-bluetooth-networks-shape-world-utaustinx-ut-rtbn-12-01x-0

по микроконтроллерах курсов не много, но они есть. К сожалению по FPGA их нет…

Идея создать серию таких удаленных курсов есть, над ней возможно смогут работать кто-нибудь из преподавателей вузов, которые участвуют в конференции в Томске 18-22 сентября — https://nanoandgiga.com/ngc2017/digital-design

На мероприятии будет два отделения:

1. Семинар по обмену опытом преподавания электроники в университетах — программа здесь — https://nanoandgiga.com/ngc2017/documents/digital-design-seminar.pdf

2. Школа для студентов и аспирантов — программа здесь —

https://nanoandgiga.com/ngc2017/documents/digital-design-school.pdf — вместе с практическими упражнениями на FPGA платах

И на одном, и на другом мероприятии будет обсуждатся тематика языков описания аппаратуры, IP-блоки, архитектура и микроархитектура, синтез и верификация, FPGA и ASIC и производство.

openedu.ru/course/spbstu/CUMICR2

Следущие шаги в черной магии процессоростроения после того, как вы освоили Харрис & Харрис