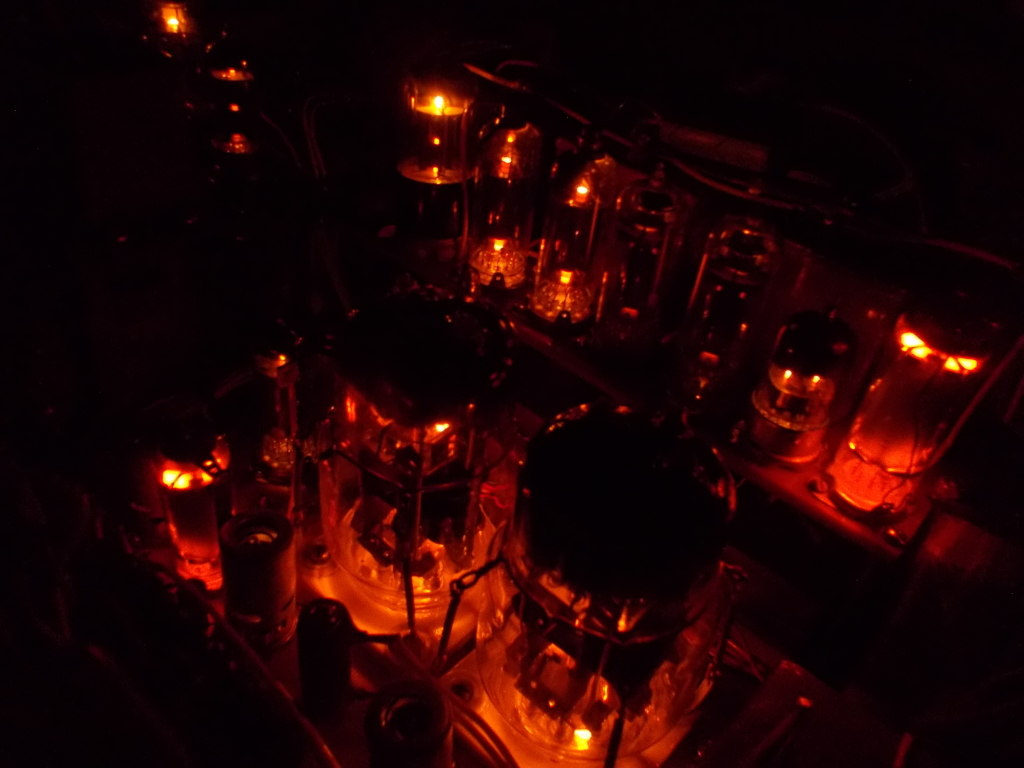

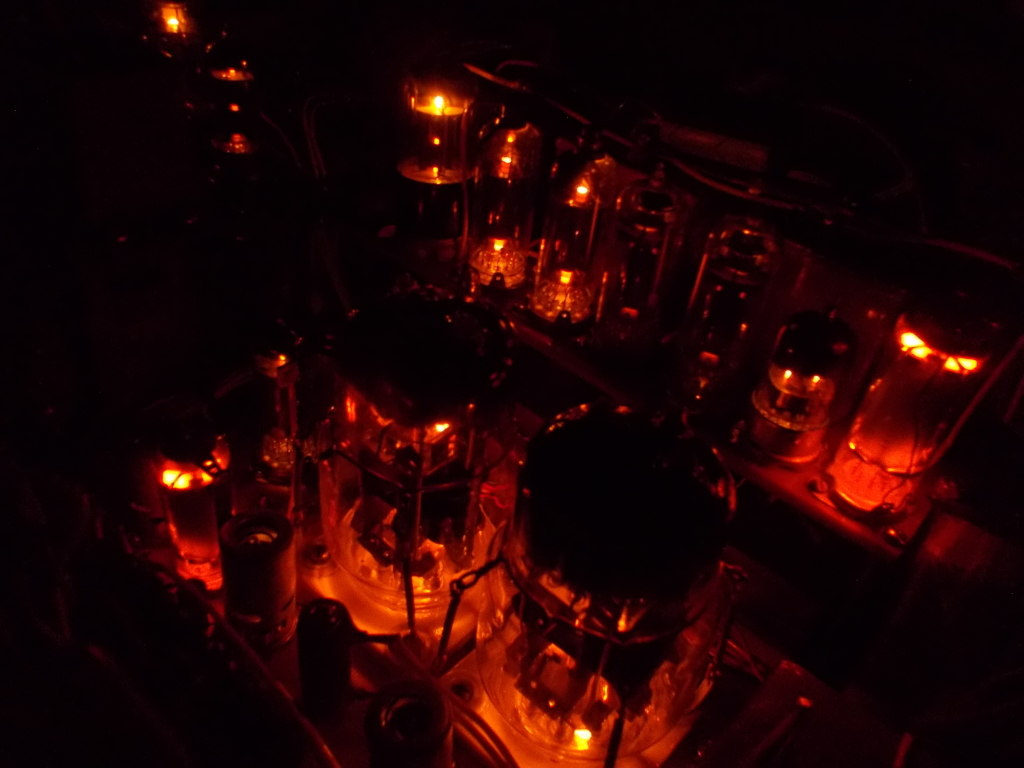

Ламповый лабораторный источник питания для ламповых устройств

Проектирование электронных схем

Твои глаза болят и чешутся чаще, чем тебе хотелось бы брать больничные перед релизами? Тогда это устройство для тебя. Помимо этого, ты на время станешь киберпанком (почти).

Применять после консультации с вашим рипером (врачом).

Одним из показателей качества аналогового тракта приемника является коэффициент шума (КШ). Чем он меньше, тем меньше дополнительных шумов вносит аналоговый тракт в сигнал, поступающий на его вход.

Выбор устройств с низким КШ может позволить увеличить дальность или скорость передачи данных в канале связи без увеличения энергопотребления и размеров антенн.

В [1] рассматриваются 3-и метода измерения коэффициента шума:

1. Метод Y-фактора. Этот метод предполагает использование генератора шума.

2. Метод генератора сигнала с удвоением мощности.

3. Метод прямого измерения шума (метод холодного источника)

1-й метод заключается в использовании генератора шума, достаточно распространен и хорошо описан в инструкциях на приборы. В статье подробнее рассматривается пример измерения коэффициента шума при помощи анализатора спектра, используя 2 и 3 способ. Также приводятся возможные ошибки при измерении коэффициента шума подобными методами и сравнение полученных результатов на практике. В свое время использовать эти методы для оценки КШ меня побудило отсутствие в доступе генератора шума на нужный диапазон частот. Также эти способы позволяют измерять устройства с большим коэффициентом шума, такие как преобразователи частоты, усилители мощности.

В своей прошлой статье я концептуально показал как устроены основные логические элементы РТЛ. Сегодня на их базе рассмотрим более сложные элементы.

Как я и обещал в предыдущей статье, представляю вашему вниманию свой независимый пользовательский отзыв на новинку этого книжного сезона: русскоязычную версию третьего оригинального издания знаменитой книги «Искусство схемотехники».

Ещё очень давно, как только я начал интересоваться цифровой электроникой, я изучал логические элементы и сразу хотел что-то собрать на их основе, но самих микросхем логики у меня изначально не было, поэтому я решил собрать их самому на основе биполярных транзисторов NPN типа и резисторах.

Такая логика называется РТЛ (резисторно-транзисторная логика).

Велосипед я не изобрёл, просто собрал кучу разного материала, плюс сам экспериментировал. Схемы примера собирал в программе Multisim и тестировал на настоящих транзисторах PN2222A. И вот что у меня вышло.

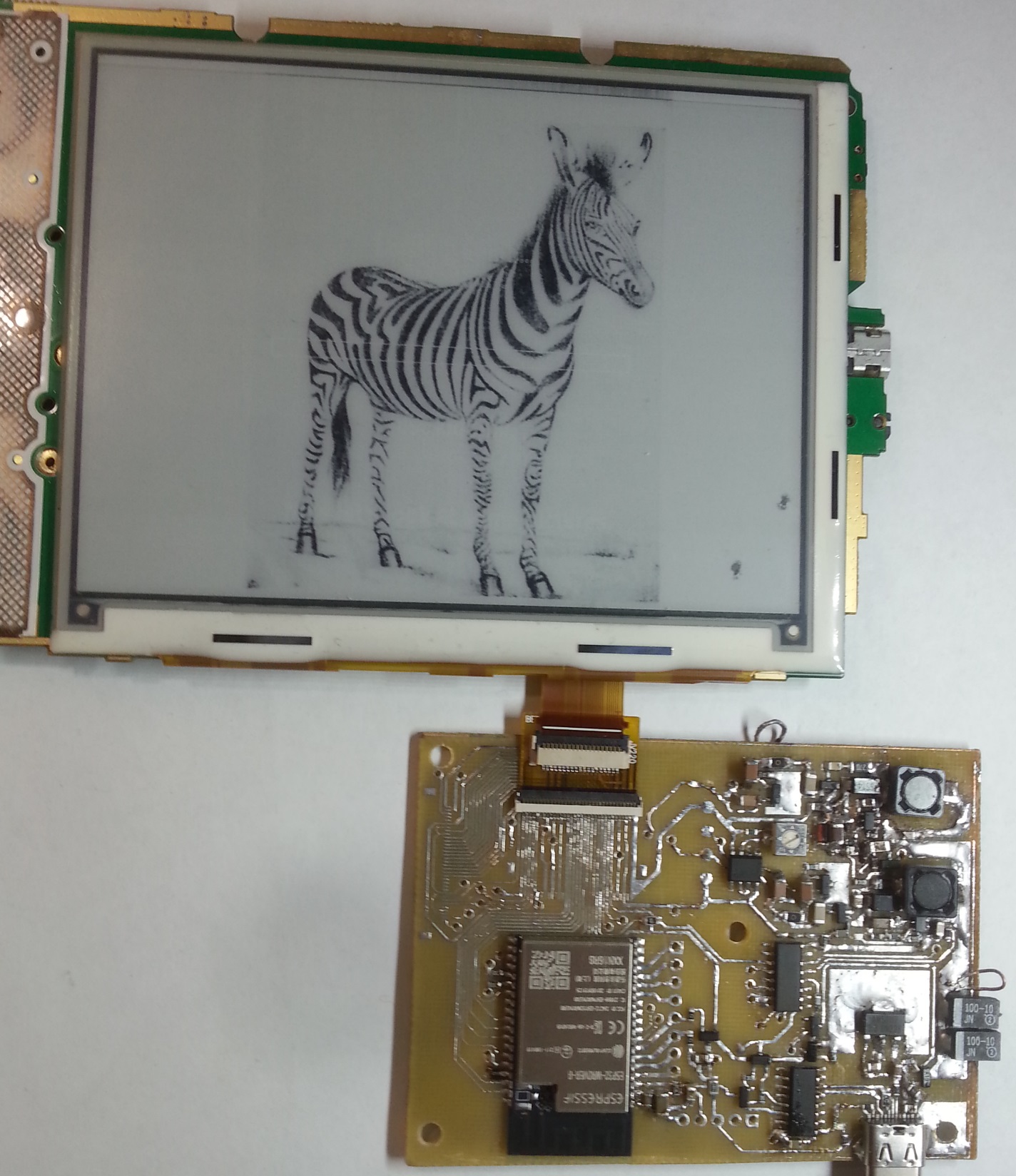

В этой статье мы рассмотрим процесс создания умной светодиодной системы под названием Smart LED. Этот проект основан на микроконтроллере ESP8266 и адресной светодиодной ленте.

Система Smart LED позволит вам не только наслаждаться красивой подсветкой, но и синхронизировать её с музыкой. Вы также сможете управлять системой с помощью голосового ассистента Алиса.

Проект на GitHub

Делюсь своим опытом применения PSE контроллера HS104PBI(PTI) от китайского производителя. Описываю свои грабли=)

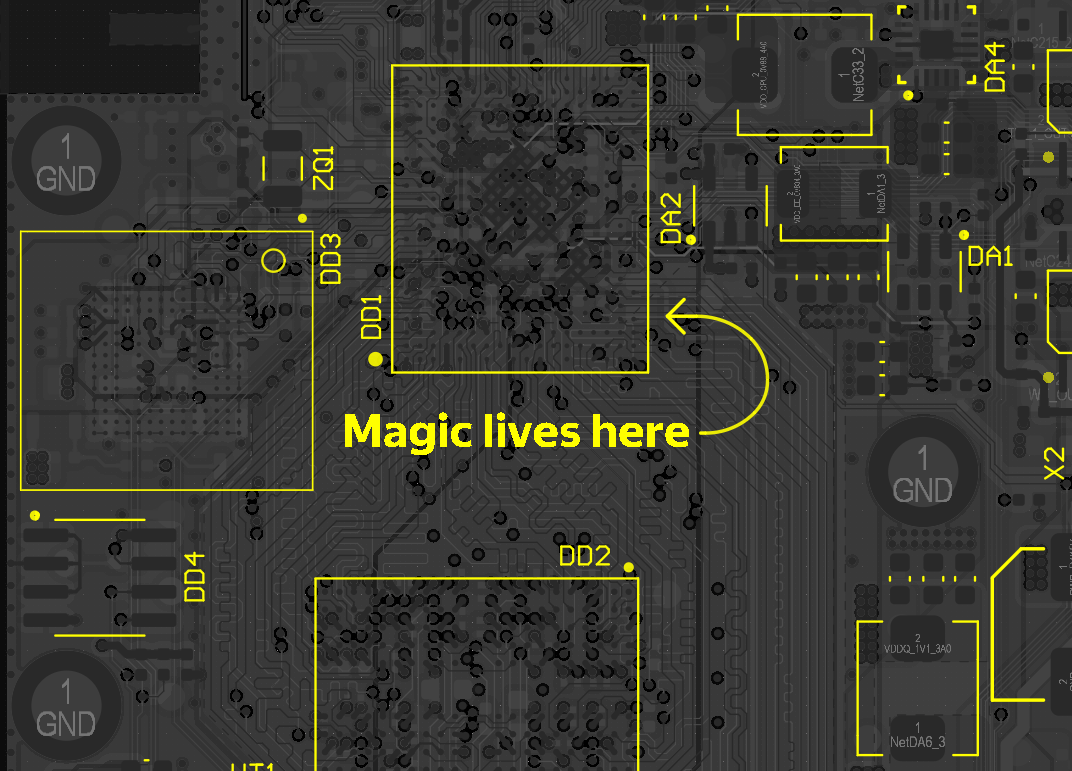

Привет! Это Алексей Фоменко, инженер-электронщик Алисы и умных устройств. Я руковожу группой аппаратной разработки, но время от времени делаю платы и своими руками.

Наши инженеры с огромным трепетом относятся к каждой плате, которую они создают, уделяя внимание мельчайшим деталям. Можно сказать, вкладывают в каждую Станцию частичку себя. Проведя с проектом платы огромное количество часов, хочется оставить какое-то невинное и милое послание прямо от создателя к самому искушённому пользователю. Такие послания ещё называют «пасхалками». И да, они есть и в наших Станциях. Покажу несколько под катом.

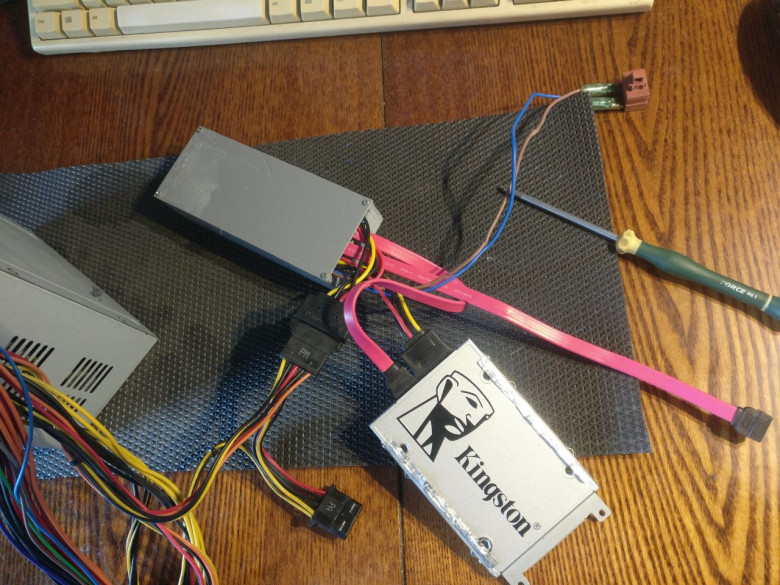

SSD killer — destroyer for your ssd

Привет, меня зовут Ваня, и вот коротенькая история о том, как я придумал и собрал одну штуку, и почему вам нужно срочно отдать мне все свои деньги.

А если серьезно, это устройство для оперативного аппаратного уничтожения данных вместе с носителем. По своей сути это аналог чеховского ружья, у которого цель выстрелить в нужный момент.

На днях узнал, что вышла русскоязычная версия третьего оригинального издания книги «Искусство схемотехники» (статья на Хабре). Новость заинтриговала. Так как достаточно давно увлекаюсь этой книгой и не понаслышке знаю, что отечественные читатели ее очень ждали. Точнее даже, заждались. Авторы оригинальной книги еще в 2015 году сделали рекламу своему произведению, разместив в свободном доступе, на сайте, посвященному книге, предисловие к третьему изданию. Но это не только реклама, но и достаточно детальное описание книги, а также декларация концепций и идей в ней заложенных. Надеюсь, мой скромный любительский перевод не будет воспринят издательством «Бином» в штыки: целей что-либо нарушать у меня нет. Если что, ко мне можно обратиться на почту. Я всегда рад конструктивному диалогу и считаю, что давно сложились условия, когда отечественная версия оригинальной книги просто обязана превзойти оригинал. Кроме того, реклама от самих авторов-корифеев еще никому не вредила.

Я заказал себе «первый том» от «Бинома». Скоро должна книжечка прийти. Я ее внимательно изучу, и по результатам будет рецензия. Надеюсь, книга оправдает мои ожидания. Даже интересно сравнить свои навыки в переводе с профессионалами. А пока, предлагаю приступить к чтению предисловия.

Нет согласующих резисторов в FPGA - что мешает реализовать целый ряд схем, но зато есть чем заменить их для цифрового сигнала внутри таких схем. Пытался найти в сети альтернативу согласующему резистору для применения внутри синтезируемой схемы, поисковик выдал скромный результат поиска, содержанием которого оказалось ничего по существу - категоричное нет на всех форумах, и иногда что-то близкое, но моей задачи не решающее. Да и собственно в схеме развёрнуты две задачи - некоторый кэш нового типа и механизм управления таким кэшем, по сути - часть процессора нового типа.

Тут нужно много вникать. И если Вы не верите IDE Logisim Evolution - можете просто пройти мимо и не принимать тут изложенный материал во что-то нужное и полезное. Тем более что это в общем-то работа новичка, который просто развивает свой проект и взгляды в новых областях, сталкивается с новыми задачами и решает их новыми способами.

(продолжение работы над своим процессором, и в заголовке про физическую память так как везде поисковиком находится про ячейки Excell).

Сначала думал - да ну какая мелочь для процессора, но потом подумал - многие пишут о мелочах и даже получают плюсы, почему не написать о мелочи, если чип создаётся новый.

Сразу говорю, что роль памяти в данной схеме играют SR триггеры предполагаемого FPGA и процедура заполнения любого числа цепи ячеек (или даже одной) выполняется за два рабочих такта проектируемого процессора, независимо от числа выбранных ячеек. Над этой задачкой пришлось немного пломать голову, и нужно было понять что такое управляемый буфер (в данном случае это для Logisim Evolution).

После того, как составил рабочую схему кэша мостов, для работы процессора в режиме без счётчика команд, приступил к схеме управления кэшом мостов. Кэш мостов - это кэш обеспечивающий выполнение команд без счётчика команд, и позволяющий выполнять только команды в обозначенных ячейках памяти. По сути управление кэшем мостов сводится к мгновенному заполнению групп выбранных ячеек. И вот для того чтобы обеспечить бесперебойную работу управляемых буферов в сложной цепи (множество ячеек и множество источников сигнала) пришлось пойти на Хитрость с ИСКЛЮЧАЮЩИМ ИЛИ.

Триггеры группы Last - нижний ряд триггеров на данном изображении, служит для обозначения последнего триггера данной группы для конкретной ячейки, в который запишется единица и заблокирует прохождение сигнала по верхнему проводнику, через который подряд записывается единица в сами эти ячейки памяти механизма управления кэшем мостов - в триггеры группы Memo (незаконченное слово, так как по сути всё это является устройством для управления памятью, а не ей самой).