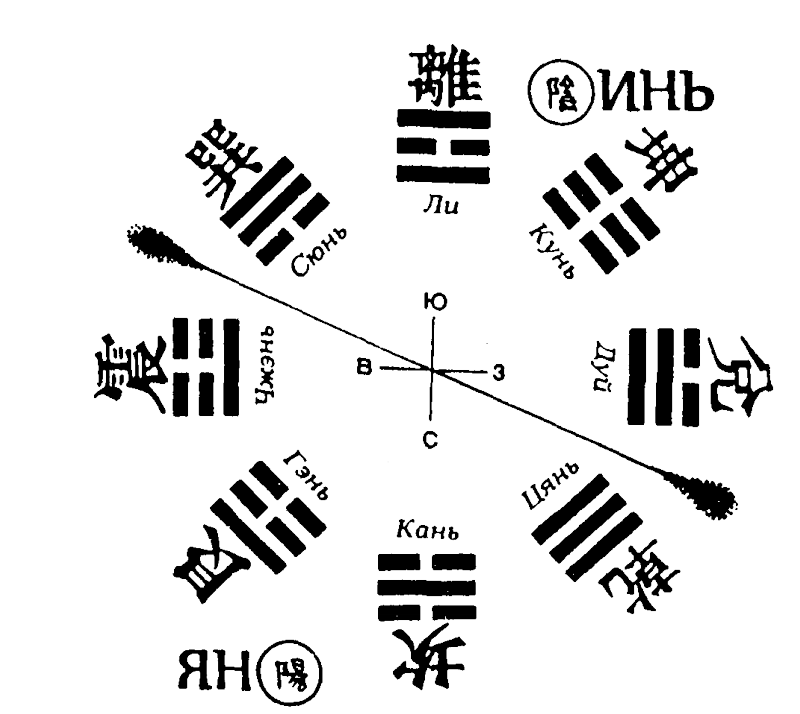

На рисунке изображены схема из 8 возможных триграмм, взятая из книги [1]

Естественные языки могут быть охарактеризованы распределением частот встречаемости своих элементов, таких как слова, отдельные буквы или последовательности букв (N-граммы). Формально N-граммой называется строка из N символов, принадлежащих некоторому алфавиту, состоящему из конечного числа символов. О теоретических и прикладных вопросах применения аппарата N-грамм для автоматической коррекции текста можно прочесть в работе [2].

В данной статье мы будем рассматривать только алфавит, состоящий из букв русского языка, далее мы расскажем о возможностях применения триграмм (последовательностей из трех символов) для постобработки (коррекции с целью уменьшения ошибок) результатов распознавания русскоязычных документов. В качестве механизма распознавания выступали сверточные нейронные сети.

Цифровая обработка изображений — весьма интересная область, но она таит в себе множество подводных камней, на которые постоянно натыкаются новички. Мы активно привлекаем студентов к участию в грантах и проектах, но когда мы пытались давать студентам реальные задания, которые требуют реализации новых алгоритмов обработки изображений, мы были в ужасе от совершаемых ими детских ошибок.

Цифровая обработка изображений — весьма интересная область, но она таит в себе множество подводных камней, на которые постоянно натыкаются новички. Мы активно привлекаем студентов к участию в грантах и проектах, но когда мы пытались давать студентам реальные задания, которые требуют реализации новых алгоритмов обработки изображений, мы были в ужасе от совершаемых ими детских ошибок.