Intel разработала чип 8087 в 1980 году для того, чтобы улучшить производительность ПК с процессорами линеек 8086/8088 (таких, как IBM PC) при выполнении операций с плавающей запятой. Поскольку первые микропроцессоры были предназначены для выполнения операций с целыми числами, выполнение операций с числами с плавающей запятой было медленным, что уже и говорить о выполнение трансцендентных операций, таких как тригонометрические функции или логарифмы. Сопроцессор 8087 значительно повысил скорость выполнения задач с плавающей запятой, все выполнялось почти в 100 раз быстрее. Архитектура 8087 была реализована и в более поздние процессоры Intel, а инструкции 8087 по-прежнему используются в современных x86 ПК. Intel представила в 1980 году чип 8087, предназначенный для улучшения производительности вычислений с плавающей запятой на процессорах 8086 и 8088.

Поскольку ранние микропроцессоры работали только с целыми числами, арифметика с числами с плавающей запятой была медленной, а трансцендентные операции, такие как триггеры или логарифмы, выглядели еще хуже. Добавление математического сопроцессора 8087 в систему позволило ускорить операции с плавающей запятой в 100 раз. Архитектура 8087 стала частью более поздних процессоров Intel, а инструкции 8087 (хотя и устарели) до сих пор являются частью современных настольных компьютеров x86.

Чип 8087 обеспечил быструю арифметику операций с плавающей запятой для оригинального IBM PC и стал частью архитектуры x86, используемой сегодня. Одной из необычных особенностей 8087 является многоуровневое ПЗУ (постоянное запоминающее устройство), способное хранить два бита на транзистор, что вдвое больше плотности обычного ПЗУ. Вместо хранения двоичных данных каждая ячейка в ПЗУ 8087 сохраняла одно из четырех различных значений, которые затем декодировались в два бита. Поскольку 8087 нуждался в большом объеме ПЗУ для микрокода (1), а количество транзисторов на чипе было весьма ограниченно, Intel использовала необычную технологию для решения задачи. В этой статье я объясню, как Intel реализовала этот многоуровневый ROM.

Я вскрыл микросхему 8087 и сфотографировал ее с помощью микроскопа, получив фотографию, представленную ниже. На фото я указал основные функциональные блоки, основываясь моем собственном реверс-инжиниринге (Кликните, чтобы увеличить изображение). Матрица процессора 8087 довольно сложная, с 40 000 транзисторов (2). 8087 использует 80-битные числа с плавающей запятой: 64 бит отведено для мантиссы, 15 бит для экспоненты, и еще знаковый бит. (Пример числа с основанием 10: в числе 6,02 × 1023 6,02 является мантиссой, а 23 — экспонентой). В нижней части фотографии надписью «fraction processing» отмечена часть схемы для мантиссы. Слева направо это включает: хранилище констант, 64-битный сдвиг, 64-битный сумматор / вычитатель, и стек регистров. Чуть выше находится схема для обработки экспоненты.

Чип математического сопроцессора для операций с плавающей запятой Intel 8087, с обозначением основных функциональных блоков

Выполнение инструкции на 8087 требовало нескольких шагов, а в некоторых случаях более 1000. Микропрограмма 8087 использовала микрокод для определения низкоуровневых операций на каждом шаге: сдвиги, инкремент, выборки из памяти, чтение констант и т. д. Вы можете воспринимать микрокод как простую программу, написанную в виде микрокоманд, в которой каждая микрокоманда генерирует управляющие сигналы для различных компонентов чипа. На фотографии выше видно ПЗУ с программой микрокода 8087. ПЗУ занимает большую часть чипа, наглядно показывая, почему компактное многоуровневое ПЗУ было необходимым. Слева от ПЗУ находится «движок», на котором запускалась программа микрокода, по сути, простой процессор.

8087 работал как сопроцессор с процессором 8086. Когда 8086 обнаруживал специальную инструкцию с плавающей запятой, процессор игнорировал ее, и позволил 8087 выполнить инструкцию параллельно. Я не буду подробно объяснять внутреннюю работу 8087, но, если коротко, операции с плавающей запятой были реализованы с использованием целочисленных операций прибавления/вычитания и сдвига. Чтобы сложить или вычесть два числа с плавающей запятой, 8087 выполнял побитовое смещение числа до тех пор, пока двоичные разделители (то есть десятичный разделитель — запятая, но в двоичной системе) не сравняются, а затем прибавлял или вычитал мантиссу. Умножение, деление и квадратный корень выполнялись путем многократных сдвигов, сложений или вычитаний. Трансцендентные операции (tan, arctan, log, power) использовали алгоритмы CORDIC, которые используют сдвиги и добавления специальных констант, обрабатывая по одному биту за раз. 8087 также сталкивался со многими частными случаями: бесконечности, переполнения, NaN (не число), денормализованные числа и несколько режимов округления. Микрокод, сохраненный в ПЗУ, контролировал все эти операции.

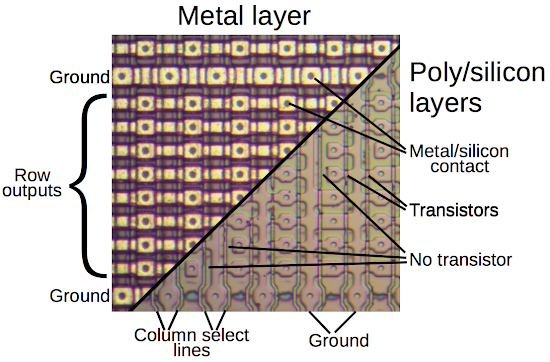

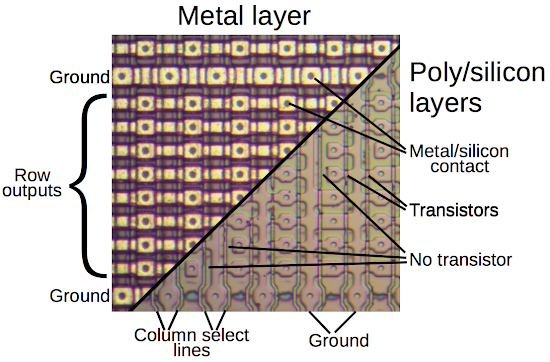

Чип 8087 состоит из крошечной кремниевой матрицы, на которой кремний местами легирован примесями, чтобы получить желаемые полупроводниковые свойства. На кремниевую поверхность нанесен поликремний (особый тип кремния), который формирует провода и транзисторы. И напоследок, металлический слой поверх силикона завершает рабочую электрическую цепь. На фото ниже, с левой стороны показана небольшая часть чипа, как она видна под микроскопом, демонстрируя желтоватую металлическую проводку. На правой части фото металл удален с помощью кислоты, обнажив поликремний и кремний. Когда поликремний пересекает кремний, формируется транзистор. Розовые области — легированный кремний, а тонкие вертикальные линии — поликремний. Маленькие круги — это контакты между слоями кремния и металла, соединяющие их вместе.

Структура ПЗУ в Intel 8087 FPU. Металлический слой показан слева, а поликремний и кремний — справа

Хотя существует много способов построения ПЗУ, стандартный способ состоит в том, чтобы создать сетку «ячеек», где каждая ячейка хранит один бит. Каждая ячейка может иметь транзистор (что означает 0 бит) или не иметь транзистор, что значит 1 бит. На изображении выше вы можете видеть сетку ячеек с транзисторами (где поликремний нанесен на кремний) и отсутствующими транзисторами (где в кремнии есть зазоры). Для считывания информации из ПЗУ активируется одна линия выбора столбца (на основании адреса), чтобы выбрать биты, хранящиеся в этом столбце, и получить на выходе по одному биту из каждой строки. Вы можете видеть вертикальные линии выбора столбца (column select lines) из поликремния, и горизонтальные металлические ряды, на фото выше. Вертикальные линии легированного кремния заземлены.

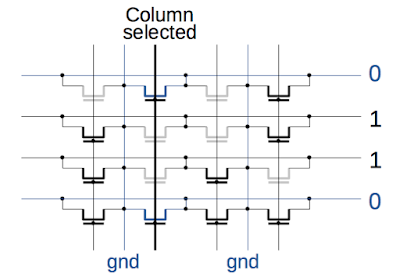

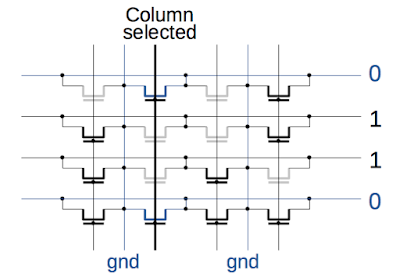

Схема ниже (соответствующая сегменту ПЗУ 4 × 4) объясняет, как функционирует ПЗУ. Каждая ячейка либо имеет транзистор (черный цвет), либо не имеет транзистор (выделен серым цветом). Когда на линию выбора столбца поликремния подается напряжение, транзисторы в этом столбце включаются, и заземляют соответствующие металлические ряды. (в данном случае, транзистор NMOS подобен вентилю, который открыт, если вход равен 0, и закрыт, если вход равен 1.) Металлические «строки» схемы выводят данные, сохраненные в выбранном «столбце».

Схема 4х4 сегмента ПЗУ

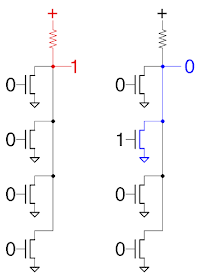

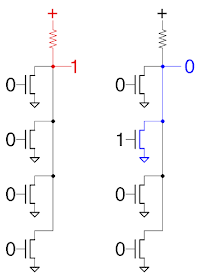

Сигналы выбора столбца генерируются схемой декодера. Так как эта схема построена из вентилей NOR, я сначала объясню конструкцию вентилей. Схема ниже показывает вентиль NOR с четырьмя входами, построенный из четырех транзисторов и подтягивающего резистора (хотя фактически, функцию резистора выполняет специальный транзистор). В левой части схемы все входы равны 0, поэтому все транзисторы отключены, а подтягивающий резистор поддерживает выходной сигнал на «высоком» уровне. В правой части на один из входов подали 1, включив транзистор. Транзистор заземлен, поэтому выходной сигнал теперь «низкого» уровня. Таким образом, если какие-либо входы высоки (1), выход низок (0). Так эта схема реализует вентиль NOR.

4-входной вентиль NOR, построенный из транзисторов NMOS

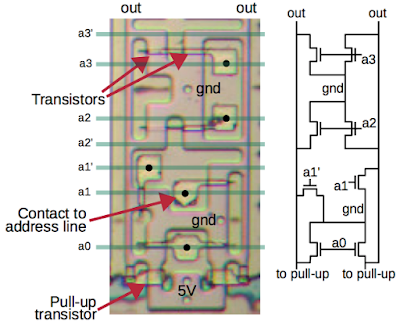

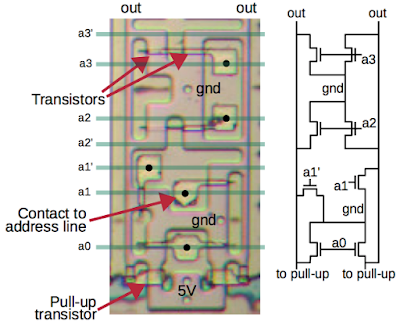

Схема декодера выбора столбца принимает входящие адресные биты и активирует соответствующую строку выбора. Декодер содержит 8-входный вентиль NOR для каждого столбца, то есть один вентиль NOR для каждого адреса. На фотографии показаны два элемента NOR, генерирующие сигналы выбора столбцов (для простоты я покажу только четыре из 8 входов). Каждый столбец использует различную комбинацию адресных строк и дополненных адресных строк в качестве входных данных, выбирая другой адрес. Адресные строки находятся в металлическом слое, который удален на фотографии ниже; адресные линии выделены зеленым цветом. Чтобы определить адрес, связанный со столбцом, посмотрите на квадратные контакты, связанные с каждым транзистором, и отметьте, какие адресные линии подключены. Если все адресные линии, подключенные к транзисторам столбца, находятся на низком (0) уровне, вентиль NOR выберет этот столбец.

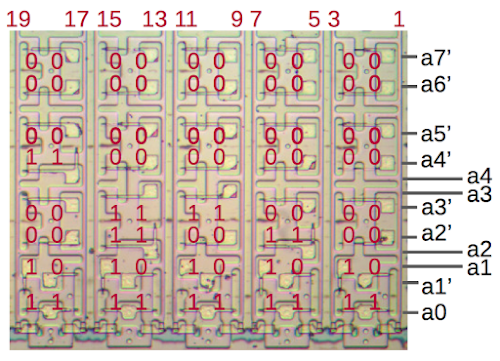

Часть адресного декодера. Декодер адреса выбирает нечетные столбцы в ПЗУ, считая справа налево. Числа в верхней части показывают адрес, связанный с каждым выходом

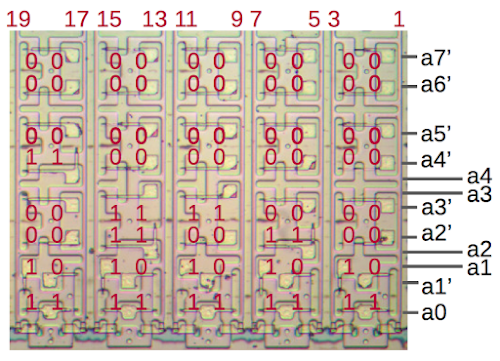

На фото ниже показана небольшая часть декодера ПЗУ со всеми 8 входами для вентилей NOR. Вы можете прочитать двоичные адреса, внимательно изучив соединения в адресной строке. Обратите внимание на двоичный паттерн: соединения a1 меняют значения в каждом столбце, соединения a2 чередуются через каждые два столбца, соединения a3 через каждые четыре столбца и т. Д. Соединение a0 является фиксированным, поскольку эта схема декодера выбирает нечетные столбцы; аналогичная схема ПЗУ выбирает четные адреса (такое разделение было необходимо, чтобы декодер поместился на микросхеме, поскольку каждый столбец декодера в два раза шире ячейки ПЗУ).

Часть адресного декодера для микрокода ПЗУ 8087. Декодер преобразует 8-битный адрес в сигналы выбора столбца

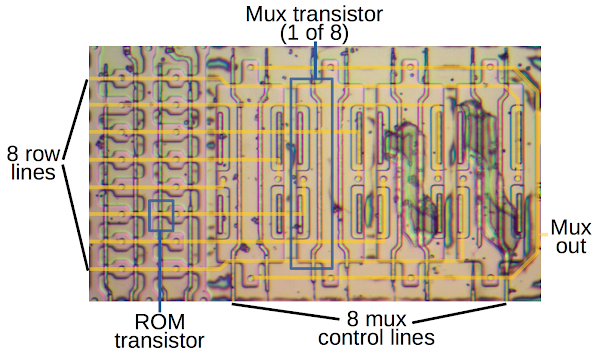

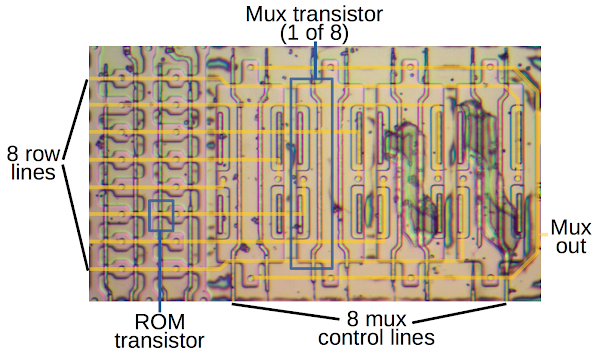

Последний компонент ПЗУ — это набор мультиплексоров, который уменьшает 64 выходных строки до 8 строк. Каждый мультиплексор 8-к-1 выбирает один из своих 8 входов, основываясь на адресе. На приведенной ниже схеме показан один из мультиплексоров строк процессора 8087, построенный из восьми больших проходных транзисторов, каждый из которых подключен к одной из линий «строк». Все транзисторы подключены к выходу поэтому, когда выбранный транзистор включен, он передает свой вход на выход. Транзисторы мультиплексора намного, намного больше, чем транзисторы в ПЗУ, чтобы уменьшить искажение сигнала ПЗУ. Декодер (аналогичный рассмотренному ранее, но меньший) генерирует восемь линий управления мультиплексором из трех адресных линий.

Один из 8-рядных мультиплексоров в ПЗУ. Здесь видны слои (поли)кремния, с металлическими соединениями, нарисованными оранжевым

Подводя итог, ПЗУ хранит биты в сетке. Он использует восемь адресных бит для выбора столбца в сетке. Затем три бита адреса выбирают желаемые восемь выходов из «строк».

До сих пор я объяснял устройство типичного ПЗУ, которое хранит один бит на ячейку. Так как же 8087 смог хранить два бита на ячейку? Если вы посмотрите внимательно, микрокод ПЗУ 8087 содержит четыре разных размера транзисторов — если считать отсутствие транзистора как один из размеров (6). С четырьмя вариантами для каждого транзистора, одна ячейка может кодировать два бита, примерно удваивая плотность (7). Текущий раздел объясняет, как четыре размера транзисторов генерируют четыре разных тока, и как аналоговые и цифровые схемы микросхемы преобразуют эти токи в два бита.

Микрофотография микрокода ПЗУ 8087 показывает четыре разных размера транзисторов. Это позволяет ПЗУ хранить два бита на ячейку

Размер транзистора регулирует ток через транзистор (8). Важным геометрическим фактором является различная ширина кремния (розовый), где он пересекается с поликремнием (вертикальные линии), создавая транзисторы с различной шириной затвора. Поскольку ширина затвора управляет током через транзистор, четыре размера транзистора генерируют четыре различных тока: самый большой транзистор пропускает большую часть тока, и ток вообще не протекает, если транзистора нет.

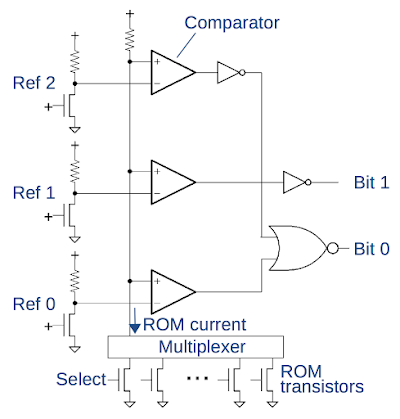

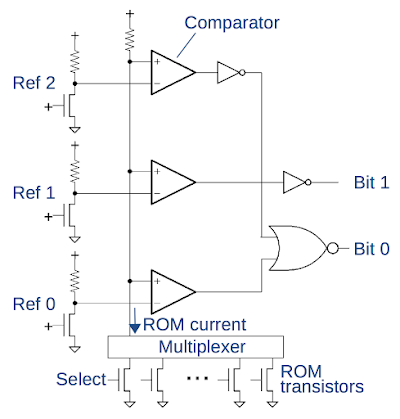

Ток ПЗУ преобразуется в биты за несколько шагов. Сначала подтягивающий резистор преобразует ток в напряжение. Затем три компаратора сравнивают напряжение с опорным напряжением для генерации цифровых сигналов, определяя, какое напряжение выше/ниже. Наконец, логические вентили преобразуют выходные сигналы компаратора в два выходных бита. Эта схема повторяется восемь раз, генерируя в общей сложности 16 битов на выходе.

Схема для чтения двух битов из ячейки ПЗУ

Схема выше выполняет эти шаги преобразования. В итоге, один из транзисторов ПЗУ выбирается линией выбора «столбца» и мультиплексором (обсуждался ранее), генерирующим один из четырех токов. Затем, подтягивающий резистор (12) преобразует ток транзистора в напряжение, в результате чего напряжение зависит от размера выбранного транзистора. Компараторы сравнивают это напряжение с тремя опорными напряжениями, и выводят 1, если напряжение ПЗУ выше, чем опорное напряжение. Компараторы и эталонные напряжения требуют тщательного проектирования, поскольку напряжения ПЗУ могут отличаться всего на 200 мВ.

Опорные напряжения находятся посередине между ожидаемыми значениями напряжения ПЗУ, что допускает некоторые колебания напряжений. «Низкое» напряжение ПЗУ ниже, чем все опорные напряжения, так что все компараторы будет выводить 0. Второе напряжение ПЗУ выше, чем Ref 0, так что нижний компаратор выводит 1. При третьем напряжении ROM, нижние два компаратора выводят 1, а при максимальном напряжении ПЗУ на выходе всех трех компараторов 1. Таким образом, три компаратора выдают четыре различных шаблона вывода в зависимости от транзистора ПЗУ. Затем логические элементы преобразовывают выходные данные компаратора в два выходных бита (10).

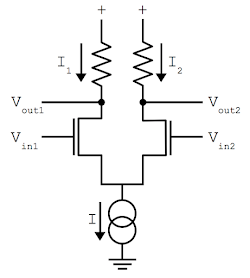

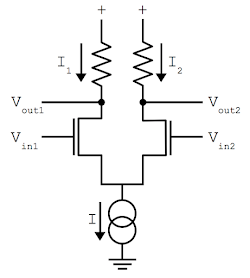

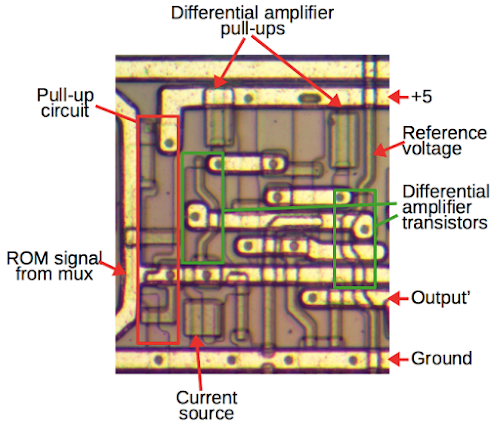

Дизайн компаратора интересен тем, что он является мостом между аналоговым и цифровым мирами, производя 1 или 0, если напряжение ROM, выше или ниже, чем опорное напряжение. Каждый компаратор содержит дифференциальный усилитель, который усиливает разницу между напряжением ПЗУ и опорным напряжением. Выход дифференциального усилителя приводит в действие затвор, который стабилизирует выход и преобразует его в сигнал логического уровня. Дифференциальный усилитель (ниже) представляет собой стандартную аналоговую схему. Источник тока (символ внизу) обеспечивает постоянный ток. Если один из транзисторов имеет более высокое входное напряжение, чем другой, большая часть тока проходит через этот транзистор. Падение напряжения на резисторах приведет к тому, что соответствующий выход станет ниже, а другой выход станет выше.

Диаграмма, показывающая работу дифференциальной пары. Большая часть тока будет проходить через транзистор с более высоким входным напряжением, в результате чего соответствующий выходной сигнал будет ниже. Символ двойного круга внизу — источник постоянного тока I

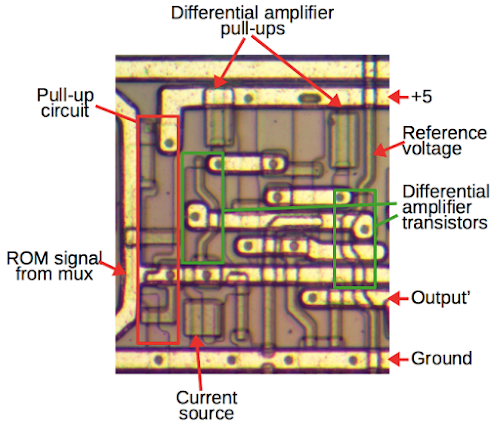

На фото ниже показан один из компараторов на чипе; металлический слой сверху, транзисторы под ним. Я рассмотрю только основные моменты этой сложной схемы; смотрите примечание 12, чтобы узнать детали. Сигнал с ПЗУ и мультиплексора поступает слева. Подтягивающая схема 12 преобразует ток в напряжение. Два больших транзистора дифференциального усилителя сравнивают напряжение ПЗУ с опорным напряжением (вход сверху). Выходы от дифференциального усилителя идут к схеме затвора (разбросаны по фотографии); выход затвора находится в правом нижнем углу. Источник тока дифференциального усилителя и подтягивающие резисторы выполнены из depletion-mode транзисторов. В каждой выходной цепи используются три компаратора, что в сумме дает 24 компаратора.

Один из компараторов в 8087. Чип содержит 24 компаратора для преобразования уровней напряжения из многоуровневого ПЗУ в двоичные данные

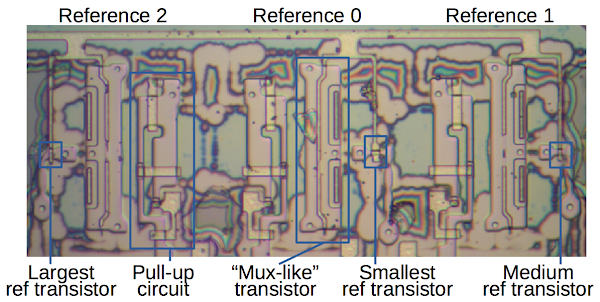

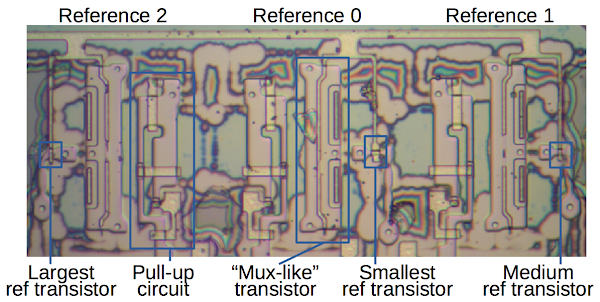

Каждое опорное напряжение генерируется транзистором тщательно подобранного размера и подтягивающим контуром. Цепь опорного напряжения разработана как можно более похожей к сигнальной цепи ПЗУ, так что любые изменения в производстве чипов будут влиять на оба элемента одинаково. Опорное напряжение и сигнал ПЗУ используют один и тот же нагрузочный контур. Кроме того, каждая схема опорного напряжения включает в себя очень большой транзистор, идентичный транзистору мультиплексора, хотя и нет мультиплексирования в цепи опорного сигнала — только, чтобы обеспечить «соответствие» цепей. Три цепи опорного напряжения идентичны, кроме размера опорного транзистора (9).

Схема, генерирующая три опорных напряжения. Размеры опорных транзисторов — между размерами транзисторов ПЗУ. Оксидный слой не был полностью удален с этой части матрицы, из-за чего на фотографии появились цветные завихрения

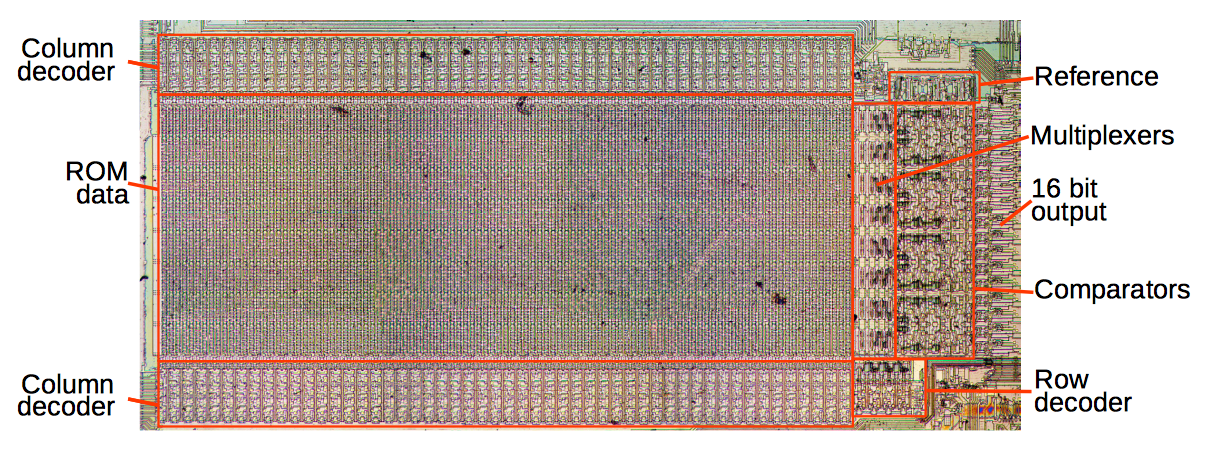

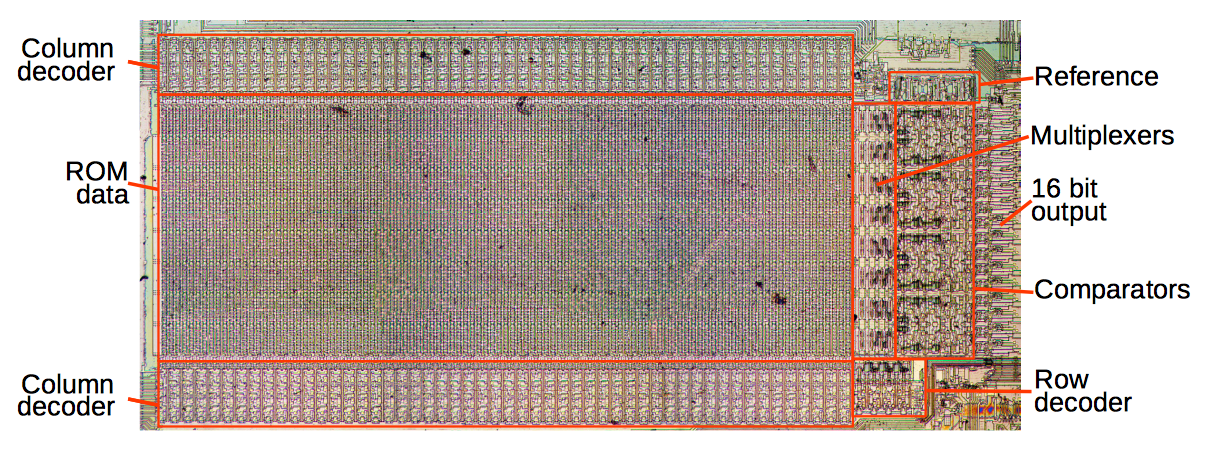

Чтобы собрать весь паззл, на фото ниже показано расположение компонентов ПЗУ микрокода на микросхеме (12). Основную часть схемы ПЗУ составляют транзисторы, хранящие данные. Схема декодера столбца расположена сверху и снизу данных ПЗУ. Половина декодеров выбора столбцов находится сверху, а половина — снизу, для лучшей компоновки. Выходная схема находится справа. Восемь мультиплексоров сокращают 64 строки строк до восьми. Затем восемь строк входят в компараторы, генерируя 16 бит на выходе из ПЗУ справа. Опорная схема над компараторами генерирует три опорных напряжения. Справа внизу небольшой декодер строк управляет мультиплексорами.

Микрокод ПЗУ от Intel 8087 FPU с маркировкой основных компонентов

Хотя изначально может показаться, что многоуровневое ПЗУ будет в два раза меньше обычного ПЗУ, эффект не настолько заметен из-за дополнительной схемы компараторов, и из-за того, что сами транзисторы немного больше, из-за необходимости использовать несколько размеров. Несмотря на это, многоуровневое ПЗУ сэкономило около 40% пространства, которое заняло бы обычное ПЗУ.

Теперь, когда я понял структуру ПЗУ, я могу просто (но утомительно) прочитать содержимое ПЗУ, просто глядя на размеры каждого транзистора под микроскопом. Но, не зная набора инструкций микрокода, содержимое ПЗУ бесполезно.

Математический сопроцессор для операций с плавающей запятой 8087 использовал необычную структуру «два бита на ячейку» для размещения микрокода на чипе. Intel повторно использовала многоуровневую структуру ПЗУ в 1981 году в обреченной системе iAPX 432.11 Насколько я могу судить, интерес к ПЗУ с многоуровневыми ячейками достиг своего пика в 1980-х годах и затем угас. Вероятно, из-за того, что, по закону Мура, намного легче увеличить емкость ПЗУ за счет сокращения стандартной ячейки, чем проектированием нестандартных ПЗУ, требующих специальных аналоговых схем, построенных с высокими допусками (14).

Удивительно, но многоуровневая концепция недавно вернулась, но уже на флэш-память. Многие флэш-устройств хранят два или более битов на ячейку (13). Флэш-память даже достигла замечательных 4 битов на ячейку (требуя 16 различных уровней напряжения) в потребительских продуктах, анонсированных недавно (QLC, quad-level cell). Таким образом, малоизвестные технологии 1980-х годов могут вернутся снова, спустя десятилетия.

Я сообщаю о своих последних постах в блоге в Твиттере, так что подписывайтесь на @kenshirriff для чтения будущих статей о 8087. У меня также есть RSS-канал. Спасибо Джеффу Эплеру за предложение исследовать ПЗУ 8087.

Спасибо, что остаетесь с нами. Вам нравятся наши статьи? Хотите видеть больше интересных материалов? Поддержите нас оформив заказ или порекомендовав знакомым, 30% скидка для пользователей Хабра на уникальный аналог entry-level серверов, который был придуман нами для Вас: Вся правда о VPS (KVM) E5-2650 v4 (6 Cores) 10GB DDR4 240GB SSD 1Gbps от $20 или как правильно делить сервер? (доступны варианты с RAID1 и RAID10, до 24 ядер и до 40GB DDR4).

VPS (KVM) E5-2650 v4 (6 Cores) 10GB DDR4 240GB SSD 1Gbps до 1 января бесплатно при оплате на срок от полугода, заказать можно тут.

Dell R730xd в 2 раза дешевле? Только у нас 2 х Intel Dodeca-Core Xeon E5-2650v4 128GB DDR4 6x480GB SSD 1Gbps 100 ТВ от $249 в Нидерландах и США! Читайте о том Как построить инфраструктуру корп. класса c применением серверов Dell R730xd Е5-2650 v4 стоимостью 9000 евро за копейки?

Поскольку ранние микропроцессоры работали только с целыми числами, арифметика с числами с плавающей запятой была медленной, а трансцендентные операции, такие как триггеры или логарифмы, выглядели еще хуже. Добавление математического сопроцессора 8087 в систему позволило ускорить операции с плавающей запятой в 100 раз. Архитектура 8087 стала частью более поздних процессоров Intel, а инструкции 8087 (хотя и устарели) до сих пор являются частью современных настольных компьютеров x86.

Чип 8087 обеспечил быструю арифметику операций с плавающей запятой для оригинального IBM PC и стал частью архитектуры x86, используемой сегодня. Одной из необычных особенностей 8087 является многоуровневое ПЗУ (постоянное запоминающее устройство), способное хранить два бита на транзистор, что вдвое больше плотности обычного ПЗУ. Вместо хранения двоичных данных каждая ячейка в ПЗУ 8087 сохраняла одно из четырех различных значений, которые затем декодировались в два бита. Поскольку 8087 нуждался в большом объеме ПЗУ для микрокода (1), а количество транзисторов на чипе было весьма ограниченно, Intel использовала необычную технологию для решения задачи. В этой статье я объясню, как Intel реализовала этот многоуровневый ROM.

Я вскрыл микросхему 8087 и сфотографировал ее с помощью микроскопа, получив фотографию, представленную ниже. На фото я указал основные функциональные блоки, основываясь моем собственном реверс-инжиниринге (Кликните, чтобы увеличить изображение). Матрица процессора 8087 довольно сложная, с 40 000 транзисторов (2). 8087 использует 80-битные числа с плавающей запятой: 64 бит отведено для мантиссы, 15 бит для экспоненты, и еще знаковый бит. (Пример числа с основанием 10: в числе 6,02 × 1023 6,02 является мантиссой, а 23 — экспонентой). В нижней части фотографии надписью «fraction processing» отмечена часть схемы для мантиссы. Слева направо это включает: хранилище констант, 64-битный сдвиг, 64-битный сумматор / вычитатель, и стек регистров. Чуть выше находится схема для обработки экспоненты.

Чип математического сопроцессора для операций с плавающей запятой Intel 8087, с обозначением основных функциональных блоков

Выполнение инструкции на 8087 требовало нескольких шагов, а в некоторых случаях более 1000. Микропрограмма 8087 использовала микрокод для определения низкоуровневых операций на каждом шаге: сдвиги, инкремент, выборки из памяти, чтение констант и т. д. Вы можете воспринимать микрокод как простую программу, написанную в виде микрокоманд, в которой каждая микрокоманда генерирует управляющие сигналы для различных компонентов чипа. На фотографии выше видно ПЗУ с программой микрокода 8087. ПЗУ занимает большую часть чипа, наглядно показывая, почему компактное многоуровневое ПЗУ было необходимым. Слева от ПЗУ находится «движок», на котором запускалась программа микрокода, по сути, простой процессор.

8087 работал как сопроцессор с процессором 8086. Когда 8086 обнаруживал специальную инструкцию с плавающей запятой, процессор игнорировал ее, и позволил 8087 выполнить инструкцию параллельно. Я не буду подробно объяснять внутреннюю работу 8087, но, если коротко, операции с плавающей запятой были реализованы с использованием целочисленных операций прибавления/вычитания и сдвига. Чтобы сложить или вычесть два числа с плавающей запятой, 8087 выполнял побитовое смещение числа до тех пор, пока двоичные разделители (то есть десятичный разделитель — запятая, но в двоичной системе) не сравняются, а затем прибавлял или вычитал мантиссу. Умножение, деление и квадратный корень выполнялись путем многократных сдвигов, сложений или вычитаний. Трансцендентные операции (tan, arctan, log, power) использовали алгоритмы CORDIC, которые используют сдвиги и добавления специальных констант, обрабатывая по одному биту за раз. 8087 также сталкивался со многими частными случаями: бесконечности, переполнения, NaN (не число), денормализованные числа и несколько режимов округления. Микрокод, сохраненный в ПЗУ, контролировал все эти операции.

Реализация ПЗУ

Чип 8087 состоит из крошечной кремниевой матрицы, на которой кремний местами легирован примесями, чтобы получить желаемые полупроводниковые свойства. На кремниевую поверхность нанесен поликремний (особый тип кремния), который формирует провода и транзисторы. И напоследок, металлический слой поверх силикона завершает рабочую электрическую цепь. На фото ниже, с левой стороны показана небольшая часть чипа, как она видна под микроскопом, демонстрируя желтоватую металлическую проводку. На правой части фото металл удален с помощью кислоты, обнажив поликремний и кремний. Когда поликремний пересекает кремний, формируется транзистор. Розовые области — легированный кремний, а тонкие вертикальные линии — поликремний. Маленькие круги — это контакты между слоями кремния и металла, соединяющие их вместе.

Структура ПЗУ в Intel 8087 FPU. Металлический слой показан слева, а поликремний и кремний — справа

Хотя существует много способов построения ПЗУ, стандартный способ состоит в том, чтобы создать сетку «ячеек», где каждая ячейка хранит один бит. Каждая ячейка может иметь транзистор (что означает 0 бит) или не иметь транзистор, что значит 1 бит. На изображении выше вы можете видеть сетку ячеек с транзисторами (где поликремний нанесен на кремний) и отсутствующими транзисторами (где в кремнии есть зазоры). Для считывания информации из ПЗУ активируется одна линия выбора столбца (на основании адреса), чтобы выбрать биты, хранящиеся в этом столбце, и получить на выходе по одному биту из каждой строки. Вы можете видеть вертикальные линии выбора столбца (column select lines) из поликремния, и горизонтальные металлические ряды, на фото выше. Вертикальные линии легированного кремния заземлены.

Схема ниже (соответствующая сегменту ПЗУ 4 × 4) объясняет, как функционирует ПЗУ. Каждая ячейка либо имеет транзистор (черный цвет), либо не имеет транзистор (выделен серым цветом). Когда на линию выбора столбца поликремния подается напряжение, транзисторы в этом столбце включаются, и заземляют соответствующие металлические ряды. (в данном случае, транзистор NMOS подобен вентилю, который открыт, если вход равен 0, и закрыт, если вход равен 1.) Металлические «строки» схемы выводят данные, сохраненные в выбранном «столбце».

Схема 4х4 сегмента ПЗУ

Сигналы выбора столбца генерируются схемой декодера. Так как эта схема построена из вентилей NOR, я сначала объясню конструкцию вентилей. Схема ниже показывает вентиль NOR с четырьмя входами, построенный из четырех транзисторов и подтягивающего резистора (хотя фактически, функцию резистора выполняет специальный транзистор). В левой части схемы все входы равны 0, поэтому все транзисторы отключены, а подтягивающий резистор поддерживает выходной сигнал на «высоком» уровне. В правой части на один из входов подали 1, включив транзистор. Транзистор заземлен, поэтому выходной сигнал теперь «низкого» уровня. Таким образом, если какие-либо входы высоки (1), выход низок (0). Так эта схема реализует вентиль NOR.

4-входной вентиль NOR, построенный из транзисторов NMOS

Схема декодера выбора столбца принимает входящие адресные биты и активирует соответствующую строку выбора. Декодер содержит 8-входный вентиль NOR для каждого столбца, то есть один вентиль NOR для каждого адреса. На фотографии показаны два элемента NOR, генерирующие сигналы выбора столбцов (для простоты я покажу только четыре из 8 входов). Каждый столбец использует различную комбинацию адресных строк и дополненных адресных строк в качестве входных данных, выбирая другой адрес. Адресные строки находятся в металлическом слое, который удален на фотографии ниже; адресные линии выделены зеленым цветом. Чтобы определить адрес, связанный со столбцом, посмотрите на квадратные контакты, связанные с каждым транзистором, и отметьте, какие адресные линии подключены. Если все адресные линии, подключенные к транзисторам столбца, находятся на низком (0) уровне, вентиль NOR выберет этот столбец.

Часть адресного декодера. Декодер адреса выбирает нечетные столбцы в ПЗУ, считая справа налево. Числа в верхней части показывают адрес, связанный с каждым выходом

На фото ниже показана небольшая часть декодера ПЗУ со всеми 8 входами для вентилей NOR. Вы можете прочитать двоичные адреса, внимательно изучив соединения в адресной строке. Обратите внимание на двоичный паттерн: соединения a1 меняют значения в каждом столбце, соединения a2 чередуются через каждые два столбца, соединения a3 через каждые четыре столбца и т. Д. Соединение a0 является фиксированным, поскольку эта схема декодера выбирает нечетные столбцы; аналогичная схема ПЗУ выбирает четные адреса (такое разделение было необходимо, чтобы декодер поместился на микросхеме, поскольку каждый столбец декодера в два раза шире ячейки ПЗУ).

Часть адресного декодера для микрокода ПЗУ 8087. Декодер преобразует 8-битный адрес в сигналы выбора столбца

Последний компонент ПЗУ — это набор мультиплексоров, который уменьшает 64 выходных строки до 8 строк. Каждый мультиплексор 8-к-1 выбирает один из своих 8 входов, основываясь на адресе. На приведенной ниже схеме показан один из мультиплексоров строк процессора 8087, построенный из восьми больших проходных транзисторов, каждый из которых подключен к одной из линий «строк». Все транзисторы подключены к выходу поэтому, когда выбранный транзистор включен, он передает свой вход на выход. Транзисторы мультиплексора намного, намного больше, чем транзисторы в ПЗУ, чтобы уменьшить искажение сигнала ПЗУ. Декодер (аналогичный рассмотренному ранее, но меньший) генерирует восемь линий управления мультиплексором из трех адресных линий.

Один из 8-рядных мультиплексоров в ПЗУ. Здесь видны слои (поли)кремния, с металлическими соединениями, нарисованными оранжевым

Подводя итог, ПЗУ хранит биты в сетке. Он использует восемь адресных бит для выбора столбца в сетке. Затем три бита адреса выбирают желаемые восемь выходов из «строк».

Многоуровневое ПЗУ

До сих пор я объяснял устройство типичного ПЗУ, которое хранит один бит на ячейку. Так как же 8087 смог хранить два бита на ячейку? Если вы посмотрите внимательно, микрокод ПЗУ 8087 содержит четыре разных размера транзисторов — если считать отсутствие транзистора как один из размеров (6). С четырьмя вариантами для каждого транзистора, одна ячейка может кодировать два бита, примерно удваивая плотность (7). Текущий раздел объясняет, как четыре размера транзисторов генерируют четыре разных тока, и как аналоговые и цифровые схемы микросхемы преобразуют эти токи в два бита.

Микрофотография микрокода ПЗУ 8087 показывает четыре разных размера транзисторов. Это позволяет ПЗУ хранить два бита на ячейку

Размер транзистора регулирует ток через транзистор (8). Важным геометрическим фактором является различная ширина кремния (розовый), где он пересекается с поликремнием (вертикальные линии), создавая транзисторы с различной шириной затвора. Поскольку ширина затвора управляет током через транзистор, четыре размера транзистора генерируют четыре различных тока: самый большой транзистор пропускает большую часть тока, и ток вообще не протекает, если транзистора нет.

Ток ПЗУ преобразуется в биты за несколько шагов. Сначала подтягивающий резистор преобразует ток в напряжение. Затем три компаратора сравнивают напряжение с опорным напряжением для генерации цифровых сигналов, определяя, какое напряжение выше/ниже. Наконец, логические вентили преобразуют выходные сигналы компаратора в два выходных бита. Эта схема повторяется восемь раз, генерируя в общей сложности 16 битов на выходе.

Схема для чтения двух битов из ячейки ПЗУ

Схема выше выполняет эти шаги преобразования. В итоге, один из транзисторов ПЗУ выбирается линией выбора «столбца» и мультиплексором (обсуждался ранее), генерирующим один из четырех токов. Затем, подтягивающий резистор (12) преобразует ток транзистора в напряжение, в результате чего напряжение зависит от размера выбранного транзистора. Компараторы сравнивают это напряжение с тремя опорными напряжениями, и выводят 1, если напряжение ПЗУ выше, чем опорное напряжение. Компараторы и эталонные напряжения требуют тщательного проектирования, поскольку напряжения ПЗУ могут отличаться всего на 200 мВ.

Опорные напряжения находятся посередине между ожидаемыми значениями напряжения ПЗУ, что допускает некоторые колебания напряжений. «Низкое» напряжение ПЗУ ниже, чем все опорные напряжения, так что все компараторы будет выводить 0. Второе напряжение ПЗУ выше, чем Ref 0, так что нижний компаратор выводит 1. При третьем напряжении ROM, нижние два компаратора выводят 1, а при максимальном напряжении ПЗУ на выходе всех трех компараторов 1. Таким образом, три компаратора выдают четыре различных шаблона вывода в зависимости от транзистора ПЗУ. Затем логические элементы преобразовывают выходные данные компаратора в два выходных бита (10).

Дизайн компаратора интересен тем, что он является мостом между аналоговым и цифровым мирами, производя 1 или 0, если напряжение ROM, выше или ниже, чем опорное напряжение. Каждый компаратор содержит дифференциальный усилитель, который усиливает разницу между напряжением ПЗУ и опорным напряжением. Выход дифференциального усилителя приводит в действие затвор, который стабилизирует выход и преобразует его в сигнал логического уровня. Дифференциальный усилитель (ниже) представляет собой стандартную аналоговую схему. Источник тока (символ внизу) обеспечивает постоянный ток. Если один из транзисторов имеет более высокое входное напряжение, чем другой, большая часть тока проходит через этот транзистор. Падение напряжения на резисторах приведет к тому, что соответствующий выход станет ниже, а другой выход станет выше.

Диаграмма, показывающая работу дифференциальной пары. Большая часть тока будет проходить через транзистор с более высоким входным напряжением, в результате чего соответствующий выходной сигнал будет ниже. Символ двойного круга внизу — источник постоянного тока I

На фото ниже показан один из компараторов на чипе; металлический слой сверху, транзисторы под ним. Я рассмотрю только основные моменты этой сложной схемы; смотрите примечание 12, чтобы узнать детали. Сигнал с ПЗУ и мультиплексора поступает слева. Подтягивающая схема 12 преобразует ток в напряжение. Два больших транзистора дифференциального усилителя сравнивают напряжение ПЗУ с опорным напряжением (вход сверху). Выходы от дифференциального усилителя идут к схеме затвора (разбросаны по фотографии); выход затвора находится в правом нижнем углу. Источник тока дифференциального усилителя и подтягивающие резисторы выполнены из depletion-mode транзисторов. В каждой выходной цепи используются три компаратора, что в сумме дает 24 компаратора.

Один из компараторов в 8087. Чип содержит 24 компаратора для преобразования уровней напряжения из многоуровневого ПЗУ в двоичные данные

Каждое опорное напряжение генерируется транзистором тщательно подобранного размера и подтягивающим контуром. Цепь опорного напряжения разработана как можно более похожей к сигнальной цепи ПЗУ, так что любые изменения в производстве чипов будут влиять на оба элемента одинаково. Опорное напряжение и сигнал ПЗУ используют один и тот же нагрузочный контур. Кроме того, каждая схема опорного напряжения включает в себя очень большой транзистор, идентичный транзистору мультиплексора, хотя и нет мультиплексирования в цепи опорного сигнала — только, чтобы обеспечить «соответствие» цепей. Три цепи опорного напряжения идентичны, кроме размера опорного транзистора (9).

Схема, генерирующая три опорных напряжения. Размеры опорных транзисторов — между размерами транзисторов ПЗУ. Оксидный слой не был полностью удален с этой части матрицы, из-за чего на фотографии появились цветные завихрения

Чтобы собрать весь паззл, на фото ниже показано расположение компонентов ПЗУ микрокода на микросхеме (12). Основную часть схемы ПЗУ составляют транзисторы, хранящие данные. Схема декодера столбца расположена сверху и снизу данных ПЗУ. Половина декодеров выбора столбцов находится сверху, а половина — снизу, для лучшей компоновки. Выходная схема находится справа. Восемь мультиплексоров сокращают 64 строки строк до восьми. Затем восемь строк входят в компараторы, генерируя 16 бит на выходе из ПЗУ справа. Опорная схема над компараторами генерирует три опорных напряжения. Справа внизу небольшой декодер строк управляет мультиплексорами.

Микрокод ПЗУ от Intel 8087 FPU с маркировкой основных компонентов

Хотя изначально может показаться, что многоуровневое ПЗУ будет в два раза меньше обычного ПЗУ, эффект не настолько заметен из-за дополнительной схемы компараторов, и из-за того, что сами транзисторы немного больше, из-за необходимости использовать несколько размеров. Несмотря на это, многоуровневое ПЗУ сэкономило около 40% пространства, которое заняло бы обычное ПЗУ.

Теперь, когда я понял структуру ПЗУ, я могу просто (но утомительно) прочитать содержимое ПЗУ, просто глядя на размеры каждого транзистора под микроскопом. Но, не зная набора инструкций микрокода, содержимое ПЗУ бесполезно.

Выводы

Математический сопроцессор для операций с плавающей запятой 8087 использовал необычную структуру «два бита на ячейку» для размещения микрокода на чипе. Intel повторно использовала многоуровневую структуру ПЗУ в 1981 году в обреченной системе iAPX 432.11 Насколько я могу судить, интерес к ПЗУ с многоуровневыми ячейками достиг своего пика в 1980-х годах и затем угас. Вероятно, из-за того, что, по закону Мура, намного легче увеличить емкость ПЗУ за счет сокращения стандартной ячейки, чем проектированием нестандартных ПЗУ, требующих специальных аналоговых схем, построенных с высокими допусками (14).

Удивительно, но многоуровневая концепция недавно вернулась, но уже на флэш-память. Многие флэш-устройств хранят два или более битов на ячейку (13). Флэш-память даже достигла замечательных 4 битов на ячейку (требуя 16 различных уровней напряжения) в потребительских продуктах, анонсированных недавно (QLC, quad-level cell). Таким образом, малоизвестные технологии 1980-х годов могут вернутся снова, спустя десятилетия.

Я сообщаю о своих последних постах в блоге в Твиттере, так что подписывайтесь на @kenshirriff для чтения будущих статей о 8087. У меня также есть RSS-канал. Спасибо Джеффу Эплеру за предложение исследовать ПЗУ 8087.

Примечания и ссылки

- Процессор 8087 содержит 1648 слов микрокода (если я правильно посчитал), с 16 битами в каждом слове, всего 26368 битов. Размер ПЗУ не обязан быть степенью двойки, и Intel может построить его любого требуемого размера.

- Источники предоставляют противоречивые значения о количестве транзисторов в 8087: Intel заявляет, что 40 000 транзисторов, а Википедия утверждает, что 45 000. Расхождение может быть связано с разными способами подсчета транзисторов. В частности, поскольку количество транзисторов в ПЗУ, PLA или аналогичной структуре зависит от данных, хранящихся в нем, источники часто считают «потенциальные» транзисторы, а не количество физических транзисторов. Другие расхождения могут быть связаны с тем, учитываются ли подтягивающие транзисторы и считаются ли сильноточные драйверы несколькими параллельными или одним большим транзистором.

- Взаимодействие между процессором 8086 и сопроцессором для операций с плавающей запятой 8087 довольно сложно; Я объясню некоторые основные моменты. Упрощенное представление состоит в том, что 8087 наблюдает за потоком команд 8086 и выполняет любые инструкции, которые являются инструкциями 8087. Сложность состоит в том, что 8086 имеет буфер предварительной выборки команд, поэтому выбранная команда не значит исполняемая. Таким образом, 8087 дублирует буфер предварительной выборки 8086 (или меньший буфер предварительной выборки 8088), поэтому он знает, что делает 8086. Еще одним препятствием являются сложные режимы адресации, используемые 8086, которые используют регистры внутри процессора. 8087 не может выполнять эти режимы адресации, поскольку у него нет доступа к регистрам 8086. Вместо этого, когда 8086 видит инструкцию 8087, он делает выборку из памяти по указанному адресу, и игнорирует результат. Между тем, 8087 захватывает адрес с шины, чтобы он мог использовать его, если адрес ему нужен. Если 8087 отсутствует, вы можете ожидать неполадки в работе, но это не происходит. Вместо этого для системы без 8087 компоновщик переписывает инструкции 8087, заменяя их подпрограммными вызовами в библиотеку эмуляции.

- Причина, по которой ПЗУ обычно используют мультиплексоры на выходах строк, заключается в том, что неэффективно создавать ПЗУ с большим количеством столбцов и несколькими выходными битами, поскольку схема декодера будет больше, чем данные ПЗУ. Решение состоит в том, чтобы изменить форму ROM, чтобы сохранить те же биты, но с большим количеством строк и меньшим количеством столбцов. Например, ПЗУ может иметь в 8 раз больше строк и 1/8 столбцов, что позволяет использовать декодер 1/8 размера. Кроме того, длинное, узкое ПЗУ (например, 1 К × 16) неудобно размещать на чипе, поскольку оно не подходит в качестве простого блока. Тем не менее, «змеиный» дизайн тоже может быть использован. Например, ранние образцы памяти от Intel были сдвиговыми регистрами; 1405 содержал 512 бит в одном длинном сдвиговом регистре. Чтобы установить это на чип, сдвиговый регистр укладывался «змеёй» взад-вперед около 20 раз.

- Некоторые компьютеры IBM использовали необычную технику хранения для хранения микрокода: в картах Майлара были пробиты отверстия (точно так же, как в обычных перфокартах), и компьютер емкостно обнаруживал отверстия (link). Некоторые компьютеры, такие как Xerox Alto, имели некоторый микрокод в оперативной памяти. Это позволяло программам модифицировать микрокод, создавая новые инструкции для своих конкретных целей. Многие современные процессоры имеют записываемый микрокод, поэтому патчи могут исправлять ошибки в микрокоде.

- Я не замечал четырех размеров транзисторов в ПЗУ микрокода, пока не увидел в комментарии к Hacker News упоминание, что 8087 использовал технологию двух бит на ячейку. Я был настроен скептически, но после более внимательного изучения чипа я понял, что комментарий был верен.

- Несколько других подходов были использованы в 1980-х годах для хранения нескольких бит на ячейку. Mostek и другие компании использовали одну из самых распространенных: легированные транзисторы в ПЗУ имели разные пороговые напряжения. Используя четыре различных пороговых напряжения, можно хранить два бита на ячейку. По сравнению с геометрическим подходом Intel, пороговый подход обеспечивал большую плотность (поскольку все транзисторы могли быть минимального размера), но требовал большего количества слоев и этапов обработки для создания многоуровневой имплантации. Этот подход использовал новую (в то время) технологию ионной имплантации для тщательной настройки уровней легирования каждого транзистора. Самым большое влияние ионной имплантации на интегральные схемы было ее использование для создания истощающих транзисторов (транзисторов с отрицательным пороговым напряжением), которые работали намного лучше, чем подтягивающие резисторы в логических элементах. Ионная имплантация также использовалась в микропроцессоре Z-80 для создания некоторых транзисторных «ловушек», схем, которые выглядели под микроскопом как обычные транзисторы, но получали импланты, которые делали их нефункциональными. Это послужило защитой от копирования, поскольку производитель, который пытался производить клоны процессора Z-80 путем копирования чипа с помощью микроскопа, в конечном итоге получал чип, который некорректно работал разными способами, некоторые из них было трудно выявить.

- Ток через транзистор пропорционален соотношению между шириной и длиной затвора. (Длина — это расстояние между истоком и стоком.) Транзисторы ПЗУ (и все, кроме наименьшего эталонного транзистора) поддерживают постоянную длину и изменяют ширину, поэтому уменьшение ширины уменьшает ток. Для уравнений MOSFET см. Wikipedia

- Затвор наименьшего опорного транзистора скорее длинным чем узким, благодаря свойствам МОП-транзисторов. Проблема заключается в том, что опорные транзисторы должны иметь размеры между размерами ПЗУ транзисторов. В частности, для Reference 0 необходим транзистор меньшего размера, чем самый маленький транзистор ПЗУ. Но самый маленький ПЗУ транзистор уже настолько мал, насколько это возможно, следуя технологии изготовления. Заметьте: чтобы решить эту проблему, поликремний, пересекающий средний эталонный транзистор, гораздо толще по горизонтали. Поскольку свойства МОП-транзистора определяются отношением ширины к высоте его затвора, расширение поликремния так же хорошо действует, как и сжатие кремния, чтобы заставить транзистор работать с меньшим током.

- Логика ПЗУ декодирует размер транзистора в битах следующим образом: Нет транзистора = 00, малый транзистор = 01, средний транзистор = 11, большой транзистор = 10. Такое упорядочение битов позволяет сэкономить несколько элементов в логике декодирования; Так как отображение от транзистора к битам является произвольным, не имеет значения, что последовательность идет не по порядку. (См. «Two Bits Per Cell ROM», Stark).

- Интерфейсный процессор Intel iAPX 43203 (1981) использовал многоуровневое ПЗУ, очень похожее на чип 8087. Подробности можно узнать в «The interface processor for the Intel VLSI 432 32 bit computer,» J. Bayliss et al., IEEE J. Solid-State Circuits, vol. SC-16, стр. 522-530, октябрь 1981 г. Интерфейсный процессор 43203 обеспечивал поддержку ввода-вывода для процессора iAPX 432. Intel начала проект iAPX 432 в 1975 году, чтобы создать «микромейнфрейм», который станет революционным процессором Intel для 1980-х годов. Когда в проекте iAPX 432 возникли задержки, Intel выпустила процессор 8086 в качестве временного решения, в 1978 году. Хотя Intel 8086 имел огромный успех, приведя к настольным ПК и современной архитектуре x86, проект iAPX 432 закончился неудачей в 1986 году.

- Схема ниже (из «Multiple-Valued ROM Output Circuits») содержит подробную информацию о схеме чтения ПЗУ. Концептуально в ПЗУ используется подтягивающий резистор для преобразования тока транзистора в напряжение. Схема фактически использует трехтранзисторную схему (T3, T4, T5) в качестве подтягивания. Т4 и Т5 по существу являются инвертором, обеспечивающим отрицательную обратную связь через Т3, что делает схему менее чувствительной к возмущениям (таким как производственные отклонения). Компаратор состоит из простого дифференциального усилителя (желтого цвета) с T6, действующим в качестве источника тока. Выход дифференциального усилителя преобразуется в устойчивый сигнал логического уровня с помощью затвора (зеленый).

- Флэш-память подразделяется на SLC (одн single level cell — один бит на ячейку), MLC (multi level cell — два бита на ячейку), TLC (triple level cell — три бита на ячейку) и QLC (quad level cell — четыре бита на ячейку). Зачастую, флэш-память с большим количеством битов на ячейку дешевле, но менее надежна, медленнее и быстрее изнашивается из-за меньших разниц сигналов.

- В журнале «Electronics» была опубликована короткая статья «Four-State Cell Doubles ROM Bit Capacity» (стр. 39, 9 октябрь 1980 г.), описывающая методику Intel, но эта статья неясна и вводит в заблуждение. Intel опубликовала подробную статью «Два бита на ПЗУ ячейки» в COMPCON (стр. 209-212, февраль 1981 г.). Внешняя группа попыталась провести обратный инжиниринг более подробных спецификаций схем Intel в «Multiple-valued ROM output circuits» (Proc. 14th Int. Symp. Multivalue Logic, 1984). Две статьи, описывающие память с использованием подобной технологии, — « A Survey of Multivalued Memories» («IEEE Transactions on Computers», февраль 1986 г., с. 99–106) и «A review of multiple-valued memory technology» (IEEE Symposium on Multivalued Logic, 1998).

Спасибо, что остаетесь с нами. Вам нравятся наши статьи? Хотите видеть больше интересных материалов? Поддержите нас оформив заказ или порекомендовав знакомым, 30% скидка для пользователей Хабра на уникальный аналог entry-level серверов, который был придуман нами для Вас: Вся правда о VPS (KVM) E5-2650 v4 (6 Cores) 10GB DDR4 240GB SSD 1Gbps от $20 или как правильно делить сервер? (доступны варианты с RAID1 и RAID10, до 24 ядер и до 40GB DDR4).

VPS (KVM) E5-2650 v4 (6 Cores) 10GB DDR4 240GB SSD 1Gbps до 1 января бесплатно при оплате на срок от полугода, заказать можно тут.

Dell R730xd в 2 раза дешевле? Только у нас 2 х Intel Dodeca-Core Xeon E5-2650v4 128GB DDR4 6x480GB SSD 1Gbps 100 ТВ от $249 в Нидерландах и США! Читайте о том Как построить инфраструктуру корп. класса c применением серверов Dell R730xd Е5-2650 v4 стоимостью 9000 евро за копейки?