Автор: iwaniwaniwan012

На этой статье мы заканчиваем серию статей, посвященных симуляции высокоскоростных приёмопередатчиков различных поколений ПЛИС Intel/Altera.

Симуляция высокоскоростных приёмопередатчиков с динамической реконфигурацией для ПЛИС Intel серии V.

Введение

В этой статье мы подошли к самому "свежему" поколению ПЛИС фирмы Intel, а именно 10 поколение. И теперь мы будем создавать проект в среде симуляции для Arria 10.

Напомню, что высокоскоростные приёмопередатчики - это пара RX и TX, встроенные в ПЛИС, которые позволяют преобразовать параллельную шину данных на низкой частоте в последовательную на высокой при передаче данных и из последовательной в параллельную при получении данных. Они необходимы для реализации различных протоколов передачи данных. А динамическая реконфигурация в данном случае необходима для "автосогласования" скорости работы интерфейсов, например 1 / 2,5 /10 Gb Ethernet.

В ПЛИС Arria 10 схема проекта, который мы будем создавать, следующая:

В ПЛИС Intel серии 10 для использование приёмопередатчиков необходимо использовать IP ядро Transceiver Native Phy и Transceiver ATX PLL

В предыдущих поколениях схема отличается, но все различия мы опишем в конце статьи, нужно же как-то подвести итоги, или сразу дать информацию, если кто-то из читателей не захочет читать предыдущие статьи =)

Описание схемы

Transceiver Native PHY - IP ядро, необходимое для обеспечения приёма и передачи данных для

Transceiver PHY Reconfiguration Controller - модуль, обеспечивающий динамическую реконфигурацию, встроенный в IP ядро Transceiver Native PHY

Transceiver ATX PLL - IP ядро, необходимое для формирования высокой частоты для передачи последовательных данных

Transceiver ATX PLL Reconfiguration Controller - модуль, обеспечивающий динамическую реконфигурацию, встроенный в IP ядро Transceiver ATX PLL

Transceiver PHY Reset - IP ядро, необходимое для правильного сброса аппаратной и программной части высокоскоростных приёмопередатчиков, используемых в IP ядре Transceiver Native PHY и Transceiver ATX PLL

PRBS9 Generator/Checker -модуль, генерирующий/проверяющий ПСП с полиномом

Пользовательская логика - модуль, который по запросу отправляющий команды для изменения скоростных характеристик с использованием динамической реконфигурацией

Приступим к нашему основному инструменту Quartus, но в этом случае будем использовать Intel Quartus Standart Edition 20.1, так как в Lite Edition нет поддержки Arria 10. Quartus Standart Edition требует лицензию, но мы выберем пробный период без возможности компиляции проекта, но мы же не собираемся работать в этом случае в железе. Думаю, что хватит уже вводных слов, пора переходить к делу.

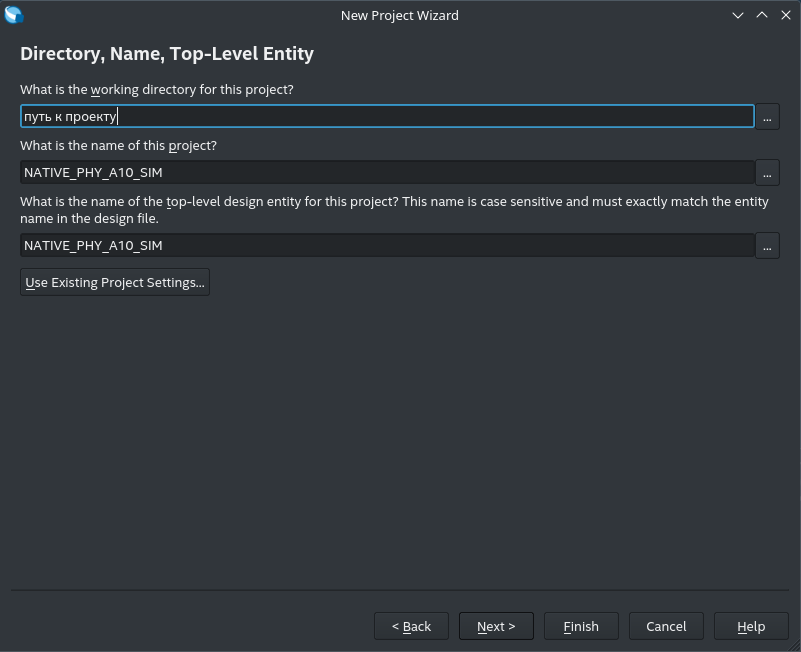

Создание проекта

В Quartus Standart Edition начнём создание нового проекта:

Здесь мы выбираем путь, по которому будет создан проект и его название

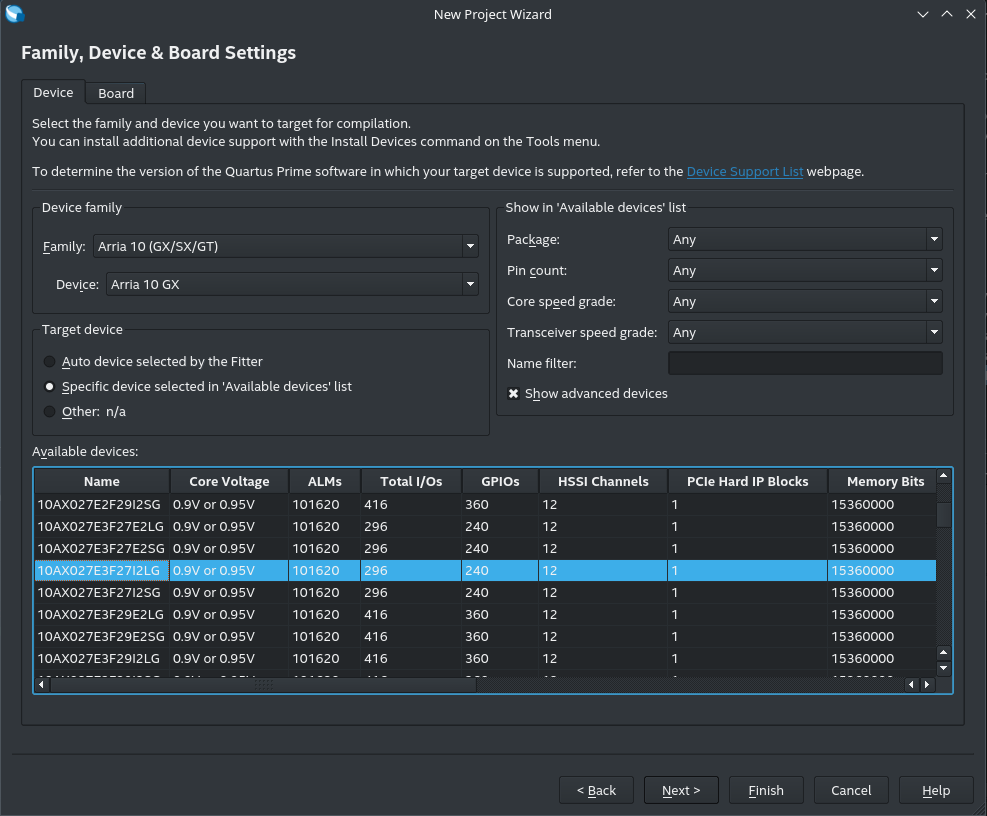

Выберем ПЛИС Arria 10 GX, далее особо не важно, ну пусть будет 10AX027E3F27I2LG и нажмём финиш. Проект откроется и сразу переходим в IP Catalog. В нём создадим Transceiver Native PHY Intel Arria 10 FPGA IP

Нам откроется Platform Designer со следующим окном:

В этом окне необходимо настроить:

Transceiver configuration rules - PCS Direct, это значит, что не будем использовать дополнительные возможности, такие как кодек например

PMA configuration rules - basic

Transceiver mode - TX/RX Duplex

Number of data channels - 1, количество каналов

Data Rate - 1250 mbps, скоростные характеристики

Enable simplified data interface - значит, что мы не будем менять на лету параметры, связанные с изменением шины параллельных данных

Спускаемся ниже и там видим следующие настройки, касающиеся TX PMA

Здесь менять ничего не будем. Но нам важна информация о том, что для функционирования TX Channel необходимо подать на вход IP ядра частоту 625 MHz (Serial Clock).

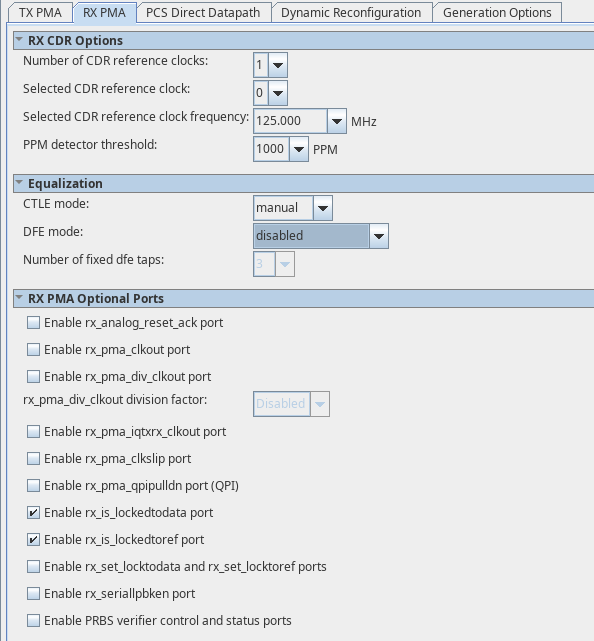

Переходим на следующую вкладку RX PMA

В RX Channel нам необходимо выбрать:

Selected CDR reference clock frequency - выбор опорной частоты, на базе которой будет функционировать CDR (Clock Data Recovery)

Enable rx_is_lockedtodata port - сигнал, который говорит о том, что RX заблокирован на базе входных данных

Enable rx_is_lockedtoref port - сигнал, который говорит о том, что RX заблокирован на базе опорной частоты

Следующая по очереди вкладка PCS Direct Datapath:

Здесь всего одна настройка - выбор шины данных, выберем 20 бит и переходим к вкладке Dynamic Reconfiguration:

И тут мы подошли к самому интересному и важному:

Enable Dynamic Reconfiguration - включаем динамическую реконфигурацию

Enable multiple reconfiguration profiles - включаем поддержку нескольких профилей, хранящиеся во встроенном реконфигураторе

Enable embedded reconfiguration streamer - включаем встроенный модуль, который при запросе сам изменит необходимые параметры

Generate reduced reconfiguration files - сгенерировать в настройках только различающиеся параметры

Number of reconfiguration profiles - количество используемых профилей

Selected reconfiguration profile - выбор профиля, который необходимо загрузить/сохранить

Далее делаем следующие шаги:

Выбираем Selected reconfiguration profile 0

Нажимаем Store configuration to selected profile

Изменяем скорость 2500 mbps

Выбираем Selected reconfiguration profile 1

Нажимаем Store configuration to selected profile

Готово

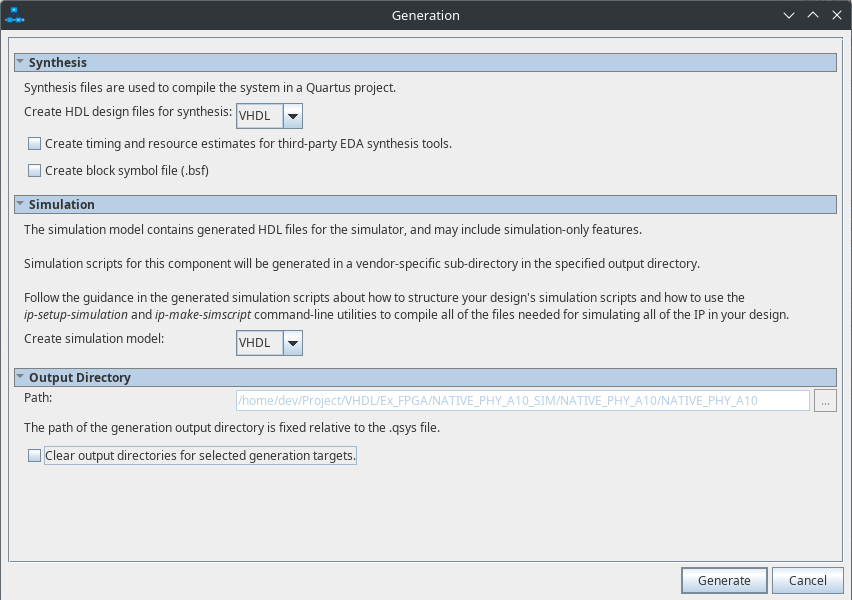

Нажимаем Finish и видим следующее окно:

Выбираем везде VHDL, и нажимаем Generate, на этом создание IP ядра закончено

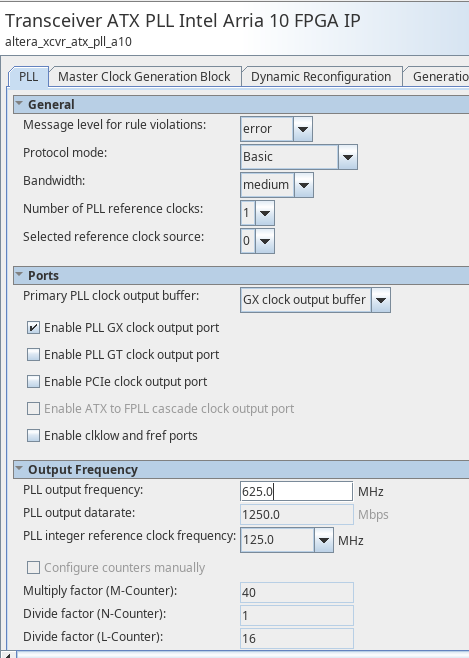

Следующее IP ядро - Transceiver ATX PLL Intel Arria 10 FPGA IP, создаем его и видим следующее окно:

Выбираем основные параметры:

PLL output frequency - 625 MHz, частота, необходимая для TX Channel

PLL integer reference clock frequency - 125 MHz, опорная частота для генерирования частоты, необходимой для стабильной работы PLL

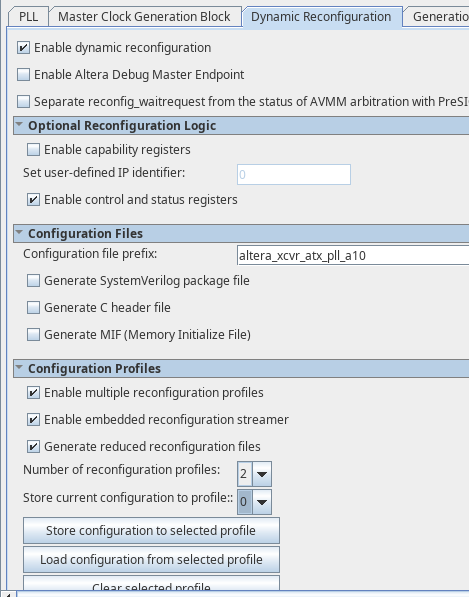

После этого переходим к вкладке Dynamic Reconfiguration

Она схожа с аналогичной вкладкой в IP ядра Transceiver Native PHY, поэтому нет смысла повторяться, главное, что нам необходимо:

Выбрать профиль 0

Сохранить частоту 625 MHz

Выбрать профиль 1

Сохранить частоту 1250 MHz

Готово, нажимаем Finish и видим следующее окно:

В нем выбираем VHDL, нажимаем Generate, и очередное IP ядро у нас готово, осталось только одно, а именно Transceiver PHY Reset Controller.

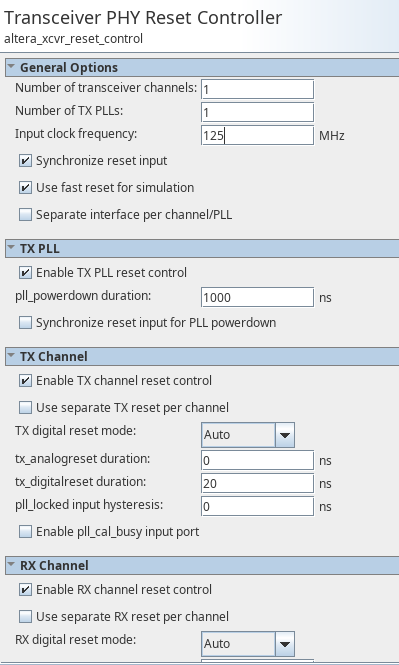

Выбираем его в IP Catalog и видим его настройки

И снова необходимо описать некоторые параметры, которые нам необходимы:

Input clock frequency - опорная частота, на базе которой IP ядро будет функционировать

Use fast reset for simulation - использовать короткий алгоритм сброса в среде симуляции

Enable TX Channel reset control - использовать данное IP ядро для сброса TX Channel

Enable RX Channel reset control - использовать данное IP ядро для сброса RX Channel

Заканчиваем с этим ядром, выбираем язык VHDL и жмём Generate, и... На этом создания IP ядер закончено.

Всё, теперь можно закрывать Quartus =)

Описание логики перестройки ATX PLL и Native PHY

Начиная с 10 поколения ПЛИС разработчики фирмы Intel для удобства разработчиков, использующих данные ПЛИС в своих проектах, в описанные IP ядра стали встраивать Embedded streamer, то есть всё то, что мы делали ранее в предыдущих статьях теперь можно запустить парой команд с использованием шины Avalon MM (Memory Mapped).

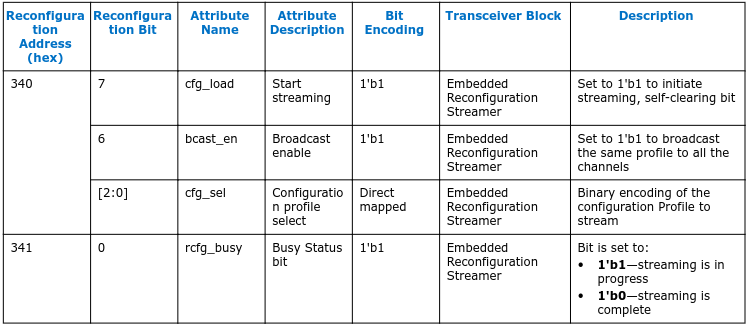

Ниже представлено адресное пространство как для Embedded Streamer IP ядра Native PHY так и для ATX PLL:

Алгоритм взаимодействия следующий:

По адресу 0x340 записать в 8-ой бит единицу, в биты [2:0] - номер профиля, который необходимо загрузить

По адресу 0x341 читаем данные

Если в данных, которые мы запросили на 2 шаге нулевой бит равен '0', то перестройка закончена, если нет - то возвращаемся на шаг 2.

Всё, тут магия довольно простая =)

Симуляция

Для сборки всего проекта был написан скрипт на языке TCL, который:

Собирает все необходимые библиотеки, которые необходимы для симуляции IP ядер

Собирает все необходимые библиотеки из файлов, которые были сгенерированы Quartus

Собирает все модули, разработанные самостоятельно, включая основной файл TestBench

Добавляет все необходимые сигналы для визуализации (waveform)

Запускает симуляцию

Листинг можно посмотреть в папке scripts, файл называет setup.tcl (ссылка на листинг и исходники проекта в конце статьи).

Есть пару основных моментов, на которые стоит обратить внимание.

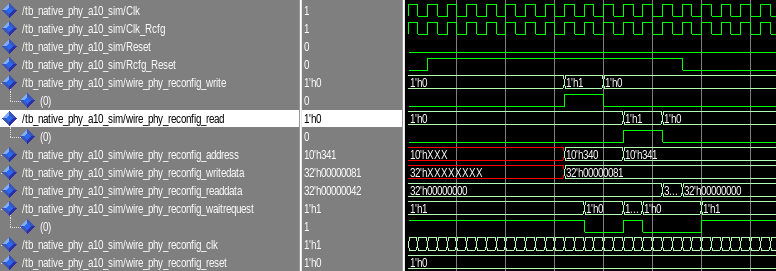

Взаимодействие с IP ядром Transceiver Native PHY через шину Avalon MM

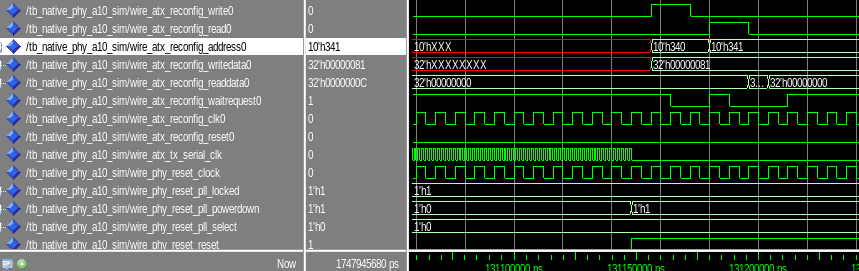

Взаимодействие с IP ядром Transceiver ATX PLL через шину Avalon MM

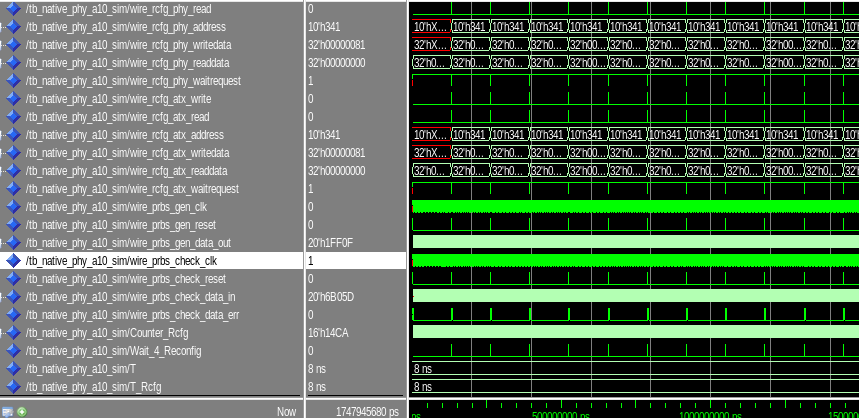

Визуализация проверки данных ПСП

Данные ПСП принимаются без ошибок после каждой перестройки.

Итог

Результат нашей работы - проект в для среды симуляции ModelSim, схема работы которого мы представили в начале статьи.

Исходные коды всего проекта доступны в github по ссылке.

Кстати, если не хочется проводить симуляцию, но хочется посмотреть сам результат, то в git так же доступен файл wlf, в котором записаны все необходимые сигналы.

Раз мы заканчиваем серию статей, то хочется сделать небольшой обзор, скажем так, эволюцию динамической реконфигурации IV, V, 10 поколений ПЛИС Intel.

Поколение ПЛИС | RX/TX Channel | TX PLL | RX/TX Reconfig | TX PLL Reconfig |

IV | ALTGX | Встроенная в ALTGX | Отдельное IP ядро (управляется MIF) | Отдельное IP ядро (управляется MIF) |

V | Native PHY | Встроенная в Native PHY | Отдельное IP ядро (управляется AvMM и MIF) | Совмещённое с RX/TX Reconfig (управляется AvMM и MIF) |

10 | Native PHY | ATX PLL | Встроенное в Native PHY | Встроенное в ATX PLL |

Теперь точно всё, спасибо за внимание!

P.S. Как обычно вопросы и комментарии приветствуются =)