Comments 41

Интересно что не добавили к сравнению конкурентов :)

Речь идёт про сравнение только Интелов между собой, в виду того что они, наконец-то, вырвались на новый техпроцесс. С конкурентами сравним в следующий раз. И так много текста :-) Тем более я лично жду ответа от Красных.

3700x ,32gb ram,1080ti, gentoo geekbench5:

https://browser.geekbench.com/v5/cpu/11727958

Что более любопытно:

https://browser.geekbench.com/v5/cpu/compare/11598285?baseline=11727958

У 12900k geekbench показывает частоту 6.4

Смысл в малых ядрах очень даже есть, вопрос в том, сможет ли диспетчер задач адекватно распределить нагрузку. Например, сможет ли он понять, что задаче не нужен большой кеш и быстрый FPU ? Вот тут вопрос.

добавив поддержку новой DDR5, Intel сохранили поддержку предыдущей — DDR4. Такое «синие» последний раз делали в процессорах Core2Duo, а точнее в чипсетах при переходе с DDR2 на DDR3 — тогда ещё контроллер оперативной памяти был в северном мосту. При переходе с DDR3 на DDR4 (4, 5 и 6 поколения соответственно) такого счастья не было

Вообще-то было: наверное все процы 1151/1151v2, а также некоторые Haswell-E поддерживают и DDR4 и DDr3.

Пожалуйста, больше подробностей и примеров. Я вот попытался вспомнить, но не смог.

Применение и технологии

Большая часть материнских плат с этим разъёмом обычно поддерживает два канала оперативной памяти стандарта DDR4 (до двух планок памяти на канал). Существуют платы с поддержкой памяти DDR3(L). На некоторых платах имеются слоты как для DDR4, так и для DDR3(L), но может быть установлен только один тип памяти. Материнские платы с чипсетами серии 300 поддерживают только память DDR4 (исключение H310C).

Поддержка DDR3

Intel официально заявляет, что интегрированные контроллеры памяти (IMC) Skylake и Kaby Lake поддерживают модули памяти DDR3L только с напряжением 1,35 В, а DDR4 с напряжением 1,2 В, что привело к предположению, что более высокие напряжения модулей DDR3 могут повредить или разрушить IMC и процессор. В то же время ASRock, Gigabyte и Asus гарантируют, что их материнские платы для Skylake и Kaby Lake со слотами DDR3 поддерживают модули DDR3 с напряжением 1,5 и 1,65 В.

В трёхсотой серии чипсетов DDR3 поддерживается только специально выпущенным для Китая чипсетом H310C.

Ga h170hd3 ddr3. 6-7 поколение (Скайлейк/Кэби Лейк) поддерживали ддр3 вместе с ддр4. Сам сидел на 2с/2т пне g4500 и ддр3-памятью. Затем на 7700ес на той же плате и той же ддр3.

Неожидано да. Благодарю. Добавлю в текст.

LGA 2011-v3.

Ряд процессоров имеет поддержку DDR3 и DDR4 (Xeon E5 2678 v3 и ряд других). Huananzhi X99-TF как пример "актуальной" материнки имеющей оба набора слотов. Есть и DDR3 only

причём если найти ddr3 с поддержкой 2133МГц, то она будет быстрее, за счёт более низких таймингов. самое смешное, что на сайте ark.intel.com этих процессоров нет и массово о них узнали только ~2,5 годаназад, когда их выкинули на вторичку, а китайцы стали делать под них материнки.

а вообще материнки под разную память, но одинаковый сокет были ещё со времён FPM/EDO.

Интересно, что же ответит АМД. По любому они держат козырь в рукаве

Полагаю, с учётом того что им есть куда ещё расти в плане TPD по сравнению с новыми корами, они просто накинуть 2-4 ядра и оптимизацию ядра на те же 19%. И не надо будет заморачиваться пока с гибридной архитектурой. Как говорил Ави мистору Тони "Пуля-в-зубах" из одного известного художественного фильма: "Не очень деликатно, но очень эффективно" :-)

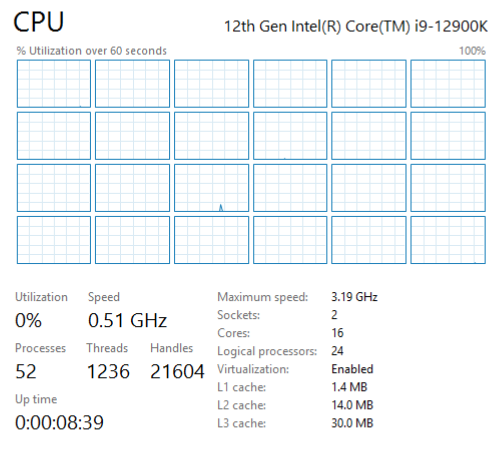

То что не попало в статью, но, на мой взгляд, интересно. Windows Server 2019 с обновлениями на день начала официальных продаж i9-12900K. Sockets: 2.

Sockets: 2.

lscpu в Linux выглядит так:

processor : 0

vendor_id : GenuineIntel

cpu family : 6

model : 151

model name : 12th Gen Intel(R) Core(TM) i9-12900K

stepping : 2

microcode : 0x12

cpu MHz : 3200.000

cache size : 30720 KB

physical id : 0

siblings : 24

core id : 0

cpu cores : 16

apicid : 0

initial apicid : 0

fpu : yes

fpu_exception : yes

cpuid level : 32

wp : yes

flags : fpu vme de pse tsc msr pae mce cx8 apic sep mtrr pge mca cmov pat pse36 clflush dts acpi mmx fxsr sse sse2 ss ht tm pbe syscall nx pdpe1gb rdtscp lm constant_tsc art arch_perfmon pebs bts rep_good nopl xtopology nonstop_tsc cpuid aperfmperf tsc_known_freq pni pclmulqdq dtes64 monitor ds_cpl vmx smx est tm2 ssse3 sdbg fma cx16 xtpr pdcm pcid sse4_1 sse4_2 x2apic movbe popcnt tsc_deadline_timer aes xsave avx f16c rdrand lahf_lm abm 3dnowprefetch cpuid_fault epb cat_l2 invpcid_single cdp_l2 ssbd ibrs ibpb stibp ibrs_enhanced tpr_shadow vnmi flexpriority ept vpid ept_ad fsgsbase tsc_adjust bmi1 avx2 smep bmi2 erms invpcid rdt_a rdseed adx smap clflushopt clwb intel_pt sha_ni xsaveopt xsavec xgetbv1 xsaves split_lock_detect avx_vnni dtherm ida arat pln pts hwp hwp_notify hwp_act_window hwp_epp hwp_pkg_req umip pku ospke waitpkg gfni vaes vpclmulqdq tme rdpid movdiri movdir64b fsrm md_clear serialize pconfig arch_lbr flush_l1d arch_capabilities

vmx flags : vnmi preemption_timer posted_intr invvpid ept_x_only ept_ad ept_1gb flexpriority apicv tsc_offset vtpr mtf vapic ept vpid unrestricted_guest vapic_reg vid ple shadow_vmcs ept_mode_based_exec tsc_scaling usr_wait_pause

bugs : spectre_v1 spectre_v2 spec_store_bypass swapgs

bogomips : 6374.40

clflush size : 64

cache_alignment : 64

address sizes : 46 bits physical, 48 bits virtual

power management:Уважаемый автор, спасибо за проделанную работу. Просьба, если сводите данные в таблицы, не затруднитесь указать единицы измерения, уж так принято в нашем несовершенном мире.

Большие ядра, как и раньше, имеют полный «фарш»: HT, поддержку аппаратной виртуализации, набор инструкций AVX512 и пр.

Ох и намучаются разработчики ещё с этой гибридной архитектурой! Помню, как у нас на андроиде приложение падало от того, что при запуске находились нужные инструкции в проце, приложение стартовало и включало нужные функции, а потом ОС его вытесняла на другие ядра, где этих инструкций нет.

По идее, ОС должна перехватить исключение и перекинуть задачу на нужно ядро. Ведь именно ОС решает, а не программа, на каких ядрах она будет работать.

Понятное дело, что именно ОС решает. Но никаких перехватов в Андроиде не было (пару лет назад), и приложение просто падало с ошибкой, что мол нет таких инструкций.

Некорректная инструкция — это прерывание, выполнение программы останавливается, а управление передаётся в ОС. Пока ОС обрабатывает прерывание, программа в принципе не может упасть. Она падает, когда ОС сообщает программе о возникшей ситуации, например, отправляет соответствующий сигнал, и возвращает ей управление.

Скореев всего, всё дело в том, что детальная обработка исключения с разбором инструкции — довольно сложная задача, на которую разработчики ОС просто забили.

«Препарируем» Intel Core i9-12900k: 10 нанометров, гибридная архитектура и новая память