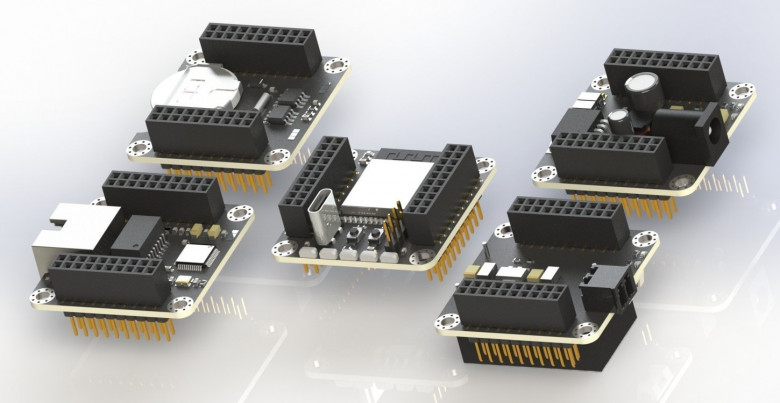

LoRa Module (P2P Private Protocol) Parameters

If you are using a LoRa module for point-to-point (P2P) communication or building your own private protocol, understanding and correctly configuring each parameter is the key to successful communication.

After reading this article, you will learn:

• How Should the LoRa Over-the-Air (PHY) Modulation and Packet Format Parameters Be Configured, and Why?

• The meaning of RF front-end parameters and how to tune them

• Chip-level control parameters: operating modes, clocks, power supply, calibration, and more

• A quick-reference "must-match" table and a list of common issues

Note: This article covers only LoRa (P2P/Private Protocol) parameters. If you need information on LoRaWAN protocol-layer parameters (e.g., ADR, DevEUI, join procedures), please refer to "LoRaWAN Protocol Layer Parameters".

Before starting configuration, verify that your device has selected PacketType = LoRa. The LR2021 supports multiple modulation types—including LoRa, LR-FHSS, FLRC, FSK/GFSK, OQPSK, and OOK. When using P2P LoRa communication, you must first switch to LoRa mode; all subsequent modulation and packet structure commands will then be interpreted in LoRa mode.

If you select the wrong PacketType (e.g., FLRC or GFSK mode), the chip will not interpret the SF, BW, and CR parameters in LoRa mode, The result is that the transmitted data cannot be decoded by the receiving end at all.