Комментарии 8

А откуда брать этот *.ppd файл с задержками? Это общепринятый формат? Насколько мне известно, производители предоставляют IBIS модель, откуда можно путём несложных расчётом получить величины задержек. Почему бы тогда не сделать импорт IBIS?

Это необязательно *.ppd можно и txt. Данные файлы можно найти на сайтах производителя микросхемы, либо вычислить опытным путём через моделирование, например используя средства HyperLynx

Сделал небольшие правки, касаемо импорта и структуры файлов:

Формат файлов PinPkgDelays/PinPkgLengths (*.txt/.*ppd/*.ppl) следующий:

Где unit — формат величины (от регистра не зависит):

part_name — ключевое слово, уникально идентифицирующее вашу микросхему

pin_number, value — здесь указывается номер вывода и соответствующее ему значение длины/задержки

Важно: инструмент импорта не поддерживает формат запятых, даже если у вас в CES они определены как разделители разрядов.

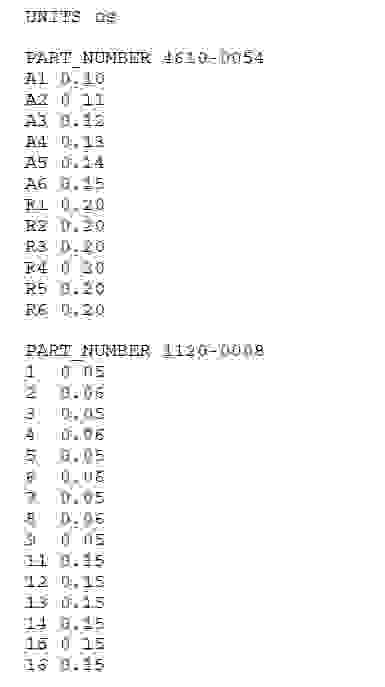

Небольшой пример файла PinPkgDelays.txt:

Формат файлов PinPkgDelays/PinPkgLengths (*.txt/.*ppd/*.ppl) следующий:

Где unit — формат величины (от регистра не зависит):

- для задержки — секунды(s), миллисекунды (ms), микросекунды (us), наносекунды (ns) и пикосекунды (ps)

- для длины — тысячные дюйма (th), микроны (um), миллиметры (mm), дюймы (in)

part_name — ключевое слово, уникально идентифицирующее вашу микросхему

pin_number, value — здесь указывается номер вывода и соответствующее ему значение длины/задержки

Важно: инструмент импорта не поддерживает формат запятых, даже если у вас в CES они определены как разделители разрядов.

Небольшой пример файла PinPkgDelays.txt:

В дополнении к вопросу о том где брать файлы с задержками, если их нет в документации на микросхему:

1) Касаемо Xilinx, можно cгенерировать файл c задержками в формате .csv через Vivado, для этого откройте проект вашей ПЛИС, RTL или netlist, затем перейдите в меню File > Export > Export I/O Ports и выберите формат csv

2) В HyperLynx VX2.4 при анализе цепей вы можете в настройках осциллографа изменить расположение щупов и установить их либо на шариковый вывод ПЛИС, либо на кристалл, либо использовать локацию описанную параметром timing_location в IBIS-модели и измерить полную задержку линий передачи:

1) Касаемо Xilinx, можно cгенерировать файл c задержками в формате .csv через Vivado, для этого откройте проект вашей ПЛИС, RTL или netlist, затем перейдите в меню File > Export > Export I/O Ports и выберите формат csv

2) В HyperLynx VX2.4 при анализе цепей вы можете в настройках осциллографа изменить расположение щупов и установить их либо на шариковый вывод ПЛИС, либо на кристалл, либо использовать локацию описанную параметром timing_location в IBIS-модели и измерить полную задержку линий передачи:

А что за величина th?

Th это тоже самое что и mils, то есть одна тысячная от дюйма (1000th=1inch)

Ясно. Я привык видеть mils. Странно, что настройки CES (Setup > Settings) задаются в mm, а расчёт идёт в th.

Зарегистрируйтесь на Хабре, чтобы оставить комментарий

Влияние задержки и длины выводов микросхемы и ПО на расчет общей длины/задержки проводников