У многих FPGA или ПЛИС, ассоциируется с низкоуровневым программированием на языках VHDL, Verilog, или OpenCL. Платформа .NET уже давно захватила нишу микроконтроллеров, проект nanoFramework. Последние новости развития nanoFramework только доказывают твердость намерений платформы .NET освоить работу и на «железе». Казалось бы, пал последний бастион, где не было платформы .NET. Но это был далеко не последний рубеж. Как вам возможность писать код на C#, вместо хардкорного VHDL или Verilog, с последующей загрузки .NET сборок на FPGA процессоры Xilinx для непосредственного исполнения? Открытый проект Hastlayer преобразует сборки .NET в низкоуровневый код для FPGA процессоров, обеспечивая максимальный параллелизм и низкое энергопотребление.

Что такое FPGA?

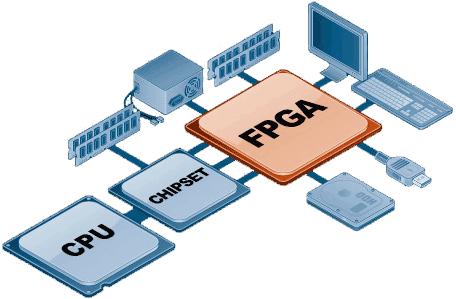

Микросхема FPGA (field-programmable gate array), она же программируемая логические интегральная схема (ПЛИС), — это микросхема (ИМС), которую можно конфигурировать под сложные вычислительные задачи. В индустрии существует потребность в специализированных микросхемах (ASIC, application-specific integrated circuit, «интегральная схема специального назначения») — от управления космических аппаратов до расчетов по финансовым моделям.

До появления FPGA сильным и одновременно слабым местом специализированных ИМС была жесткая функциональность, заложенная в микросхему, а также высокая сложность проектирования и стоимость запуска в производство. Функциональность ИМС закладывалась на этапе проектирования. Если после производства готовой микросхемы обнаруживались ошибки, то приходилось исправлять, и заново выпускать чипы. А предыдущую партию чипов выбрасывать, т.к. изменить логику микросхемы после производства не представлялось возможным. По сути, это приводило к созданию новой ИМС.

Появление на рынке FPGA-процессоров, стало настоящим прорывом в нише высокопроизводительных вычислений. FPGA-процессоры можно было перепрограммировать сколь угодное число раз, это существенно ускорило время разработки, время выхода продукта на рынок. Появились совершенно новые возможности для разработчиков аппаратных средств, в т. ч. работающих над программированием специализированных интегральных схем типа ASIC.

Технология FPGA решает специализированные задачи существенно быстрее процессоров общего назначения (CPU). Сфера применения FPGA-процессоров достаточно широка, например они используются в облачных вычислениях Microsoft Azure для задач искусственного интеллекта. На FPGA-процессорах от Intel, работает сверточная нейронная сети (DNN), которая обрабатывает информацию в режиме реального времени, например, распознает изображение или голос.

FPGA-процессор представлен матрицей логических вентилей, которая может быть запрограммирована (или «сконфигурирована»).

Матрица конфигурируемых логических блоков

Конфигурируемые логические блоки (CLB) должны взаимодействовать друг с другом и с внешней схемой. Для этих целей FPGA использует матрицу программируемых межсоединений и блоков ввода/вывода (I/O). «Программа» FPGA хранится в ячейках SRAM, которые влияют на функциональность блоков CLB и управляют коммутаторами, которые устанавливают пути подключения.

Идея заключается в том, что CLB включают в себя таблицы поиска, элементы хранения (триггеры и регистры) и мультиплексоры, которые позволяют CLB выполнять логические операции, операции хранения данных и арифметические операции.

FPGA-процессоры поставляются в составе отладочных плат или карт подключаемых по шине PCI-e. Обычно внешние отладочные платы дешевле карт, но скорость обмена данными отставляет желать лучшего, т.к. доступны только интерфейсы USB, Ethernet, UART. В случае использование карт PCI-e достигается максимальная скорость, но в этом случае карту приходится размещать внутри корпуса вычислительного узла.

FPGA-процессор

Программирование FPGA-процессоров

Как мы собираемся превратить массив настраиваемых логических блоков (CLB, Configurable Logic Block) в цифровую схему, которая делает именно то, что мы хотим? На первый взгляд это кажется довольно сложной задачей. Действительно, реализация FPGA обычно считается сложнее, чем программирование микроконтроллера. Однако разработка для FPGA не требует глубокого знания функциональности CLB или кропотливой компоновки внутренних межсоединений, так же как разработка для микроконтроллеров не требует глубокого знания инструкций на языке ассемблера процессора или внутренних сигналов управления.

На самом деле, несколько неверно представлять FPGA как самостоятельный компонент. FPGA поддерживается программным обеспечением для разработки, которое выполняет сложный процесс преобразования аппаратного проектирования в программируемые биты, которые определяют поведение межсоединений и CLB.

Это оставляет нам вопрос: как мы «объясним» программе, что должно делать аппаратное обеспечение FPGA?

Для решения этой задачи разработчики создали языки, которые позволяют нам «описывать» аппаратное обеспечение, они называются языки описания аппаратных средств (HDL, hardware description language), а два наиболее распространенных – VHDL и Verilog. Несмотря на очевидное сходство между HDL кодом и кодом, написанным на языке программирования высокого уровня, они принципиально отличаются друг от друга. Код программы определяет последовательность операций, тогда как HDL код больше похож на схему, которая использует текст для представления компонентов и создания взаимосвязей.

Пример цифровой схемы

Пример цифровой схемы, которая соответствует VHDL коду, приведенному ниже:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

----------------------------------------------------

entity circuit_2 is

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

c : in STD_LOGIC;

d : in STD_LOGIC;

out1 : out STD_LOGIC;

out2 : out STD_LOGIC);

end circuit_2;

-----------------------------------------------------

architecture Behavioral of circuit_2 is

signal sig1: std_logic;

begin

sig1 <= ( a and b );

out1 <= ( sig1 or c );

out2 <= (not d);

end Behavioral;

Теперь вы понимаете основные характеристики устройств программируемой логики и их потенциальные преимущества в отношении процессорных систем. Современные FPGA – это сложные, высокопроизводительные устройства, которые могут быть несколько пугающими для тех, кто привык использовать микроконтроллеры для сбора данных, управления микросхемами специального назначения и выполнения математических операций. Однако вы можете обнаружить, что в некоторых приложениях улучшенная производительность и универсальность стоят дополнительных усилий в разработке.

Подведем итог. FPGA, в отличие от CPU и GPU, можно перепрограммировать в соответствии с особенностями решаемой на них вычислительной задачи. Получается синтез специализированного процессора под конкретную задачу. Другими важными отличиями FPGA является пониженное энергопотребление в расчете на единицу вычислительной мощности, а также архитектура с параллельным исполнением множества векторных операций одновременно — так называемая массивно-параллельная мелкозернистая архитектура. Число ядер в чипе FPGA может достигать одного миллиона и более.

Проект HASTLAYER, запуск .NET сборок на FPGA-процессоре

Проект Hastlayer разрабатывает компания Lombiq Technologies, занимающейся веб-разработкой с использованием открытых технологий Microsoft. Среди известных разработок компании, система Orchard CMS. Hastlayer доступен в Azure Marketplace и Microsoft AppSource. В 2020 г. от Евросоюза, проект получил финансирование по программе Horizon 2020.

Теперь разберемся, как работает Hastlayer. Для начала кратко рассмотрим процесс компиляции программы на C#.

Вначале исходный код на C# компилируется в приложение или сборку с расширениями exe или dll на языке CIL. Common Intermediate Language (CIL) — «высокоуровневый ассемблер» виртуальной машины .NET. Промежуточный язык, разработанный фирмой Microsoft для платформы .NET Framework. По синтаксису и мнемонике язык CIL напоминает язык ассемблера. Его можно рассматривать как ассемблер виртуальной машины .NET. Далее, при запуске на выполнение подобного приложения происходит JIT-компиляция (Just-In-Time) в машинный код, который затем выполняется. Таким образом, получим цепочку, исходный код C# => сборка на языке CIL => машинный код.

Обратно вернемся к Hastlayer. Проект Hastlayer предназначен для платформы .NET, которая открыта и не привязана к Microsoft. Одно из преимуществ .NET заключается в том, что для написания программного обеспечения можно использовать большое количество языков программирования, потому что все программы, написанные на любом языке, будут преобразованы (скомпилированы) в один и тот же язык CIL.

Проект Hastlayer обрабатывает CIL-сборки и преобразовывает в конфигурацию для FPGA-процессора, таким образом вы можете создавать свои программы не только на C#, но и на других языках программирования, как С++, Python, PHP, даже на JavaScript. В качестве демонстрации возможности использования других языков, доступен пример Hast.Samples.FSharpSampleAssembly на языке F#.

Запуск Hastlayer на плате Nexys A7

Пока компиляция CIL кода происходит на удаленных серверах, некоторым это может, не понравится. Однако, по крайней мере, вы загружаете не свой исходный код на C#, а только .NET сборки в виде DLL файлов. Авторы проекта заявляют, что вы можете формировать, в том числе и обфуцированные сборки для защиты интеллектуальной собственности.

Общий процесс использования Hastlayer выглядит следующим образом:

- Программный код критически важный с точки зрения производительности выносится в отдельную сборку. В эту же сборку добавляется общий класс Hastlayer;

- Вызовы критически важных методов изменяются так, что бы проходить через слой Hastlayer. Это позволяет напрямую направлять вызовы к аппаратной части, если она доступна. Но в то же время сохраняется возможность запуска сборки .NET обычным способом, если, например FPGA-процессор отсутствует;

- Преобразование критически важной с точки зрения производительности, сборки выполняется с помощью Hastlayer: генерируется код на языке VHDL, который помещается в Hastlayer hardware framework, затем синтезируется и используется для программы подключенной к FPGA-процессору с инструментами toolchain поставщика оборудования;

- Теперь методы напрямую вызываются на FPGA-процессоре;

- Затем результат вычислений передается обратно программным компонентам по стеку вверх, которые и вызвали методы, после чего программа продолжает выполняться обычным образом.

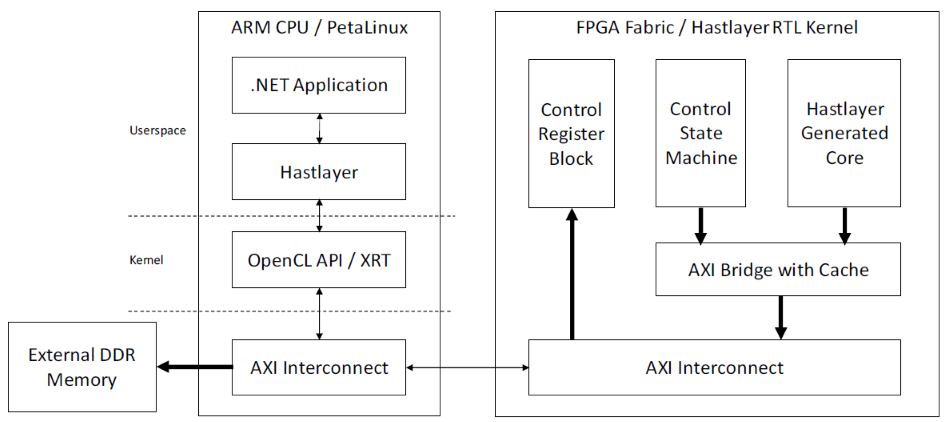

Если углубиться в детали, то работа Hastlayer базируется на OpenCL API. Данное API было разработано компанией NVIDIA для возможности разрабатывать программы для CUDA/AMD Stream, использующие вычислительные возможности GPU. Именно абстракция OpenCL дает возможность использовать различные FPGA-процессоры без переписывания основного программного кода прикладного приложения.

Общая архитектура системы

Применение Hastlayer

Hastlayer можно применять в следующих задачах:

- Машинное обучение и искусственный интеллект;

- Обработка изображений, обработка видео и компьютерное зрение;

- Алгоритмический трейдинг, финансовые расчеты;

- Сжатие и анализ данных;

- Майнинг криптовалюты;

- Криптография;

- Встраиваемые системы (роботы, дроны, спутники, IoT).

Hastlayer предназначен для разработчиков программного обеспечения, не обладающими знаниями в области аппаратного проектирования и схемотехники. Предоставляя высокоуровневый набор инструментов, Hastlayer позволяет разработчикам использовать возможности FPGA с их существующими навыками, т.е. разработчикам не требуется получать отдельное специализированное знание для разработки конфигурации для FPGA-процессора, достаточно знание платформы .NET, принципов параллельных вычислений, и хотя бы немного аппаратных средств. Это позволяет существенно расширить круг потенциальных разработчиков, а вместе с тем и компаний использующих FPGA-процессоры.

Оборудование

Nexys A7 (Nexys 4 DDR)

Для начальной разработки рекомендуется использовать плату Nexys A7, которая стоит всего 249 долларов. Но на этой плате далеко не все можно реализовать, что доступно в Hastlayer. Например, из-за небольшого объема, плата не может вместить большие алгоритмы и вдобавок поддерживает только медленные каналы связи (USB, Ethernet). Таким образом, Hastlayer с этой платой, подходит только для простых алгоритмов, которым необходимо обмениваться только небольшим объемом данных.

Плата Nexys A7

Nexys A7 (предыдущее название Nexys 4 DDR) — недорогая, но мощная FPGA плата для разработки. Разработанная на основе семейства процессоров Xilinx Artix-7 FPGA, Nexys A7 представляет собой готовую к использованию платформу для разработки цифровых схем, которую удобно использовать в учебной среде.

Плата Nexys A7 оборудована большим количеством различных интерфейсов, таких как 10/100 Ethernet, USB, UART, JTAG и VGA. На плате присутствует датчик температуры, микрофон и акселерометр.

Xilinx Alveo и AWS EC2 F1 instances

Xilinx Alveo

Для больших нагрузок рекомендуется использовать платы Xilinx Alveo U50, U200, U250 или U280. Данные карты, также доступны в виде облачного сервиса от Nimbix.

Инстансы F1 в Amazon EC2 на базе Xilinx обеспечат гибкую масштабируемость вашей системы.

Схема вычислений .NET приложения с использованием Xilinx Alveo

Модель исполнения карты Xilinx Alveo

.NET в космосе

23 февраля 2022 управляющий директор Lombiq Technologies и создатель Hastlayer, Zoltán Lehóczky провел демонстрацию как использовать аппаратное ускорение .NET с Hastlayer, в бортовых спутниковых системах, таких как CubeSat. Hastlayer подходит для небольших и простых спутников, благодаря быстрой разработке и низкого порога вхождения для разработчиков.

Презентация Hastlayer для проекта satsearch

Благодаря платформе .NET, разработчики бортовых спутниковых систем, как и разработчики веб/мобильных приложений смогут:

- Получить доступ к современным инструментам .NET;

- Использовать развитые IDE-среды;

- Используйте расширенную отладку приложения;

- Выполнять автотесты и мониторить производительность относительно участков программного кода;

- Использовать различные платформы для разработки и запуска приложений (Windows, Mac, некоторые дистрибутивы Linux).

Xilinx Zynq-7000 FPGA accelerator

Несмотря на то, что аппаратные платформы, такие как Xilinx Zynq, уже стали квазистандартами из-за их широкого использования, каждый производитель бортовых компьютеров (OBC) использует собственный набор инструментов SDK, с которым разработчикам необходимо разобраться, чтобы эффективно использовать все возможности платформы. Использование Hastlayer позволяет разработчикам унифицировать подход к написанию ПО, несмотря на различия в аппаратной части, как в свое время это было сделано в .NET nanoFramework.

Но возможности .NET не безграничны. Да, разработчики пишут безопасный управляемый код, но этот код не является детерминированным. Код на C# можно использовать для разработки приложений и ускорения обработки бортовой информации, но он не подходит для вычислений в режиме реальном времени или критически важных подсистем.

.NET в Catapult FPGA от Microsoft

С конца 2019 года проект Hastlayer поддерживает большие FPGA-процессоры проекта Microsoft Catapult platform. Проект Catapult был разработан в лаборатории Microsoft Research. Исследователи ставили себе целью, использование FPGA-процессоров для задач связанных с искусственным интеллектом, вычислений с большими данными, с предоставлением облачного доступа. Компания Microsoft одни из первых, среди поставщиков облачных решений, кто предоставила вычисления на FPGA-процессорах.

Используемая в проекте Catapult плата FPGA, на базе Intel Stratix 10

Проект Catapult себя зарекомендовал в таких службах как, Bing’s IndexServe engine, Azure Machine Learning, Azure Networking, Azure Cloud Server Infrastructure (CSI), и Azure Storage.

В 2015 г. впервые использовали сервера с FPGA-платами в дата-центрах для ускорения работы Bing и Azure

В 2017 г. Microsoft уже на базе проекта Catapult презентовала новый проект Brainwave для решения задач в области искусственного интеллекта в режиме реального времени. Режим реального времени означает, что система обрабатывает поступающие данный со сверхмалой задержкой, такие потоки данных как поисковые запросы, видео, потоки датчиков или взаимодействие с пользователями.

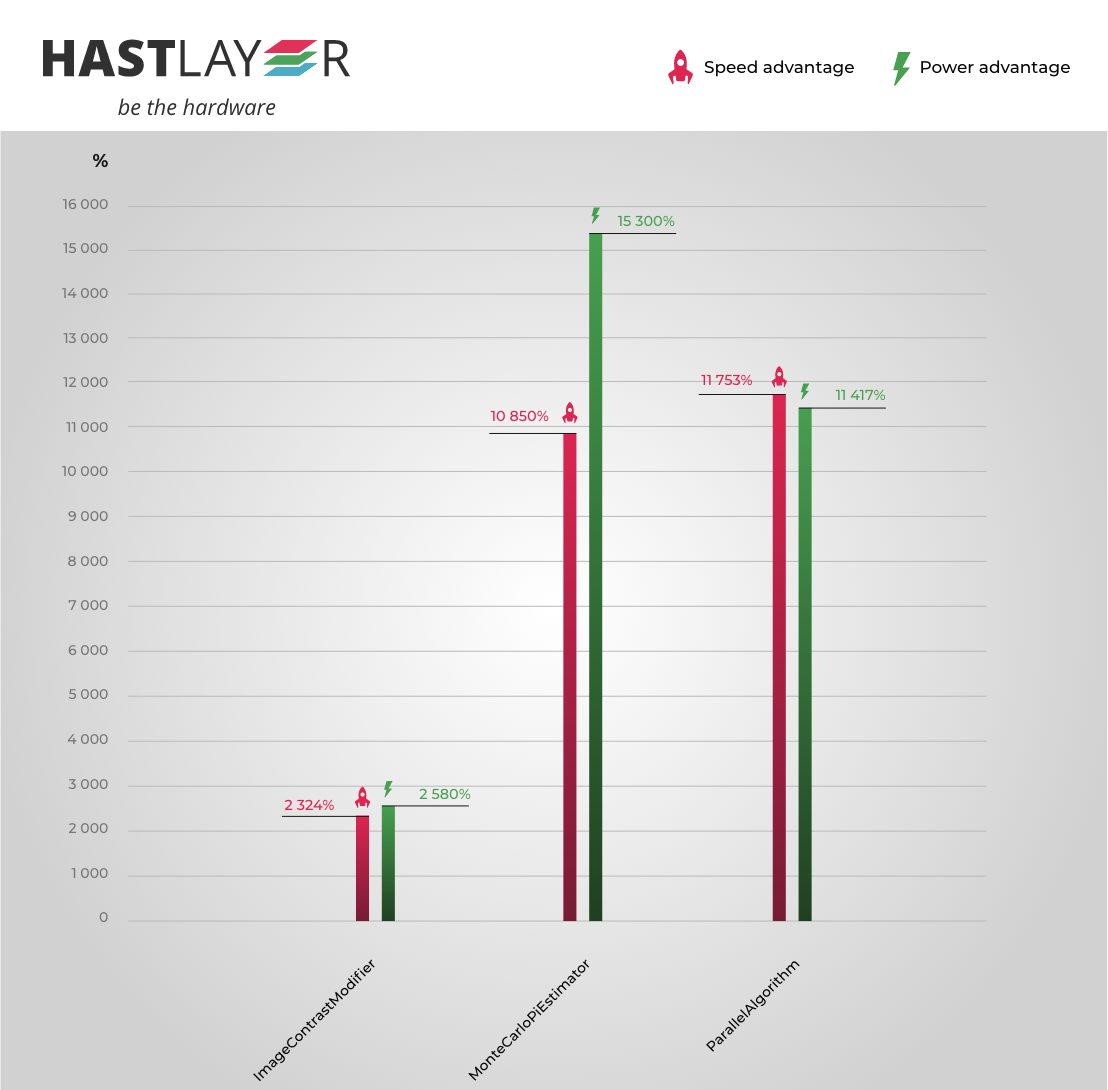

Тесты скорости использования Hastlayer по сравнению со стандартным .NET кодом

Необходимо обратить внимание, что прямое сравнение производительности несколько затруднено т.к. при использовании FPGA вы не запускаете программу на процессоре, как при использовании CPU или GPU, вместо этого создается процессор из вашего алгоритма.

Тем не менее, приведенные ниже результаты демонстрируют сравнение FPGA-процессора и хост-ПК (или ЦП), находящиеся примерно на одном уровне; например, сравнивается ЦП среднего уровня с FPGA среднего уровня.

Представленные алгоритмы в примерах Hastlayer, доступны для самостоятельной проверки. Вы можете просмотреть бенчмарк Zynq на GitHub, и некоторые примеры SDK Hastlayer.

В тестах сравнивается аппаратное ускорение Zynq-7000 FPGA с SoM ARM. В тестах используется модуль Trenz Electric TE0715-04-30-1C, подключенный к несущей плате TE0706 (с форм-фактором, аналогичным Raspberry Pi).

Характеристики следующие:

- FPGA: Xilinx Zynq XC7Z030-1SBG485C SoC FPGA. Основная частота 150 МГц;

- Хост: двухъядерный процессор ARM Cortex-A9 MPCore;

- Обе системы используют 1 ГБ (32-разрядной) памяти DDR3L SDRAM.

Согласно отчетам Trenz, энергопотребление составляет около 5 Вт. С помощью встроенного электросчетчика были получены результаты в потребление не менее 4,6 Вт.

В рамках теста было подготовлено две сборки, первая выполнялась только на CPU, другая только на FPGA. Для репрезентативности сборки неоднократно выполнялись в циклах.

Сравнение эффективности использования Hastlayer

Детальные результаты тестов доступны в таблице на GitHub, включая потребление электроэнергии в расчете полезной нагрузки на CPU и FPGA.

Разработка

Разработка ведется в Visual Studio 2019 или старше (любая редакция). Если используется Linux, то необходимо использовать проект Mono. Если у вас имеется совместимая FPGA плата, то вы можете запустить готовый пример для теста без обращения к службе Hastlayer Remote Services. Документация располагается в папке GitHub — Lombiq/Hastlayer-SDK/blob/dev/Docs/. Сборка должны быть основана на .NET Framework или .NET Core 3.1- 6.0.

Рассмотрим первый демонстрационный пример Hast.Samples.Demo, который запускает простые параллельные вычисления на FPGA-процессоре, файл Program.cs. Программный код разделяется на три региона:

- Configuration;

- HardwareGeneration;

- Execution.

region Configuration

В этом участке кода происходит инициализация самого FPGA-процессора, затем добавляется точка взаимодействия, и добавляется событие срабатывания после вычислений на процессоре.

using var hastlayer = Hastlayer.Create();

#region Configuration

var configuration = new HardwareGenerationConfiguration("Nexys A7", "HardwareFramework");

configuration.AddHardwareEntryPointType();

configuration.VhdlTransformerConfiguration().VhdlGenerationConfiguration = VhdlGenerationConfiguration.Debug;

hastlayer.ExecutedOnHardware += (_, e) =>

Console.WriteLine(

StringHelper.ConcatenateConvertiblesInvariant(

"Executing on hardware took ",

e.Arguments.HardwareExecutionInformation.HardwareExecutionTimeMilliseconds,

" milliseconds (net) ",

e.Arguments.HardwareExecutionInformation.FullExecutionTimeMilliseconds,

" milliseconds (all together)."));

#endregion Configuration

region HardwareGeneration

Определяем проксирующий/шлюз класс взаимодействия с FPGA-процессором.

#region HardwareGeneration

Console.WriteLine("Hardware generation starts.");

var hardwareRepresentation = await hastlayer.GenerateHardwareAsync(

new[]

{

typeof(ParallelAlgorithm).Assembly,

},

configuration);

#endregion HardwareGeneration

region Execution

Параллельные алгоритмы хорошо демонстрируют ускорение с помощью Hastlayer. Для примера берется класс/сборка ParallelAlgorithm, которая будет исполняться непосредственно на FPGA-процессоре.

Вначале выполняется замер времени работы на общем CPU. Ничего сложного, просто вызывается метод ParallelAlgorithm().Run(...). По итогу вычислений выводится информация о затраченном времени на вычисления.

#region Execution

Console.WriteLine("Hardware generated, starting software execution.");

var sw = System.Diagnostics.Stopwatch.StartNew();

var cpuOutput = new ParallelAlgorithm().Run(234234);

sw.Stop();

Console.WriteLine(StringHelper.ConcatenateConvertiblesInvariant("On CPU it took ", sw.ElapsedMilliseconds, " milliseconds."));

Затем выполняются вычисления уже на FPGA-процессоре.

Console.WriteLine("Starting hardware execution.");

var parallelAlgorithm = await hastlayer.GenerateProxyAsync(hardwareRepresentation, new ParallelAlgorithm());

var memoryConfig = hastlayer.CreateMemoryConfiguration(hardwareRepresentation);

var output1 = parallelAlgorithm.Run(234234, hastlayer, hardwareRepresentation.HardwareGenerationConfiguration);

var output2 = parallelAlgorithm.Run(123, hastlayer, hardwareRepresentation.HardwareGenerationConfiguration);

var output3 = parallelAlgorithm.Run(9999, hastlayer, hardwareRepresentation.HardwareGenerationConfiguration);

#endregion Execution

Как видим, программный код вызова алгоритма на FPGA-процессоре достаточно прост. В прокси-класс добавляем алгоритм new ParallelAlgorithm() для вычислений на FPGA-процессоре, затем точно так же, как и с CPU вызываем запуск.

И все, получаем результаты и сравниваем выигрыш в скорости.

А теперь посмотрим программный код метода ParallelAlgorithm().Run(...) файл ParallelAlgorithm.cs:

public virtual void Run(SimpleMemory memory)

{

var input = memory.ReadInt32(RunInputInt32Index);

var tasks = new Task[MaxDegreeOfParallelism];

// Hastlayer will figure out how many Tasks you want to start if you kick them off in a loop like this. If this

// is more involved then you'll need to tell Hastlayer the level of parallelism, see the comment in

// ParallelAlgorithmSampleRunner.

for (int i = 0; i < MaxDegreeOfParallelism; i++) { tasks[i] = Task.Factory.StartNew( indexObject =>

{

var index = (int)indexObject;

int result = input + (index * 2);

var even = true;

for (int j = 2; j < 9_999_999; j++)

{

if (even) result += index; else result -= index;

even = !even;

}

return result;

},

i);

}

// Task.WhenAny() can be used too.

Task.WhenAll(tasks).Wait();

int output = 0;

for (int i = 0; i < MaxDegreeOfParallelism; i++)

{

output += tasks[i].Result;

}

memory.WriteInt32(RunOutputInt32Index, output);

}

Как видим все просто, привычный алгоритм на C#. Согласитесь, на порядок проще примера VHDL-кода, который представлен в начале поста.

Приблизительная оценка сложности программирования отображена на диаграмме, чем выше значение, тем сложнее изучение, по заявлениям разработчиков Hastlayer.

Сравнение сложности изучения Hastlayer

Подробно про типы данных и построение алгоритма в документации — Working with Hastlayer.

Насколько хорош Hastlayer можно оценить, посмотрев тесты производительности.

Итог

Стартап Hastlayer безусловно заслуживает внимания. Проект Arduino в свое время, в сфере программирования микроконтроллеров сделал революцию и перевернул всю индустрию. Используя подход абстракций оборудования, теперь разработчику не требуется в деталях разбираться в какой регистр записать, а из какого регистра считать данные. Теперь он фокусируется на выполнение своей задачи и не задумывается над аппаратной реализации платформы. Вторым хорошим примером, для платформы .NET является фреймворк .NET nanoFramework. Написанный программный код, одинаково хорошо работает, как и на микроконтроллерах ESP32, так и на STM32. С единственной разницей, требуется указывать номера контактов для интерфейсов, и объемы памяти могут быть различны. Но при переносе программного кода, разработчику не придется переписывать с нуля основной код, и это существенный прогресс с точки зрения массовости и привлекательности платформы.

Проект Hastlayer делает то же самое, что и Arduino и NET nanoFramework, только в сфере использования FPGA-процессоров. Программный код для Hastlayer переносим между различными процессорами, мало того вычисления можно с легкостью перенести в облако Azure или AWS. С точки зрения работодателя гораздо проще найти на рынке .NET специалиста, немного его обучить для работы с Hastlayer, чем найти специалиста знающего, что такое VHDL-код.

Массовые вычисления на FPGA-процессорах это вторая волна революции, после представлению миру Arduino-подхода для программирования микроконтроллеров. Одним из признаков увеличения интереса к FPGA вычислениям является запуск сервиса бесплатной аренды отладочных плат с FPGA.

Вполне возможно, через несколько лет, на отладочной плате вместе с микроконтроллером типа ESP32 начнут размещать небольшой FPGA-сопроцессор, для небольших вычислительных задач, с возможностью программирования на C#.

.NET и C# — технологии, за которыми будущее!

Ресурсы

- Hastlayer — Lombiq Technologies

- Hastlayer-SDK — GitHub

- Hastlayer Samples — GitHub

- Spotlight advancing satellite software development with Hastlayer — of satsearch member Lombiq Technologies satsearch blog