Что делать, если человечество не сможет создать искусcтвенный интеллект никогда?

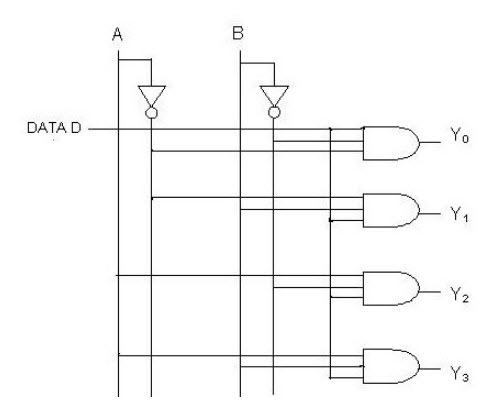

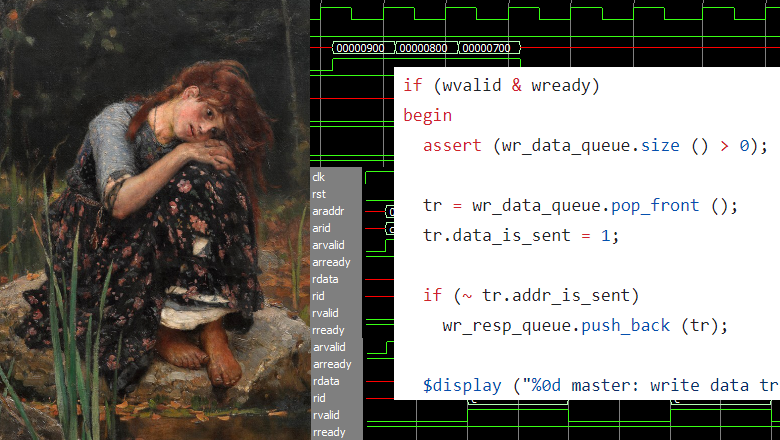

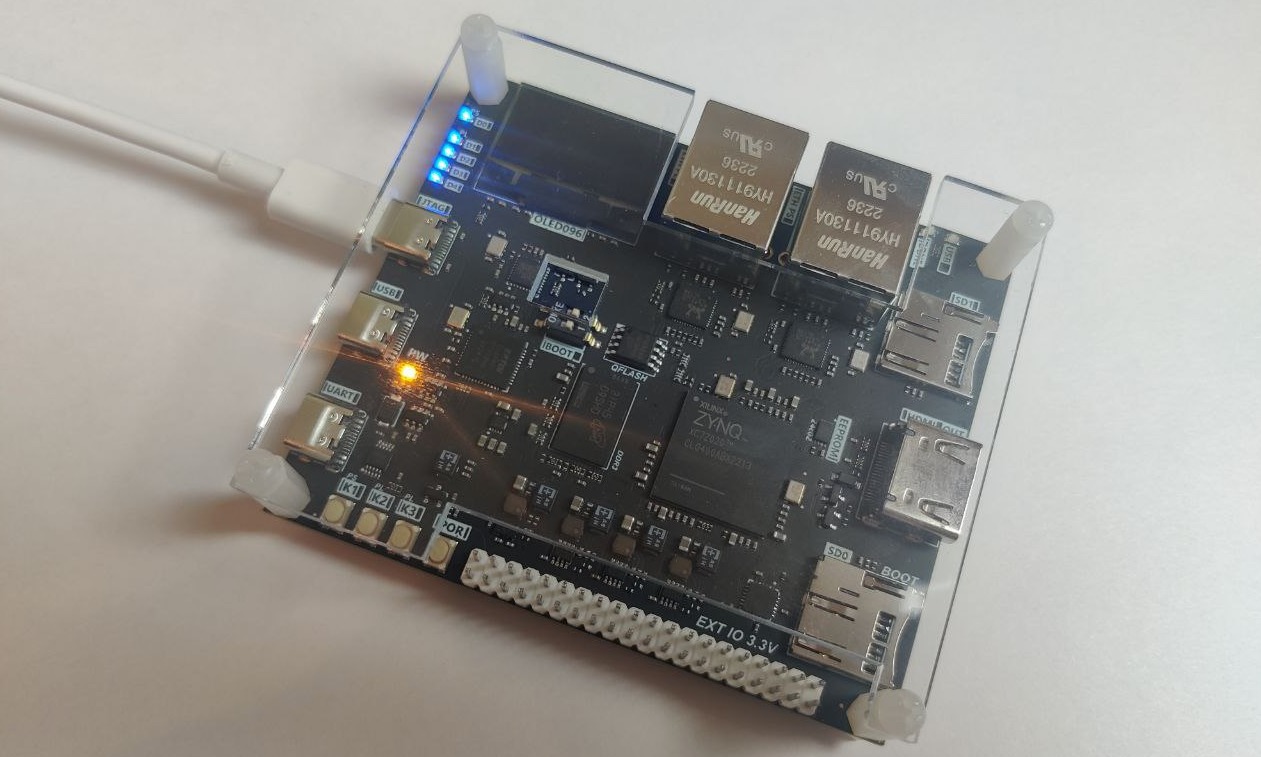

Любая комбинация софтвера и цифрового хардвера - от микроконтроллера, двигающего дворники у автомобиля - до серверной фермы с много-много-ядерными процессорами, аппаратными ускорителями ML и ChatGPT - сводятся к конечному автомату с достаточно большим состоянием. Независимо от сложности и адаптивности программ.

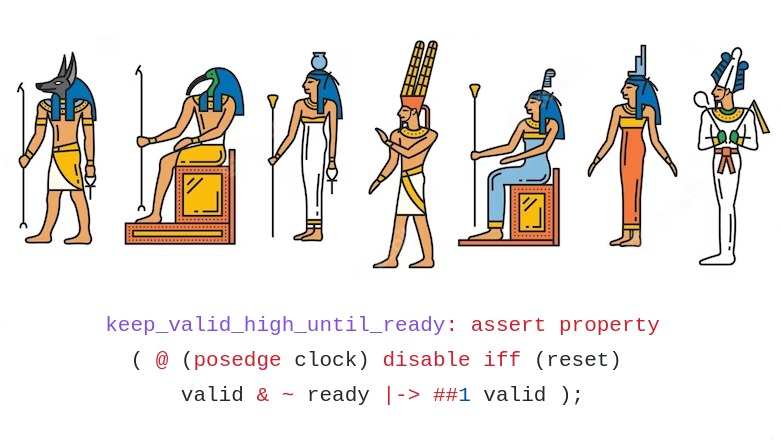

Сводится ли к конечному автомату человеческий интеллект? К сожалению, у человеческого интеллекта есть атрибут, природа которого современной науке неизвестна и который никогда не наблюдался у конечных автоматов, например у арифмометра. Этот атрибут - ощущение собственного "я", self-awareness. Конечно вы можете сделать в программе переменную "я_чувствую_собственное_я" и присвоить ей true, а потом утверждать, что вы симулируете собственное "я", но это жульничество, а не технология.

Я вовсе не пытаюсь нагонять мистику или агитировать за бога. Self-awareness наверняка такой же физический феномен, как какая-нибудь термоядерная реакция. Но скажем древние греки не знали природы термоядерной реакции. Наверное, они вели диалоги типа "если ты не веришь, что Солнце - просто большой костер из дров, то значит ты веришь в сказки про Зевса и других богов?"