Памяти Ивана Петровича Макарченко

От поклонников его творчества, и по совместительству моих собеседников

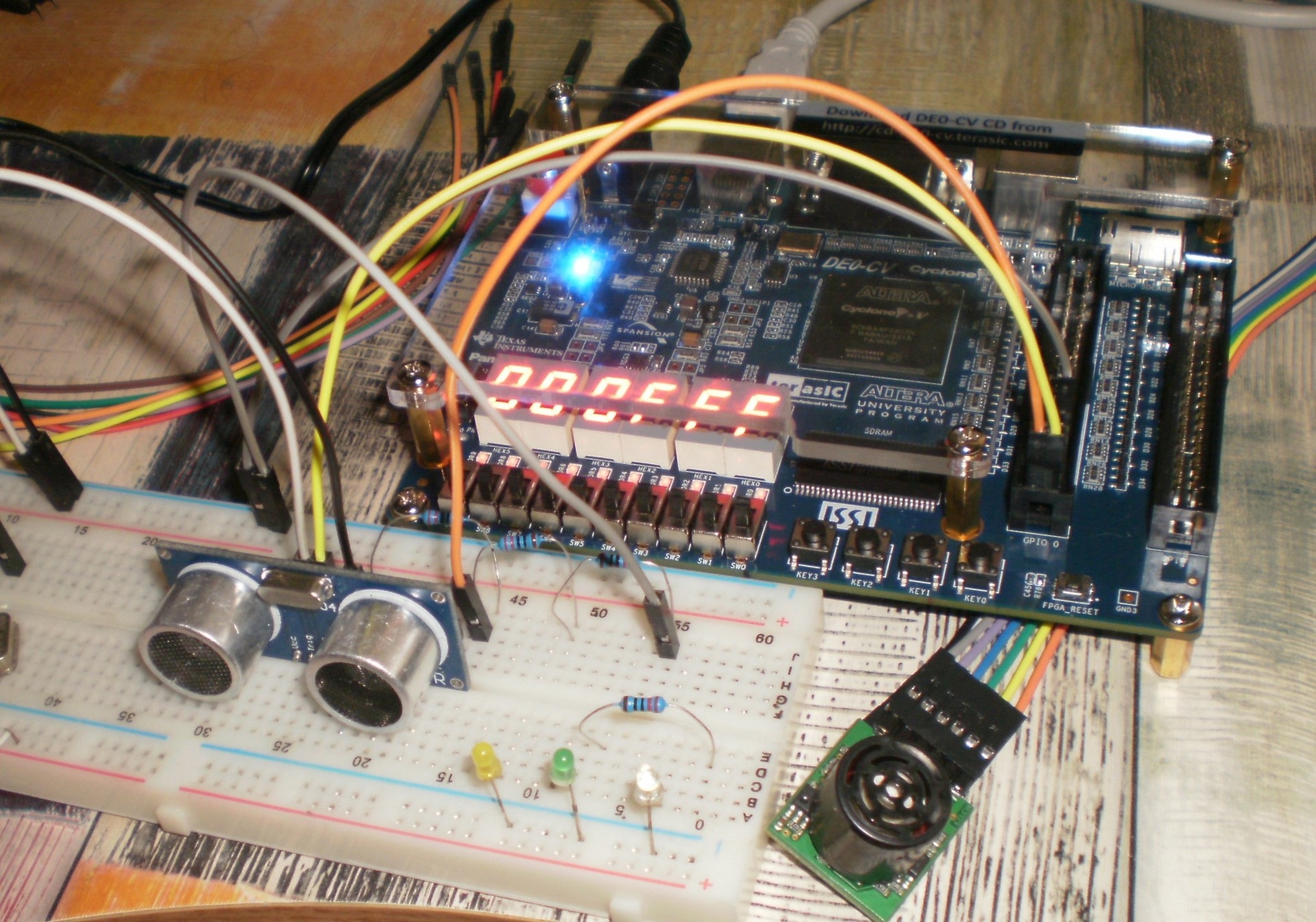

Я эпизодически интересовался компьютерами из серии сделай сам, те которые пользователь может спаять самостоятельно. Интересовался спектрумом и его многочисленными клонами, смотрел современные видео самостоятельных сборок спектрума на ютубе. Совершенно случайно, через знакомого я узнал, о редком, забытом 8 битном компьютере Спринтер, чья разработка внезапно ожила в последнее время. И который, возможно собрать своими руками.

Информации о данном проекте в интернете чрезвычайно мало, есть темы на форуме http://winglion.ru/ . Основные свои представления о Спринтере, я почерпнул из личного общения и telegram, поэтому возможно в моем посте будут содержаться фактические ошибки, или же простое недопонимание. Простой поиск по Хабру показал, что на нем нет статей по компьютеру Спринтер / Sprinter, есть только упоминания о нем в статьях посвященных zx spectrum. Моя статья это попытка закрыть этот пробел. Это моя первая статья на хабре, надеюсь она будет полезной для сообщества компьютера Sprinter, так и интересной для любителей ретро техники. Хотя, она может и выглядит довольно сумбурной. Сейчас необходимо сообщить всем лицам, которые могут быть заинтересованны в данном проекте, о его оживлении, а так же о текущем состоянии дел, кроме того дать ссылки на тематические ресурсы, и каналы связи с разработчиками.

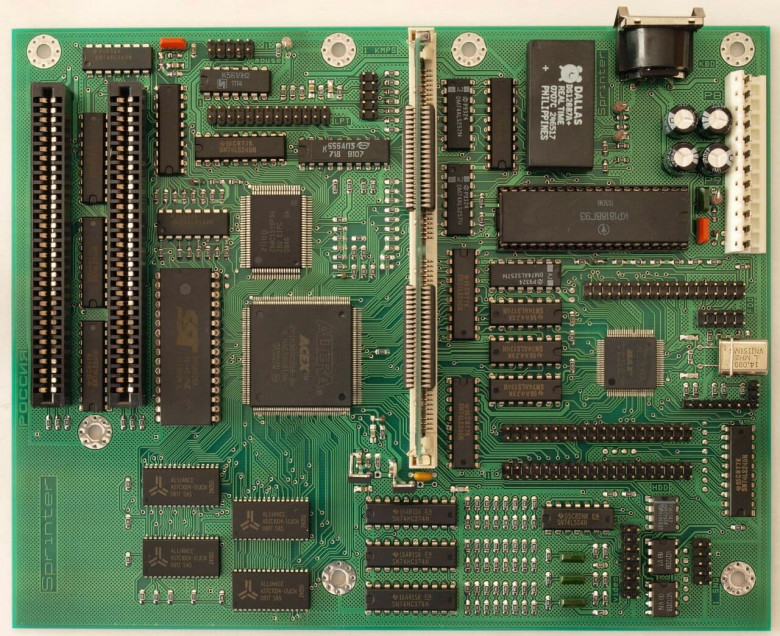

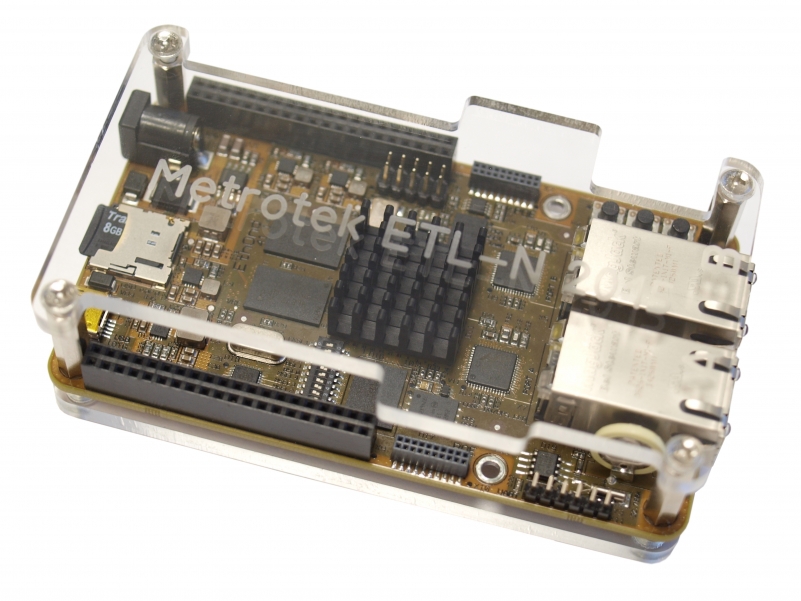

Персональный компьютер Спринтер, достаточно современный 8 -битный компьютер, чья окончательная версия была представлена фирмой Петерсплюс/Peters Plus 7 августа 2000 г. Хотя рабочий прототип был впервые представлен на компьютерной выставке enlight'96, в 1996 году. Его производство было остановлено в 2003 году. 1 февраля 2007 Иван Мак - Иван Макарченко- winglion (разработчик компьютера Спринтер) объявил о том, что фирма Петерсплюс отдала ему все наработки, по - этому компьютеру, и теперь он готов со временем открыть проект. После его смерти, поддержкой, восстановлением проекта, и дальнейшей разработкой данного компьютера занимается группа энтузиастов.