Сколковская Школа Синтеза Цифровых Схем начиналась как широкое, но относительно поверхностное мероприятие, в основном для профориентации школьников. Однако в процессе из участников образовалась небольшая стабильная группа, в основном из студентов вузов, которая хочет продолжить изучать тему проектирования микросхем вглубь, до уровня, когда они могут собеседоваться в электронные компании.

По этой причине в новом году меняется формат мероприятия. Если раньше планировалось два набора в год по 13 занятий, то теперь набор становится годовым на 23 занятия. В новую программу войдет введение в цифровую обработку сигналов на ПЛИС, графика с кадровым буфером на ПЛИС и даже проектирование микроархитектуры блока с алгоритмом Томасуло - классический способ реализации внеочередного выполнения инструкций в суперскалярном процессоре.

Кроме этого увеличивается участие EDA и semiconductor IP компаний в подготовке семинаров. В частности школа договорилась с Syntacore, Cadence Design Systems, Synopsys, Siemens EDA / Mentor Graphics и Imagination Technologies об использовании их материалов, лицензий, в некоторых случаях их инженеров и лекторов. Студенты и даже школьники получат возможность поработать с тем же софтвером для проектирования микросхем, который используют инженеры в Apple и NVidia.

Новый план семинаров начиная с этой субботы (если вы хотите участвовать в эту субботу и не сообщили Александру Биленко info@chipexpo.ru, то вы еще можете прислать к нему емейл - там осталось несколько мест):

Секция "Введение в центральные процессоры"

15 января 2022: 9. Проектирование процессорного кэша и измерение его производительности.

Ведут инженеры компании Syntacore БогданаТищук, Николай Терновой и Павел Куроедов.

Секция "Стандартные блоки и приемы проектирования"

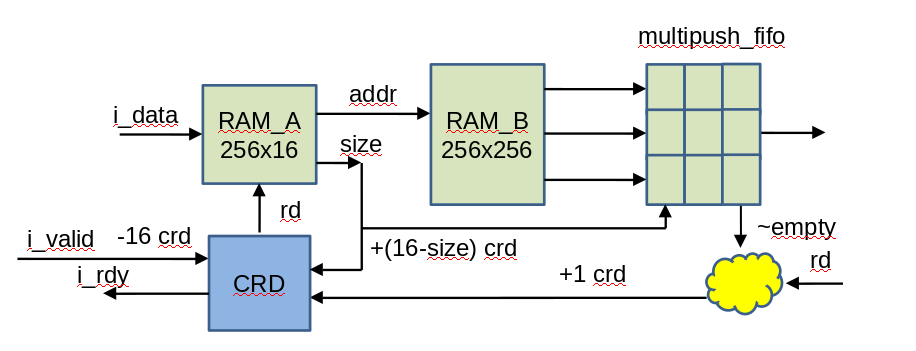

22 января 2022: 10. Стандартные блоки и приемы проектирования: очереди FIFO и кредитные счетчики.

29 января 2022: 11. Стандартные блоки и приемы проектирования: арбитры, банки и разделение памяти.

Ведет Дмитрий Смехов, инженер-разработчик ПЛИС, компании IRQ, ИнСис и Inline Group.

Секция "Маршрут проектирования массовых микросхем ASIC"

5 февраля 2022: 12. Пробуем маршрут RTL2GDSII: как разрабатываются массовые микросхемы. Часть I. Cadence.

12 февраля 2022: 13. Пробуем маршрут RTL2GDSII: как разрабатываются массовые микросхемы. Часть II. Synopsys.

Синтез, размещение и трассировка двух примеров - schoolRISCV и модуля игры со спрайтами. Демонстрация измерения динамического энергопотребления и формальной верификации логической эквивалентности, Logic Equivalence Checker - LEC.

Проводится в МИЭТ. Ведет Александр Михайлович Силантьев, преподаватель Национального исследовательского университета «Московский институт электронной техники» (МИЭТ).

19 февраля 2022: 14. Маршрут физического проектирования от Siemens EDA / Mentor Graphics.

Занятие состоит из двух частей. В первой части демонстрируется смешанный маршрут проектирования, когда для логического синтеза используются программы для Cadence или Synopsys, а для физического размещения и трассировки используеются программы от Siemens EDA / Mentor Graphics.

Вторая часть - обзор алгоритмов, которые используются на маршруте RTL2GDSII.

Ведет Александр Силантьев, МИЭТ с помощью лекторов из МИЭТ и Mentor Graphics.

26 февраля 2022: 15. Продвинутая отладка с помощью временных диаграмм и утверждений темпоральной логики.

С участием лекторов из Mentor Graphics / Siemens EDA.

Секция "Продолжение работы с периферийными устройствами, графикой и звуком"

5 марта 2022: 16. Подсоединение FPGA платы к компьютеру через текстовую консоль PuTTY, с использованием переходника USB-to-UART. Разбор учебного проекта: стековый калькулятор c обратной польской записью (реализованный без процессора, чистый аппаратный конечный автомат со стеком) и диалогом с пользователем через компьютер.

Организатор - Рафаэль Ильясов, руководитель Дизайн-центра электроники и микроэлектроники Университета Иннополис.

12 марта 2022: 17. Графика с кадровым буфером (frame buffer). Создаем видеопроцессор, который может рисовать прямые, квадраты и окружности по командам, которые генерирует центральный процессор.

Ведет Дмитрий Смехов.

19 марта 2022: 18. Первые шаги в цифровой обработке сигналов (ЦОС) / Digital Signal Processing (DSP). Эксперименты с цифровым фильтром, микрофоном и усилителем. Изменение тембра голоса или мелодии, создание эха. Презентация о практическом использовании преобразования Фурье и демонcтрация его на FPGA.

Сергей Анатольевич Иванец, декан факультета электронных и информационных технологий, Черниговский национальный технологический университет, Украина. В кооперации с Александром Силантьевым, МИЭТ.

Секция "Стандартные блоки и приемы проектирования: продолжение"

26 марта 2022: 19. Пересечение тактового домена, Clock Domain Crossing - CDC. Обмен данными между блоками, которые работают на разных частотах. Популярная тема во время интервью. Разбор нескольких способов, как избежать потери данных или получения лишних данных, в том числе с помощью применекния асинхронной очереди FIFO.

Организует Александр Силантьев.

Секция "Продвинутая микроархитектура центральных процессоров"

2 апреля 2022: 20. Внеочередное выполнение инструкций, алгоритм Томасуло и переименование регистров.

Организует Александр Силантьев с коллегами по МИЭТ.

9 апреля 2022: 21. Три образовательных пакета с учебными процессорами:

1. Упражнения с учебным процессором YRV с архитектурой RISC-V от Монте Далримпл.

Подготовкой материалов занимается Дмитрий Смехов и Иннополис.

2. Упражнения с пакетом RVfpga от компании Imagination Technologies на основе RISC-V ядра от Western Digital, с использованием плат с Xilinx Artix-7 FPGA.

Только три дня назад вышла версия этого пакета с документацией на русском языке

В подготовке принимает участие декан Илья Кудрявцев из Самарского Университета, МИЭТ и Imagination Technologies.

3. Использование языка TIE для расширения процессоров Tensilica XTensa от Cadence Design Systems.

При необходимости, это занятие может быть расширено.

Секция "Проверка и соревнование"

16 апреля 2022: 22. Имитиция собеседования на позицию проектировщика

цифровых микросхем на уровне регистровых передач.

23 апреля 2022: 23. Разбор имитации интервью и презентации проектов

участников Школы.

Видео с предыдущего занятия по микроархитектуре конвейерных процессоров. На нем Дмитрий Смехов также показать как прицепить к простейшему процессору простейший видеопроцессор: