Трудно представить другую технологию, которая настолько разносторонняя как FPGA.

FPGA — Field-Programmable Gate Array, то есть программируемая логическая матрица (ПЛМ), программируемая логическая интегральная схема (ПЛИС). Это технология, при которой создается микросхема с набором логических элементов, триггеров, иногда оперативной памяти и программируемых электрических связей между ними. При этом программирование FPGA оказывается похоже на разработку электрической схемы, а не программы. Пользуюсь данной технологией давно и попробую описать самые полезные с моей точки зрения применения по мере их усложнения.

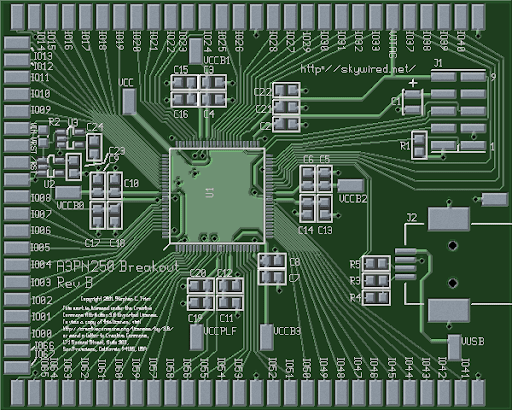

Многие наверняка сталкивались, что центральный процессор, память, другие многоногие микросхемы создавали люди, редко задумывающиеся о том, как они будут соединяться на печатной плате. Протянуть шину разрядностью 32 или 64 бита — задача не решаемая без многослойной платы. Но стоит поставить между микросхемами FPGA как разводка становится на несколько порядков проще:

И все это благодаря возможности внутренней перекоммутации сигналов внутри FPGA.

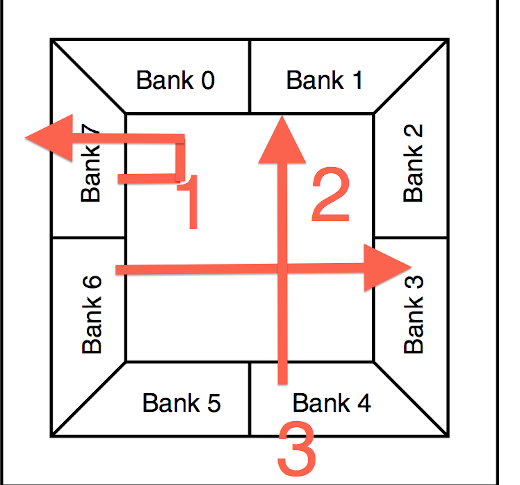

Часть микросхем имеет интерфейс 1.2В, другая 1.5, 1.8, 2.5, 3.3В, и все эти микросхемы можно подключить к одной FPGA и обеспечить двусторонний обмен за счет того, что любая FPGA имеет несколько банков ввода-вывода, каждый из которых может иметь свое опорное напряжение сигналов. Например, так:

FPGA достаточно дорогие, но надежные устройства. Они начинают включаться при меньшем напряжении, чем номинальное, выдерживают импульсные наводки, часто короткое замыкание на ножках IO, быстро загружаются и могут использоваться для контроля и управления процессорами и умной периферией. Плюс могут реализовывать вспомогательные функции коммутации, задержек, моргания светодиодом и так далее. Мне очень нравится использовать FPGA (маленький PLD) как умный сторожевой таймер и схема запуска — ни разу не подводил.

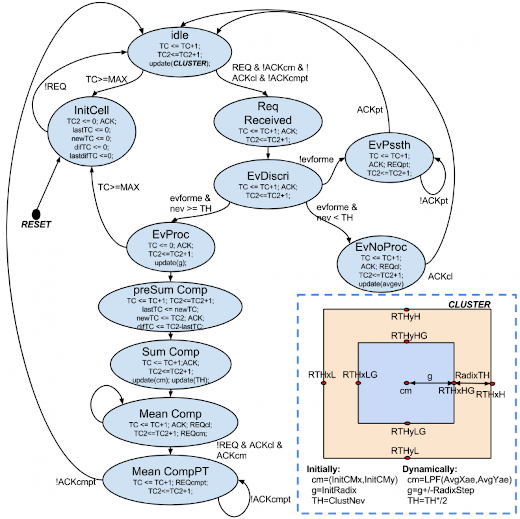

Если на процессоре сначала создается «исполнитель команд», то есть процессор, а потом в него загружается последовательность команд, то на FPGA можно писать программу с командами, вшитыми в структуру прошивки. При этом отсутствует избыточность процессора, появляется малое потребление при той же скорости и функциональности, гарантированное время выполнения и высокая надежность. Пример такого автомата состояний:

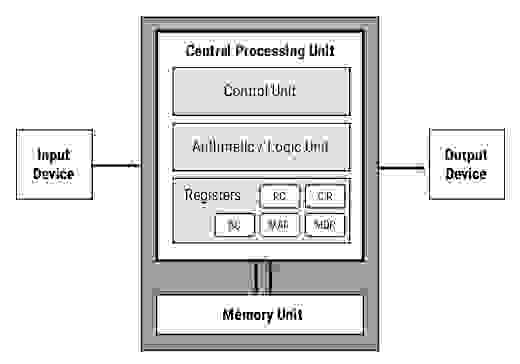

Считается, что каждый программист должен написать хотя бы один компилятор, а каждый инженер должен разработать хотя бы один процессор. Это очень интересный и важный процесс, позволяющий лучше понять как работают микропроцессоры, при этом можно оптимизировать под свои задачи систему команд, встраивать большое количество одновременно работающих процессоров в одну микросхему и получать настоящую многозадачность с низким энергопотреблением. При этом структура процессора проста и легко реализуема на FPGA:

Недостатком такого процессора является отсутствие готовых компиляторов и отладчиков.

Библиотеки готовых процессоров есть у любого производителя FPGA (от 8086 до ARM), позволяют быстро создать процессор с определенным набором периферии и вставить его в проект FPGA. К процессору прилагается компилятор и отладчик. Быстро, удобно, но избыточно и потому ограничено по быстродействию. Пример структуры готовой библиотеки процессора:

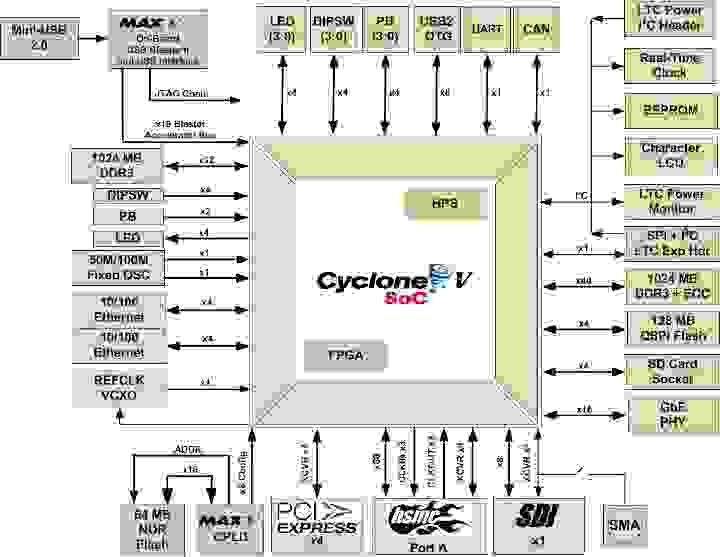

SoC — достаточно новая технология, решающая самую страшную проблему инженера, необходимость протаскивать по плате много высокоскоростных интерфейсов, которых всегда оказывается недостаточно, и которые необходимо программно поддерживать. Технология SoC позволяет в одной микросхеме иметь полноценный центральный процессор (поддерживающий операционную систему Linux, например) или микроконтроллер и большую FPGA, соединенные логическими сигналами, общей внутренней памятью и интерфейсами к внешней. То есть проблема эффективной, простой и быстрой передачи информации между FPGA и процессором успешно решена! Пример структуры SoC:

Видно, что FPGA и HPS (Host Processor System, процессор) находятся внутри одной микросхемы и окружены программируемыми ножками ввода-вывода. Действительно это многофункциональная система на кристалле.

Вспоминая, что FPGA — это набор логических ячеек и триггеров, работающих параллельно, на FPGA можно проводить много параллельных операций, что отличает от процессора, параллельность которого ограничена количеством ядер и потоков. Поэтому можно использовать FPGA как сопроцессор к центральному процессору, вынося на FPGA все самые требовательные к вычислительной мощности операции. Например, центральный процессор занимается логической обработкой задачи, а FPGA параллельно вычисляет контрольные суммы, хэши, ищет совпадения, перебирает варианты и так далее. Быстродействие FPGA ограничено только количеством параллельных блоков и временем выполнения одной операции. Отладив таким образом вычисления можно заказать ASIC, то есть заказную микросхему, выполняющую те же функции, но дешевле (при массовом производстве) и с меньшим энергопотреблением. И данная идея оказалась настолько перспективной и удобной, что гиганты разработки FPGA начали создавать специальное ПО, позволяющее интерактивно переносить части вычислений из программы на C/C++ в FPGA и контролировать быстродействие (HLS, High-Level Synthesis). Есть готовые платы с быстрыми интерфейсами для этого и средства отладки. Очень интересная и перспективная тема для использования.

Нейронные сети и глубокие нейронные сети сейчас активно используются в разных областях, но реализация их на процессоре оказывается неэффективной — существует много вычислений, которые можно распараллелить (нейроны одного слоя, например, вычисляются независимо).

Поэтому перенеся нейронную сеть на FPGA удается на много порядков ускорить работу нейронной сети, остается обеспечить высокоскоростной интерфейс для загрузки исходных данных и получения результата. В качестве примера — реализация системы распознавания лиц на процессоре i7/9Gen распознает до 20 лиц за секунду с одной видеокамеры HD, реализация на FPGA — порядка 1000 лиц с нескольких камер. Структура используемой глубокой нейронной сети:

Это только часть применений FPGA, с которыми можно столкнуться.

И жаль, что не так много людей ее активно используют и развивают.

FPGA — Field-Programmable Gate Array, то есть программируемая логическая матрица (ПЛМ), программируемая логическая интегральная схема (ПЛИС). Это технология, при которой создается микросхема с набором логических элементов, триггеров, иногда оперативной памяти и программируемых электрических связей между ними. При этом программирование FPGA оказывается похоже на разработку электрической схемы, а не программы. Пользуюсь данной технологией давно и попробую описать самые полезные с моей точки зрения применения по мере их усложнения.

1. Помощь при разводке плат

Многие наверняка сталкивались, что центральный процессор, память, другие многоногие микросхемы создавали люди, редко задумывающиеся о том, как они будут соединяться на печатной плате. Протянуть шину разрядностью 32 или 64 бита — задача не решаемая без многослойной платы. Но стоит поставить между микросхемами FPGA как разводка становится на несколько порядков проще:

И все это благодаря возможности внутренней перекоммутации сигналов внутри FPGA.

2. Согласование уровней сигналов

Часть микросхем имеет интерфейс 1.2В, другая 1.5, 1.8, 2.5, 3.3В, и все эти микросхемы можно подключить к одной FPGA и обеспечить двусторонний обмен за счет того, что любая FPGA имеет несколько банков ввода-вывода, каждый из которых может иметь свое опорное напряжение сигналов. Например, так:

3. Обеспечение надежности устройства

FPGA достаточно дорогие, но надежные устройства. Они начинают включаться при меньшем напряжении, чем номинальное, выдерживают импульсные наводки, часто короткое замыкание на ножках IO, быстро загружаются и могут использоваться для контроля и управления процессорами и умной периферией. Плюс могут реализовывать вспомогательные функции коммутации, задержек, моргания светодиодом и так далее. Мне очень нравится использовать FPGA (маленький PLD) как умный сторожевой таймер и схема запуска — ни разу не подводил.

4. Автоматы состояний или аппаратное программирование

Если на процессоре сначала создается «исполнитель команд», то есть процессор, а потом в него загружается последовательность команд, то на FPGA можно писать программу с командами, вшитыми в структуру прошивки. При этом отсутствует избыточность процессора, появляется малое потребление при той же скорости и функциональности, гарантированное время выполнения и высокая надежность. Пример такого автомата состояний:

5. Создание процессора внутри FPGA

Считается, что каждый программист должен написать хотя бы один компилятор, а каждый инженер должен разработать хотя бы один процессор. Это очень интересный и важный процесс, позволяющий лучше понять как работают микропроцессоры, при этом можно оптимизировать под свои задачи систему команд, встраивать большое количество одновременно работающих процессоров в одну микросхему и получать настоящую многозадачность с низким энергопотреблением. При этом структура процессора проста и легко реализуема на FPGA:

Недостатком такого процессора является отсутствие готовых компиляторов и отладчиков.

6. Использование готовых библиотек процессоров для FPGA

Библиотеки готовых процессоров есть у любого производителя FPGA (от 8086 до ARM), позволяют быстро создать процессор с определенным набором периферии и вставить его в проект FPGA. К процессору прилагается компилятор и отладчик. Быстро, удобно, но избыточно и потому ограничено по быстродействию. Пример структуры готовой библиотеки процессора:

7. Объединять процессор и периферию в одной микросхеме — SoC (System-On-Chip)

SoC — достаточно новая технология, решающая самую страшную проблему инженера, необходимость протаскивать по плате много высокоскоростных интерфейсов, которых всегда оказывается недостаточно, и которые необходимо программно поддерживать. Технология SoC позволяет в одной микросхеме иметь полноценный центральный процессор (поддерживающий операционную систему Linux, например) или микроконтроллер и большую FPGA, соединенные логическими сигналами, общей внутренней памятью и интерфейсами к внешней. То есть проблема эффективной, простой и быстрой передачи информации между FPGA и процессором успешно решена! Пример структуры SoC:

Видно, что FPGA и HPS (Host Processor System, процессор) находятся внутри одной микросхемы и окружены программируемыми ножками ввода-вывода. Действительно это многофункциональная система на кристалле.

8. Модные приложения типа crypto mining

Вспоминая, что FPGA — это набор логических ячеек и триггеров, работающих параллельно, на FPGA можно проводить много параллельных операций, что отличает от процессора, параллельность которого ограничена количеством ядер и потоков. Поэтому можно использовать FPGA как сопроцессор к центральному процессору, вынося на FPGA все самые требовательные к вычислительной мощности операции. Например, центральный процессор занимается логической обработкой задачи, а FPGA параллельно вычисляет контрольные суммы, хэши, ищет совпадения, перебирает варианты и так далее. Быстродействие FPGA ограничено только количеством параллельных блоков и временем выполнения одной операции. Отладив таким образом вычисления можно заказать ASIC, то есть заказную микросхему, выполняющую те же функции, но дешевле (при массовом производстве) и с меньшим энергопотреблением. И данная идея оказалась настолько перспективной и удобной, что гиганты разработки FPGA начали создавать специальное ПО, позволяющее интерактивно переносить части вычислений из программы на C/C++ в FPGA и контролировать быстродействие (HLS, High-Level Synthesis). Есть готовые платы с быстрыми интерфейсами для этого и средства отладки. Очень интересная и перспективная тема для использования.

9. Реализация нейронных сетей на FPGA

Нейронные сети и глубокие нейронные сети сейчас активно используются в разных областях, но реализация их на процессоре оказывается неэффективной — существует много вычислений, которые можно распараллелить (нейроны одного слоя, например, вычисляются независимо).

Поэтому перенеся нейронную сеть на FPGA удается на много порядков ускорить работу нейронной сети, остается обеспечить высокоскоростной интерфейс для загрузки исходных данных и получения результата. В качестве примера — реализация системы распознавания лиц на процессоре i7/9Gen распознает до 20 лиц за секунду с одной видеокамеры HD, реализация на FPGA — порядка 1000 лиц с нескольких камер. Структура используемой глубокой нейронной сети:

Это только часть применений FPGA, с которыми можно столкнуться.

И жаль, что не так много людей ее активно используют и развивают.