Доброго времени суток! Наверное, вы все знакомы с компьютерной оперативной памятью DDRx (где x - поколение). Я бы хотел вам рассказать о ней с точки зрения SI (Signal Integrity - целостность сигналов) и принципов трассировки этого интерфейса.

Читая документацию на различные микросхемы CPU, FPGAs, DSPs, ASICs можно увидеть много различных рекомендаций, так называемых "Rules of Thumb", по трассировке DDR3/4 SDRAM (Double Data Rate Synchronous Dynamic Random Access Memory — синхронная динамическая память с произвольным доступом и удвоенной скоростью передачи данных). Но в ней редко можно встретить информацию почему именно так это необходимо делать. В этой статье я попытаюсь вам объяснить различные способы улучшения SI с точки зрения схемотехники и топологии.

Меня зовут Сергей. Я занимаюсь схемотехникой и топологией печатных плат. Так как я сам только учусь, процитирую Texas Instruments:

Оглавление:

Введение

Начать наш разговор стоит с основной проблемы, с которой столкнулись при увеличении скорости передачи – это отражения сигнала от конца линии данных SDRAM. Для уменьшения этих отражений, начиная с DDR2 была добавлена встроенная терминация On Die Termination (ODT).

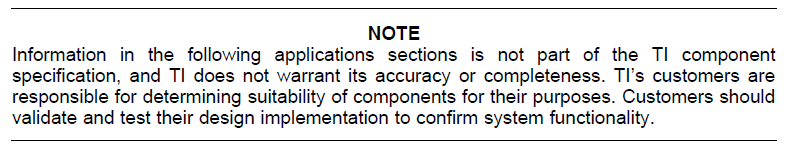

Поэтому давайте разберемся как происходит согласование импедансов. В идеальном случае сигнал от драйвера проходит по линии передачи печатной платы до нагрузки и полностью на ней поглощается. Но сигнал отражается всякий раз, когда проходит участок с изменяющимся импедансом. Например, выходной импеданс драйвера как правило в районе 15-30 ом, линия передачи 50 Ом, а приемник с CMOS логикой, имеет очень большое входное сопротивление порядка сотен кОм. В таких случаях в основном используются два типа терминации: последовательное согласование на стороне передатчика и параллельное на стороне приемника:

В первом варианте, сумма последовательного согласующего резистора Rs_Term и выходного импеданса драйвера R_Driver должна быть равна волновому сопротивлению линии передачи Z. В таком случае коэффициент отражения сигнала от ближнего конца линии равен нулю.

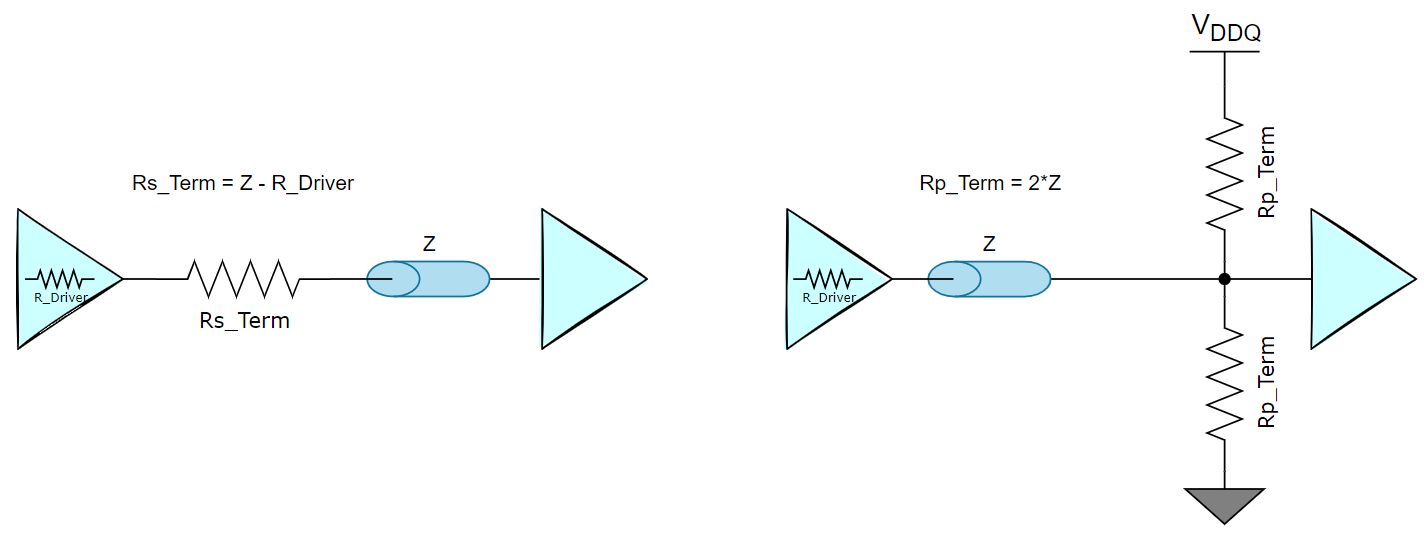

При выставлении единицы из-за получившегося делителя напряжения R_Driver + Rs_Term и импеданса линии Z, по линии передачи будет распространяться сигнал равный половине напряжения драйвера. Коэффициент отражения от дальнего конца линии равен +1. В результате наложения падающего и отраженного сигналов, сигнал на входе Receiver возрастет до напряжения драйвера. Отраженный сигнал (половинной амплитуды) при этом возвращается на вход драйвера и полностью поглощается нагрузкой R_Driver + Rs_Term. Но если на линии передачи есть два приемника (два модуля памяти), то у того, который находится в середине линии, будет сигнал равный получившемуся после делителя и через какое-то время придёт отраженный сигнал от дальнего приемника, в зависимости от длины линии (Vser_mid):

Vser_mid – Напряжение на первом приемнике,

Vser_far – Напряжение на дальнем приемнике.

Из вышеописанного видно, что такой тип согласования не подходит для DDR.

Второй тип — это параллельное согласование на стороне приемника. В этой схеме эквивалентное сопротивление параллельного соединения сопротивлений Rp_Term выбирается равным волновому сопротивлению Z линии передачи, то есть Rp_Term=2*Z. Таким образом не будет возникать отражений на нагрузке и тем самым сигнал у второго приемника в линии будет хорошей формы:

Тем самым такой тип согласования подходит для использования в DDR. И именно поэтому в DDR1- DDR3 был выбран тип логики Stub Series Terminated Logic (SSTL) с аналогичным согласованием. Эти согласующие резисторы на приемной стороне в интерфейсе DDR называются ODT. Подключение его к линии, и его сопротивление определяется при конфигурации контроллером, оно задается через RTT_PARK, RTT_NOM, RTT_WR.

Так же стоит отметить, что благодаря согласованию на стороне нагрузки время нарастания переходной характеристики при работе на емкостную нагрузку будет вдвое меньше по сравнению с линией передачи, согласованной на стороне передатчика.

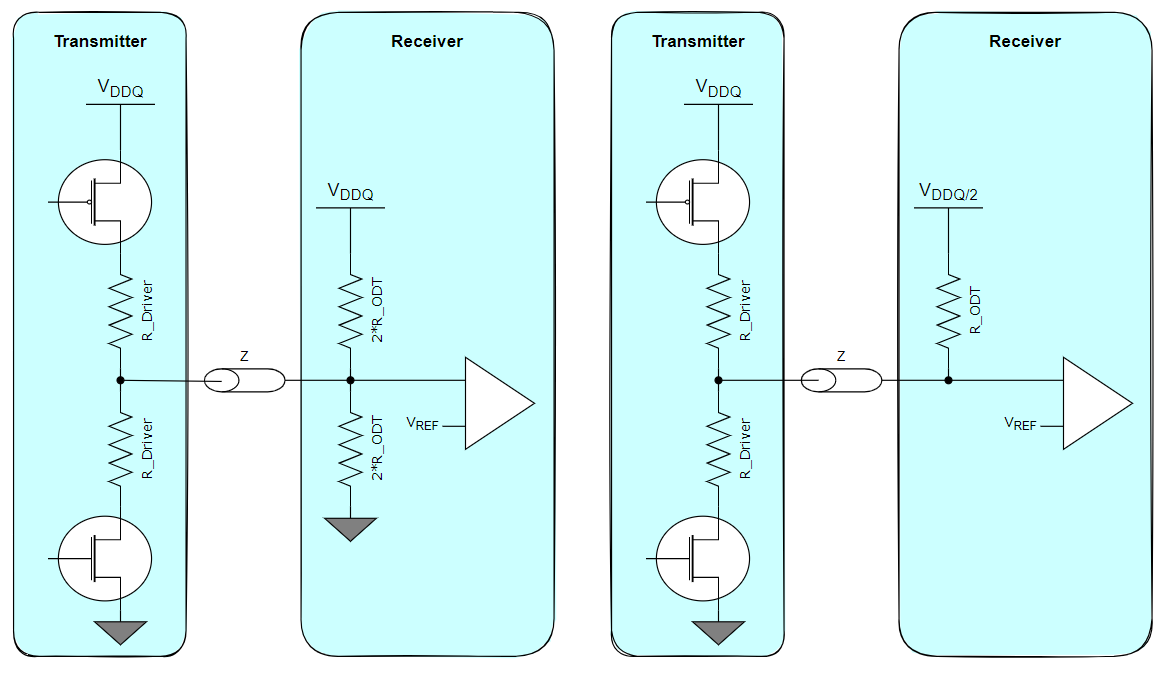

Вход у SSTL логики может быть подключен с помощью двух резисторов, один из которых к VDDQ, другой к GND или одного к VDDQ/2:

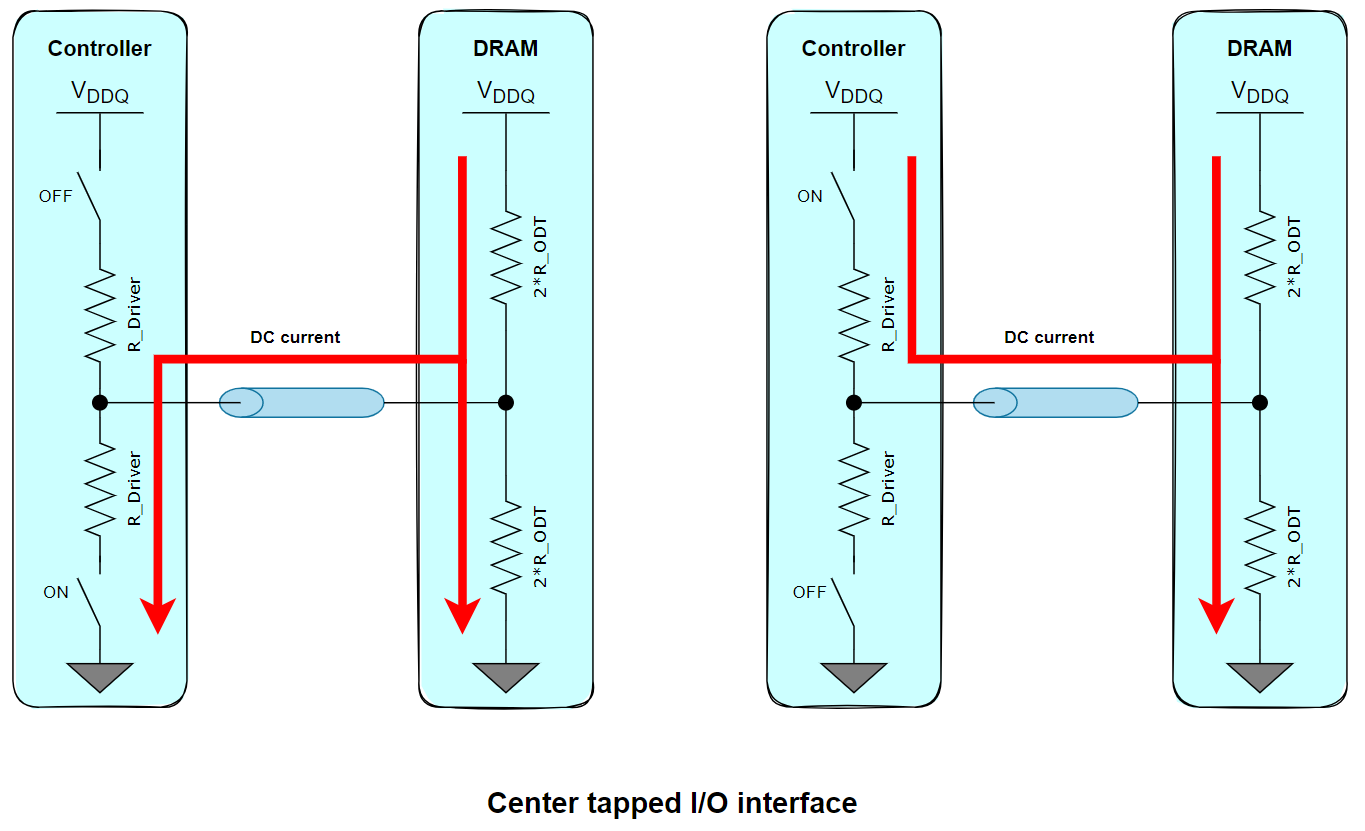

При переходе от DDR3 к DDR4 была изменена схема согласования на стороне нагрузки (приемника) от center tapped I/O interface к pseudo open drain (POD) I/O interface:

Это было сделано, чтобы уменьшить потребление тока. То есть при POD терминации Direct current (DC) возникает только при выставлении нуля драйвером. Вместе с этим была добавлена интересная функция – DBI (Data Bus Inversion). Она так же помогает уменьшить потребление – инвертирует данные, если к передаче на шину готовится байт данных, в котором присутствует больше нулей, чем единиц. То есть может быть максиму половина нулей на шине во время передачи данных. Как результат становится меньше шума в питании из-за меньшего количества портов, одновременно переходящих в состояние, когда протекает ток.

Пример преобразования данных, при использовании функции DBI:

Data from CORE | DM/DBI | BUS DATA (DQ) | |

1110 1010 | → | 1 | 1110 1010 |

1000 1000 | → | 0 | 0111 0111 |

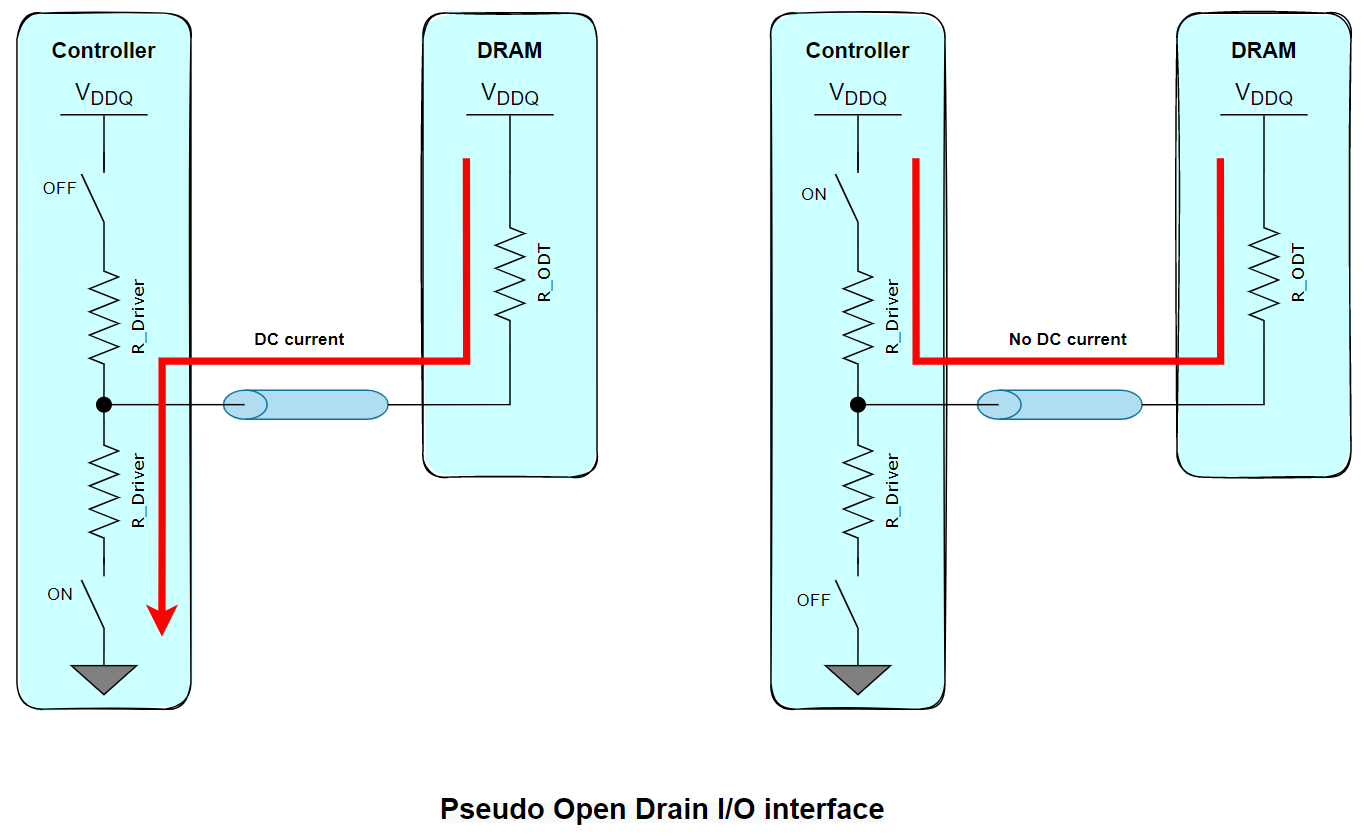

Из-за перехода к POD изменилась схема выбора Vref. Vref это опорное напряжение относительно которого определяются пороговые уровни для защелкивания 1 или 0. При DDR1-DDR3 это напряжение было фиксированным, независимо от выбранных значений ODT и равнялось половине напряжения VDDQ. В DDR4 необходимо его смещать, так как из-за получившегося делителя напряжения, уровень 0 меняется в зависимости от ODT резистора и импеданса драйвера. Это происходит во время так называемых тренингов в начале конфигурации.

R_ODT может выбираться из ряда: 34, 40, 48, 60, 80, 120, 240 Ом. Такой набор сопротивлений выбран в основном для того, чтобы можно было хорошо согласовывать линию, когда к одному контроллеру DDR подключается 2 планки памяти, но также и для уменьшения энергопотребления. Чем ниже выбранное значений ODT, тем выше расходуемая энергия.

R_Drive может выбираться из ряда: 34, 48 Ом. Эти импедансы относятся к SDRAM согласно стандарту, однако у контроллера, может быть, и другой набор этих значений.

Давайте рассмотрим так называемые «глазковые» диаграммы с разными значениями ODT. Схема моделирования упрощенная (R_driver=48 Ohms, line impedance=50 Ohms, ODT изменяются):

Результаты моделирования на 3200Mb:

С увеличением значения ODT размах «глаза» увеличивается, но и увеличивается его искажение, из-за возрастающей межсимвольной интерференции (Intersymbol interference - ISI) и отражений.

ISI связана с тем, что высокочастотный сигнал (последовательность бит 01010101) не успевает достичь номинального значения и при переключении состояния быстрее возвращается к противоположному значению, в отличии от низкочастотных последовательностей (00001111):

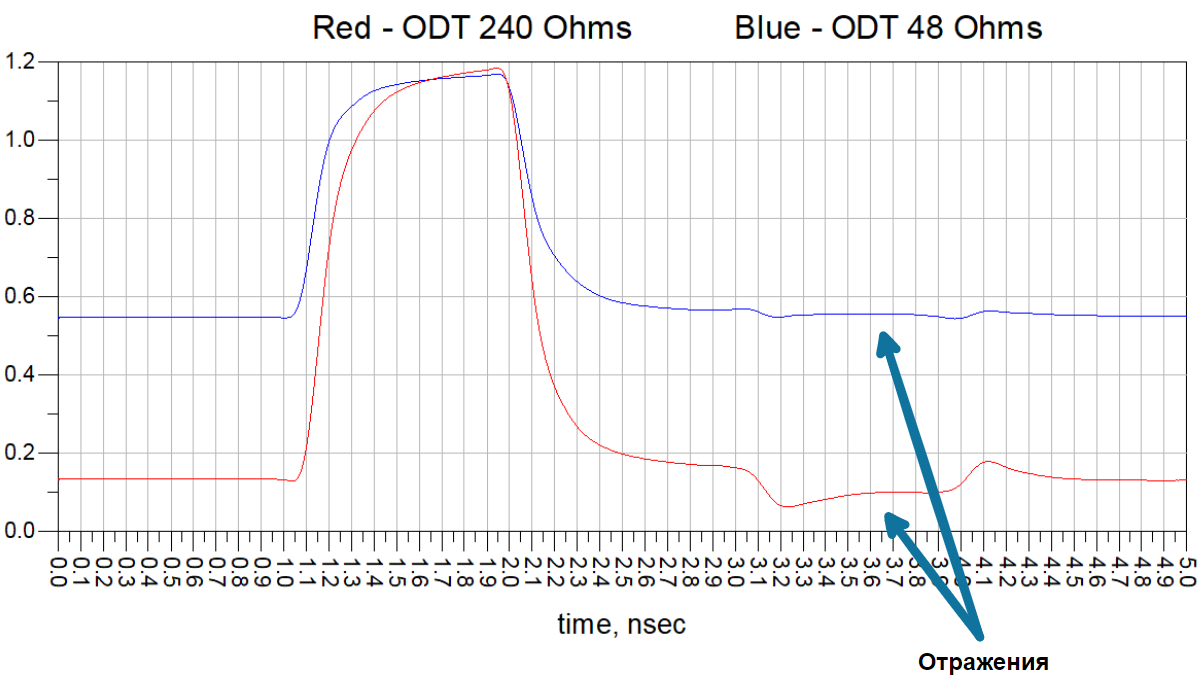

С увеличением сопротивления ODT увеличивается время нарастания сигнала, и увеличиваются отражения:

Отражения, которые присутствуют на линии с ODT=48 Ом скорее всего связанные с входной емкостью SDRAM, она вносит неоднородность в линию.

Теперь давайте рассмотрим разные конфигурации подключения памяти и основы их согласований для линий DATA и ADDR/CMD.

Согласование

Интерфейс DDR может иметь очень много разных вариантов подключений микросхем памяти к контроллеру, это необходимо для возможности подключения разных объемов памяти и разной ширины шины данных, то есть разного количество микросхем SDRAM.

Существуют следующие варианты:

Controller to 1 Chip on DQ, то есть 1 Rank

Controller to 2 Chip on DQ (с зеркальным расположением чипов), то есть 2 Rank

1DPC 1R - 1 DIMM (Dual In-line Memory Module) per Channel 1 Rank

1DPC 2R - 1 DIMM per Channel 2 Rank

2DPC 1R - 2 DIMM per Channel 1 Rank

2DPC 2R - 2 DIMM per Channel 2 Rank

DATA

Data Controller to Chip (1 Rank)

Это простое подключения, так как при таком подключении имеется самый “большой запас прочности”. Так, например самый сложный вариант — это когда к одной линии данных подключают 4-ре микросхемы памяти (2DPC с 2-Rank). Поэтому, в нашем случае, можно использовать хоть ODT - 240 Ом, это снизит потребление и нагрев. В такой топологии лучше больше внимание уделить перекрестным помехам.

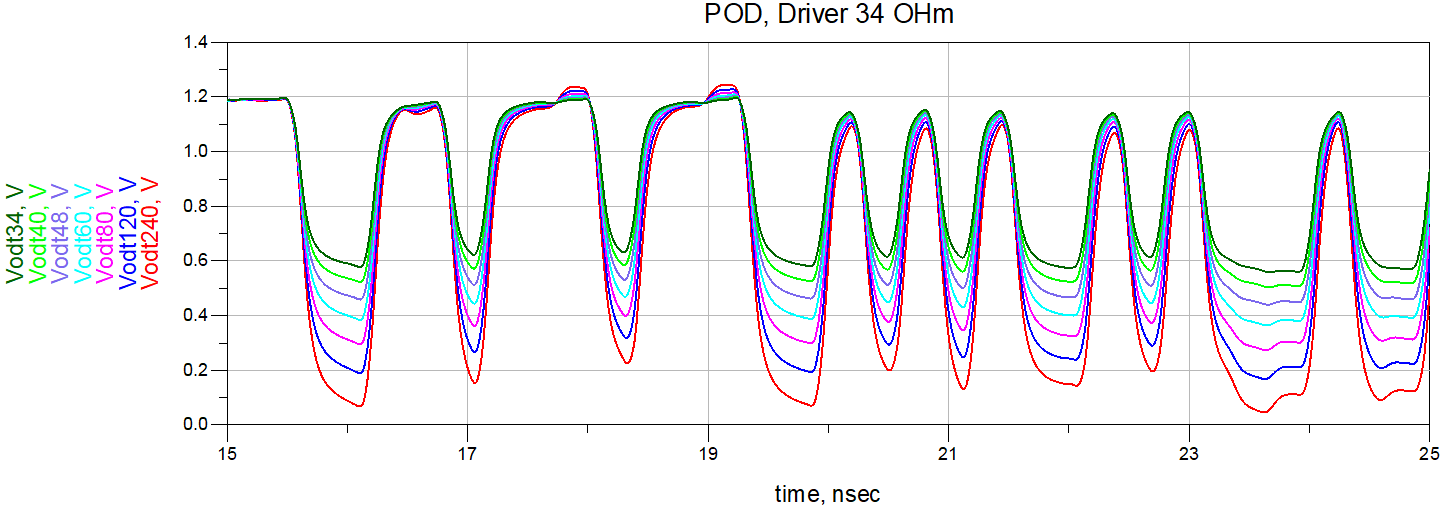

Но есть интересный момент что в линии с драйвером 34 Ом и линией 34 ом, jitter выше, чем с драйвером 34 Ом и линией 50 ом при различных вариантах ODT. Давайте разберемся из-за чего это происходит, и как сигнал формируется и отражается (мы это делаем с большими упрощениями для наглядности):

Так как используется POD можно считать, что изменения напряжения будут происходить относительно 1.2В.

Посмотрим на графики полученные при идеальных линиях, нагрузках и драйверах:

Графики сигналов, построенных с помощью IBIS моделей:

На передатчике: На приемнике:

Уровни отличаются от приведенных выше графиков, так как сами сопротивления могут отличаться от номинального значения в IBIS при различных условиях, а так же из-за паразитных параметров входов/выходов микросхемы.

Соотношение отраженного сигнала и полезного равно: 0.335В к 0.6В = 0.558 | Соотношение отраженного сигнала и полезного равно: 0.238В к 0.714В = 0.333 |

Из-за того, что уровень отражений выше (у варианта - драйвер 34 Ом, импеданс линии 34 Ом) они будут сильнее влиять на выходной ток драйвера, то есть разброс выходного тока при разных последовательностях данных и соответственно разных отражениях, будет больше. Это повлияет на скорость нарастания и спада выходного сигнала:

Синий график – длина линии равна половине длины волны сигнала. Красный график - длина линии равна четверти длины волны передаваемого сигнала. Так мы можем смоделировать ситуацию максимальных и минимальных отражений для сигнала.

По графикам видно, что разница в скорости нарастания тока у линии с импедансом 50 Ом меньше, чем у линии с импедансом 34 Ом. Именно поэтому jitter меньше с линией 50 Ом.

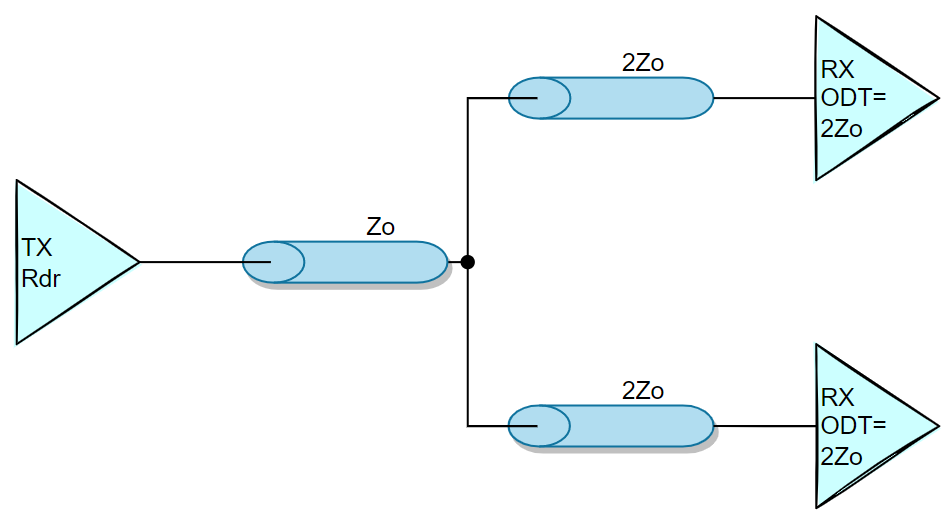

Data Controller to 2 Chip (2 Rank)

Этот вариант подключения, когда сигналы данных (DQx, DM, DQSx) подключаются параллельно к двум микросхемам SDRAM. И эти SDRAM работают по очереди, какая работает определяется сигналом chip select (CS). Легче всего на плате это реализовать установкой микросхем друг под другом (mirror). Подключение будет выглядеть следующим образом:

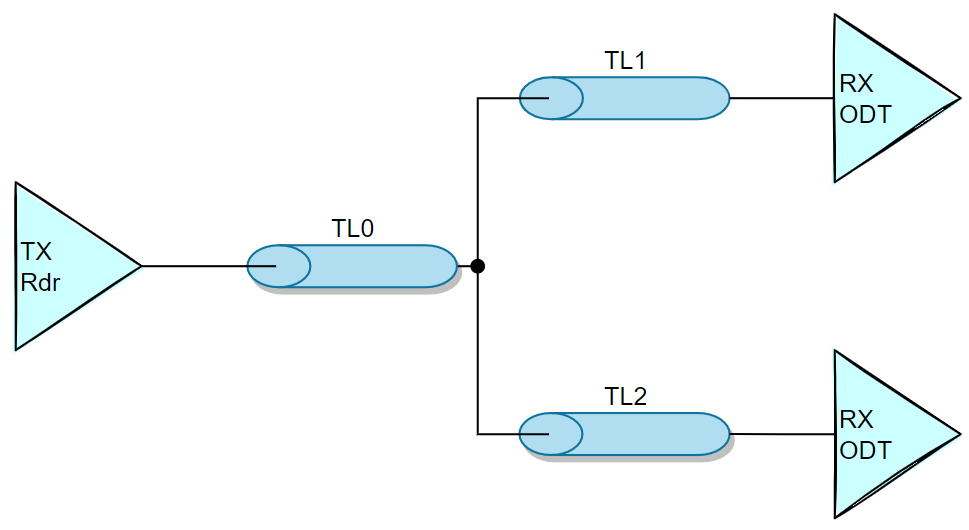

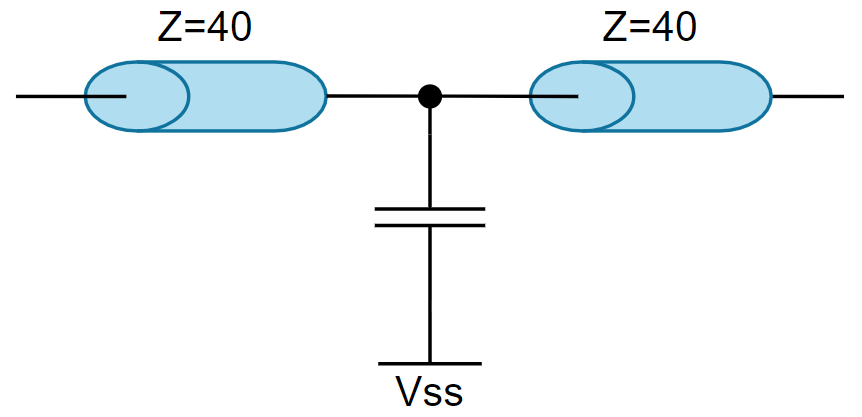

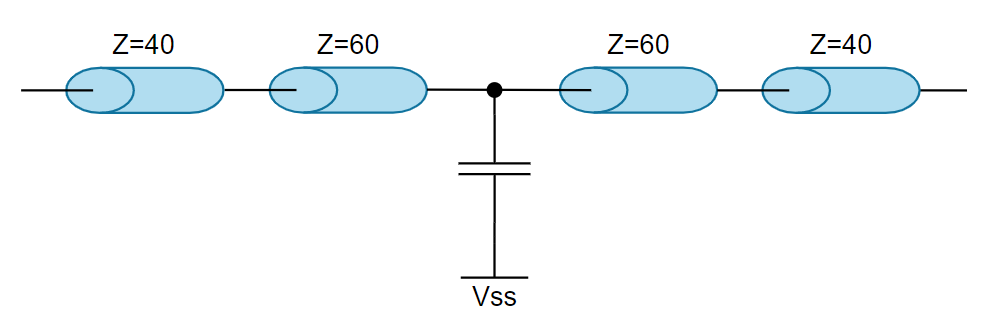

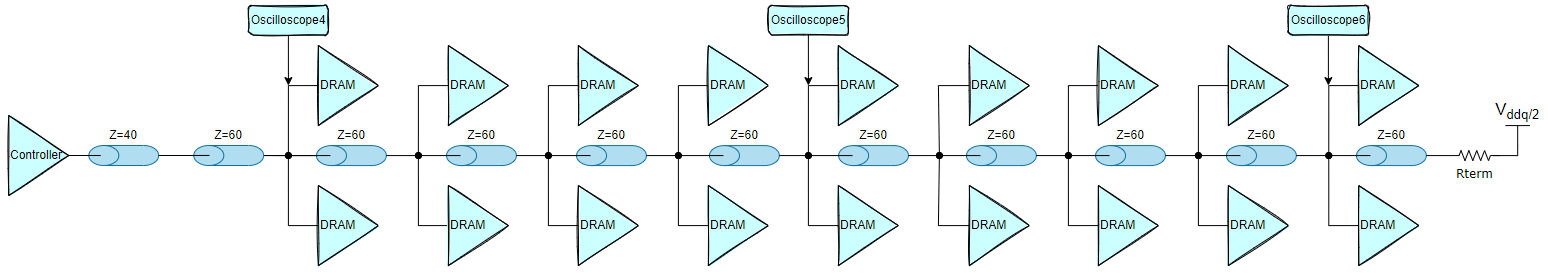

Обычно выбирают импеданс линий везде равным 50 ом. Но это плохой вариант согласования, так как будет возникать отражение в точке расхождения линий. Этого можно избежать, используя вот такой вариант топологии:

Но такой вариант очень сложно реализовать из-за сильно отличающихся линий по волновому сопротивлению. Но если мы сделаем хотя бы небольшую разницу это положительно повлияет на уменьшение отражений. Например, мы можем сделать трассу до разветвлений 40 ом (TL0), а трассы до чипов по 60 ом (TL1, TL2). При этом ODT так же сильно влияет на итоговый eye, так как получается параллельное подключение двух ODT и при выборе маленького значения, например 48 Ом, раскрытие глаза сильно сузится по высоте.

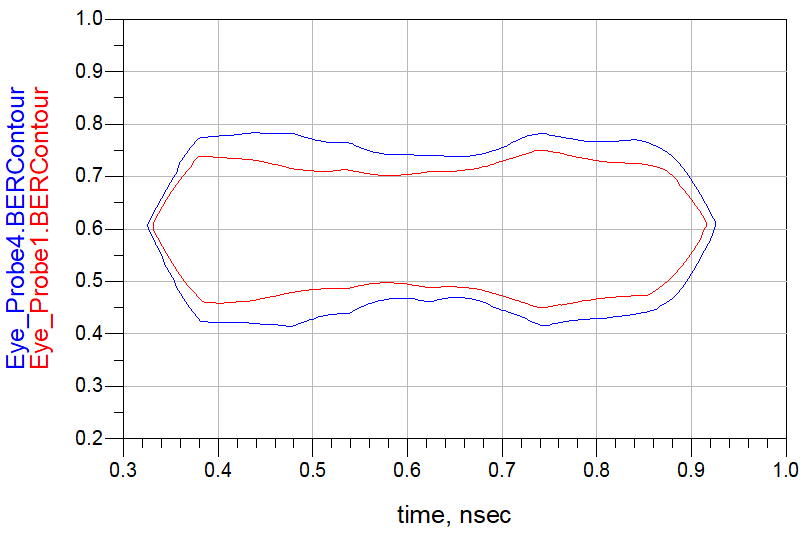

Вот пример двух топологий, их eye диаграмм и какая получается разница:

Видно, что есть заметный эффект. Хоть тут и большой запас у обоих вариантов, но с учетом перекрестных помех, а также из-за шума по питанию, «глаз» еще закроется. Поэтому это улучшение может быть полезным.

На раскрытие глаза так же влияет длина участка от точки расхождения линий до чипа, поэтому это более актуально для таких вариантов подключения как 2DPC. Но там применяются еще и другие варианты для уменьшения отражений, они будут рассмотрены дальше.

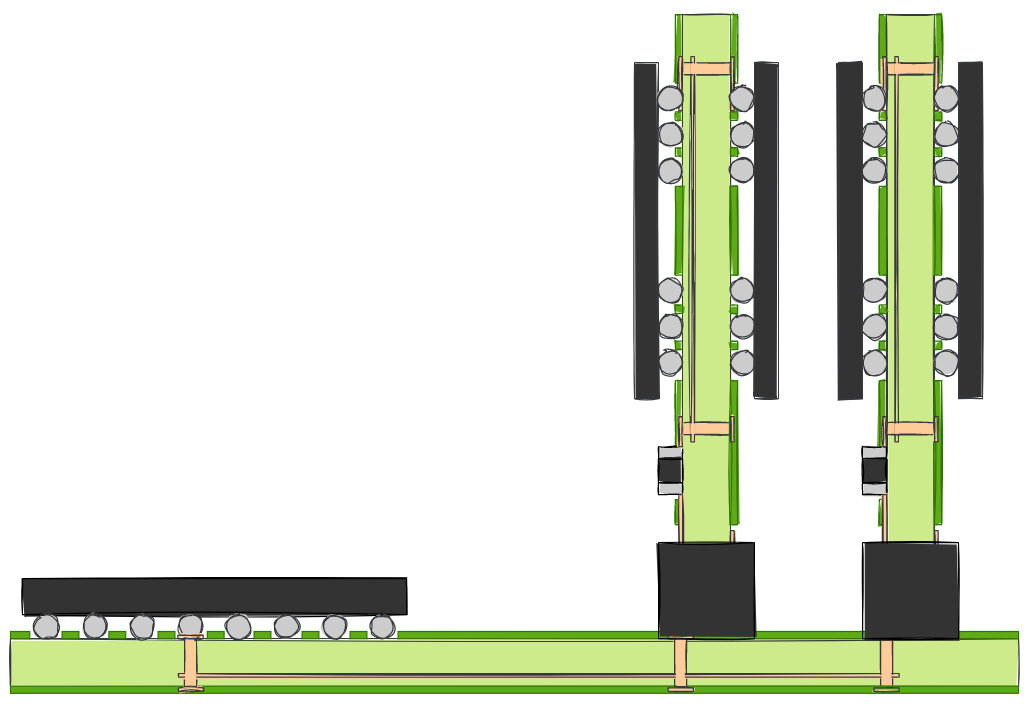

Data 1DPC (1 Rank)

Давайте рассмотрим схему подключения данных с 1DPC (1 Rank):

Здесь Slot 1 — это модуль памяти DIMM (Dual In-line Memory Module) имеющий 1 Rank.

Rstub это резистор 15 Ом, который размещается на плашках памяти, для чего он нужен рассмотрим в дальнейшем.

TL1 - трасса на печатной плате модуля памяти, имеющая импеданс 50 Ом. Поэтому если применяется только один slot на плате рекомендуется использовать TL0 импедансом в 50 Ом.

Вариант с драйвером 34 ом тут работает лучше, чем с 48 ом, так как обеспечивает большее раскрытие глазковой диаграммы. Рассмотрим несколько вариантов для наглядности:

Из интересного стоит отметить, что Rstub резистор уменьшает раскрытие глазковой диаграммы, но так как модули памяти делаются стандартными, он присутствует на всех модулях. Он помогает улучшить SI при использовании 2DPC.

Увеличение значение ODT терминирующего резистора, будет увеличивать раскрытие глазковой диаграммы и уменьшать ток потребления.

Data 1DPC (2 Rank)

Давайте рассмотрим схему подключения данных для 1DPC (2 Rank):

Здесь Slot 1 — это модуль памяти DIMM имеющий 2 Rank.

Rstub это резистор 15 Ом, который размещается на плашках памяти.

TL1, TL2 - трассы на печатной плате модуля памяти, имеющая импеданс 50 Ом. Поэтому если применяется только один slot на плате рекомендуется использовать TL0 импедансом в 50 Ом.

Вариант с драйвером 34 ом тут работает так же лучше, чем с 48 ом, так как обеспечивает большее раскрытие глазковой диаграммы. Рассмотри несколько вариантов для наглядности:

Видно что при переходе к ODT 240 Ом выйгрыша уже не наблюдается, но при этом увеличивается jitter и overshoot, а так же трасса больше подвержена перекрестной помехе.

Data 2DPC (1 Rank)

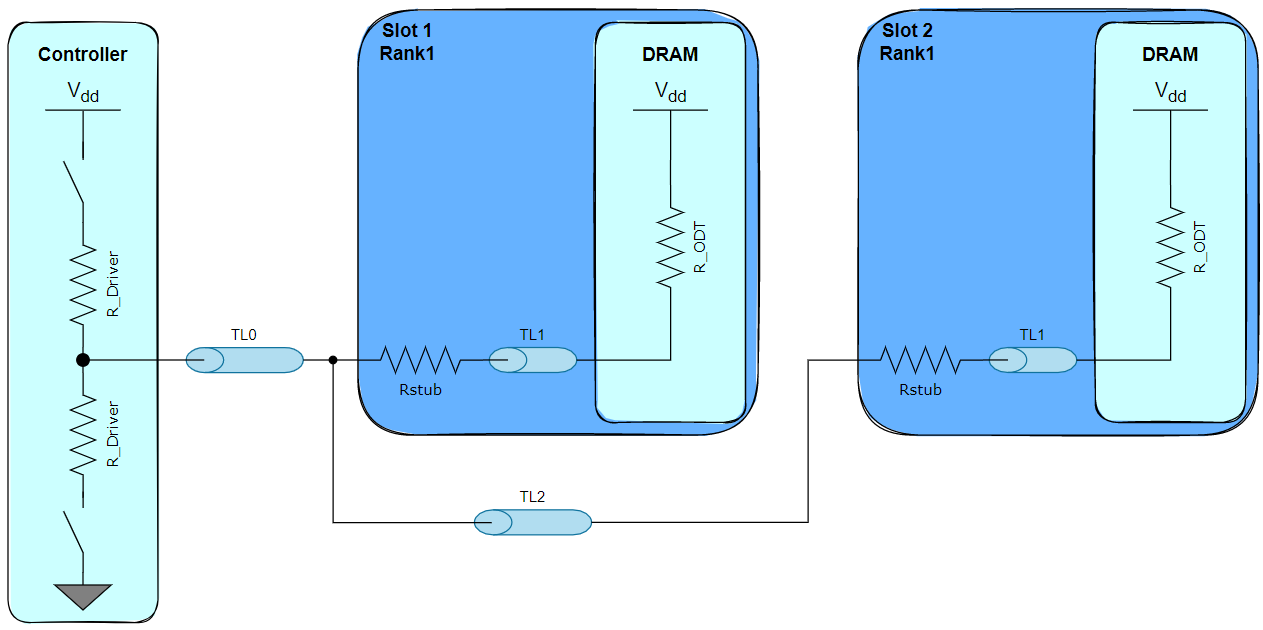

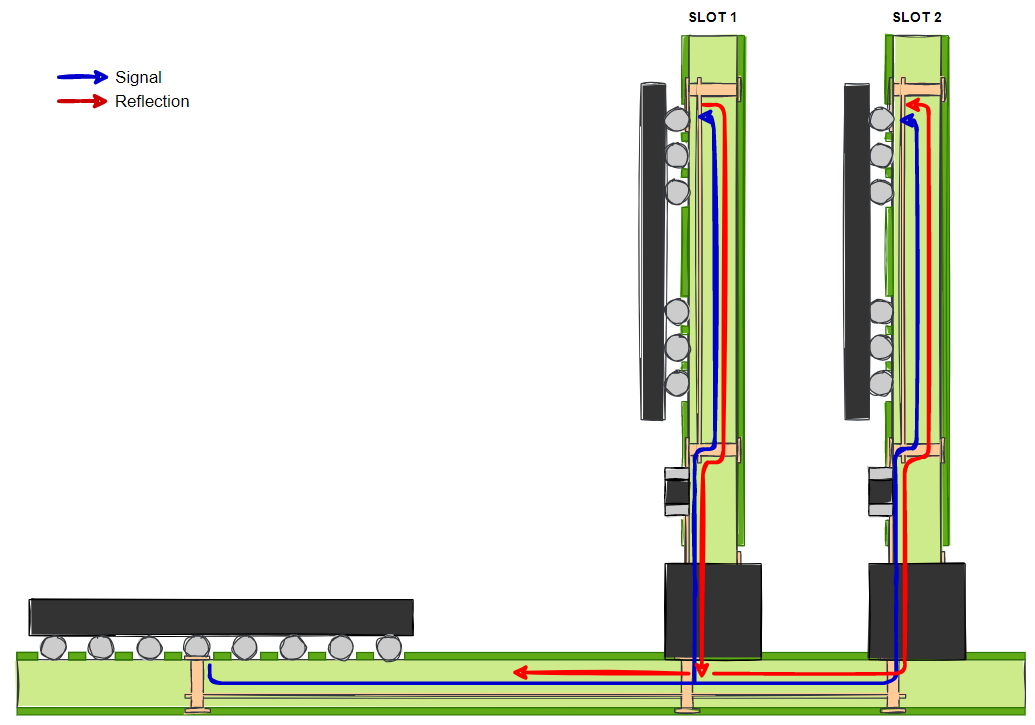

Давайте рассмотрим схему подключения данных для 2DPC (1 Rank):

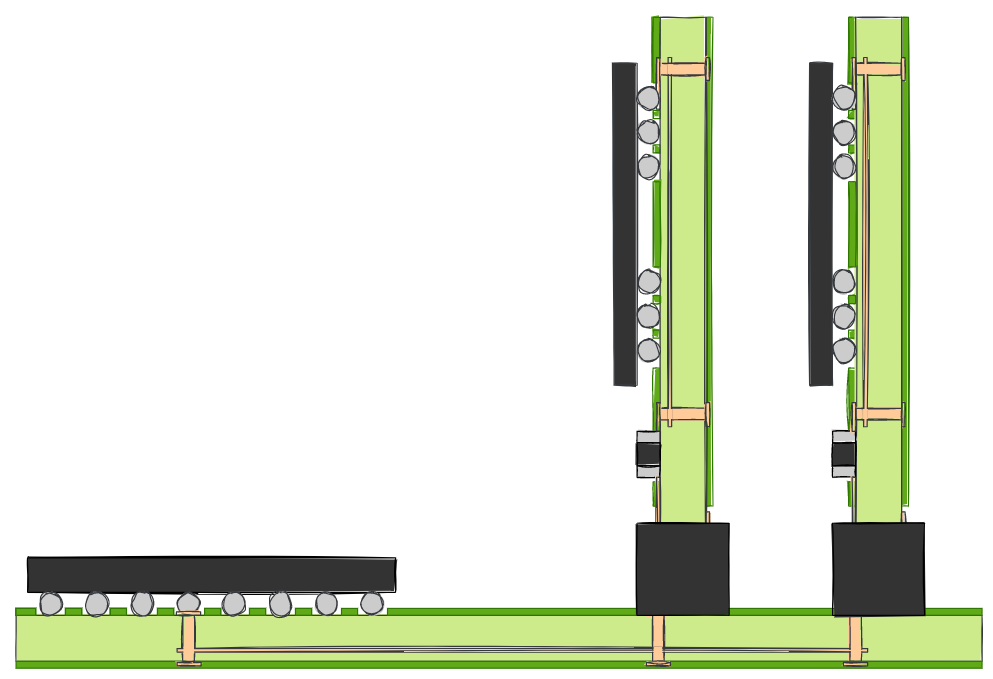

Пример участка топологии в зоне разъемов:

Здесь Slot 1,2 — это модули памяти DIMM имеющие 1 Rank.

Rstub это резистор 15 Ом, который размещается на плашках памяти.

TL1 - трассы на печатной плате модуля памяти, имеющие импеданс 50 Ом.

Этот вариант, когда к одному контроллеру подключается два модуля памяти DIMM c 1 Rank каждый. Главная проблема в такой топологии заключается в том, что если сигнал пишется в какую-то из DIMM, например в slot 2, то он будет там искажен в связи с тем, что часть сигнала отразится от slot 1 и придет в slot 2:

Есть возможность уменьшить это отражение. Этого можно добиться включением ODT=48 Ом в slot 1, это избавит нас от отражения на этом конце линии. При использовании в slot 2 так же ODT=48 Ом, сильно уменьшит раскрытие глазковой диаграммы, так как будет включено два ODT по 48 Ом в параллель. Но так как нам не страшно что от slot-а в который мы пишем будут отражения, так как они практически не повлияют на качества сигнала в этом slot-е, то лучше всего для slot 2 использовать терминацию высокого сопротивления:

Очень низкий запас с учетом того, что было много упрощений при моделировании.

Такая терминация заметно лучше повлияла на раскрытие глазковой диаграммы.

Все то же самое относится и к чтению из памяти:

Видно, что при таких комбинациях ODT запас получается больше. Так же наглядно видно и то, что 240 Ом применять не целесообразно из-за overshoot и возросшего jitter.

Еще один способ улучшить SI, это уменьшить импеданс линии данных до разъема, для уменьшения отражений в точке распараллеливания. Рассматривали выше:

Так как на модуле памяти импеданс фиксирован 50 омами, мы можем уменьшить только импеданс до разъема.

Видно, что увеличение раскрытия глазковой диаграммы произошло примерно на 55мв по высоте.

Следующее улучшение, которое мы можем сделать это симметричное подключение разъемов:

или такой вариант:

Правый вариант дает еще примерно +35мВ по высоте.

Чтение из памяти:

При чтении так же видно преимущество от такой топологии.

Rstub:

Теперь пришло время разобраться для чего используется Rstub.

Rstub это резистор который расположен на модуле DIMM максимально близко к краевому разъему:

Этот резистор, на первый взгляд, может показаться что является последовательным терминирующим резистором для SDRAM, но в нем нет необходимости, так как внутреннее сопротивление драйвера может быть как 34 ом, так и 48 ом. Он служит для подавления отражений от неиспользуемых в данный момент модулей в multi-DIMM конфигурациях и соответственно улучшения качества сигналов (хорошо подавляет overshoot и уменьшает jitter). Значение этого резистора 15 ом и совместно с ODT=34 ом, получится хорошее согласование на конце линии.

Запись:

Выше overshoot и jitter.

У левого варианта чуть меньше overshoot и jitter, но зато у правого больше раскрытие глазковой диаграммы.

Чтение:

На чтении особенно хорошо видно увеличение overshoot и jitter, хотя раскрытие глазковой диаграммы практически идентичны.

На чтении особенно хорошо видно увеличение overshoot и jitter.

Data 2DPC (2 Rank)

Давайте рассмотрим схему подключения данных для 2DPC (2 Rank):

Здесь Slot 1,2 — это модули памяти DIMM имеющие 2 Rank.

Rstub это резистор 15 Ом, который размещается на плашках памяти.

TL1 - трассы на печатной плате модуля памяти, имеющая импеданс 50 Ом.

Этот вариант, когда к одному контроллеру подключается два модуля памяти DIMM c 2 Rank каждый. Главная проблема в такой топологии остается такой же, как и в варианте 2DPC (1 Rank) и заключается в том, что если сигнал пишется в какую то из DIMM (например slot 2), то он будет там искажен из-за того что часть сигнала отразится от slot 1 и придет в slot 2:

Варианты улучшения качества сигнала точно такие же как были озвучены выше.

Ниже приведем примеры согласований линий данных в зависимости от количества модулей, rank и происходит запись или чтение:

SDRAM ODT Matrix for Writes:

Slot 1 | Slot 2 | Write To | Controller Driver | Slot 1 | Slot 2 | ||

Rank 1 | Rank 2 | Rank 1 | Rank 2 | ||||

DR | DR | Slot 1 | 34 or 48 | 120 ohm | ODT off | ODT off | 34-ohm |

Slot 2 | 34 or 48 | ODT off | 34-ohm | 120 ohm | ODT off | ||

SR | SR | Slot 1 | 34 or 48 | 120 ohm |

| 34-ohm |

|

Slot 2 | 34 or 48 | 34-ohm |

| 120 ohm |

| ||

DR | Empty | Slot 1 | 34 or 48 | 120 ohm | ODT off |

|

|

Empty | DR | Slot 2 | 34 or 48 |

|

| 120 ohm | ODT off |

SR | Empty | Slot 1 | 34 or 48 | 120 ohm |

|

|

|

Empty | SR | Slot 2 | 34 or 48 |

|

| 120 ohm |

|

SR: single-ranked DIMM;

DR: dual-ranked DIMM.

SDRAM ODT Matrix for Reads:

Slot 1 | Slot 2 | Read From | SDRAM Driver | Slot 1 | Slot 2 | ||

Rank 1 | Rank 2 | Rank 1 | Rank 2 | ||||

DR | DR | Slot 1 | 34 or 48 | ODT off | ODT off | ODT off | 34-ohm |

Slot 2 | 34 or 48 | ODT off | 34-ohm | ODT off | ODT off | ||

SR | SR | Slot 1 | 34 or 48 | ODT off |

| 34-ohm |

|

Slot 2 | 34 or 48 | 34-ohm |

| ODT off |

| ||

DR | Empty | Slot 1 | 34 or 48 | ODT off | ODT off |

|

|

Empty | DR | Slot 2 | 34 or 48 |

|

| ODT off | ODT off |

SR | Empty | Slot 1 | 34 or 48 | ODT off |

|

|

|

Empty | SR | Slot 2 | 34 or 48 |

|

| ODT off |

|

SR: single-ranked DIMM;

DR: dual-ranked DIMM

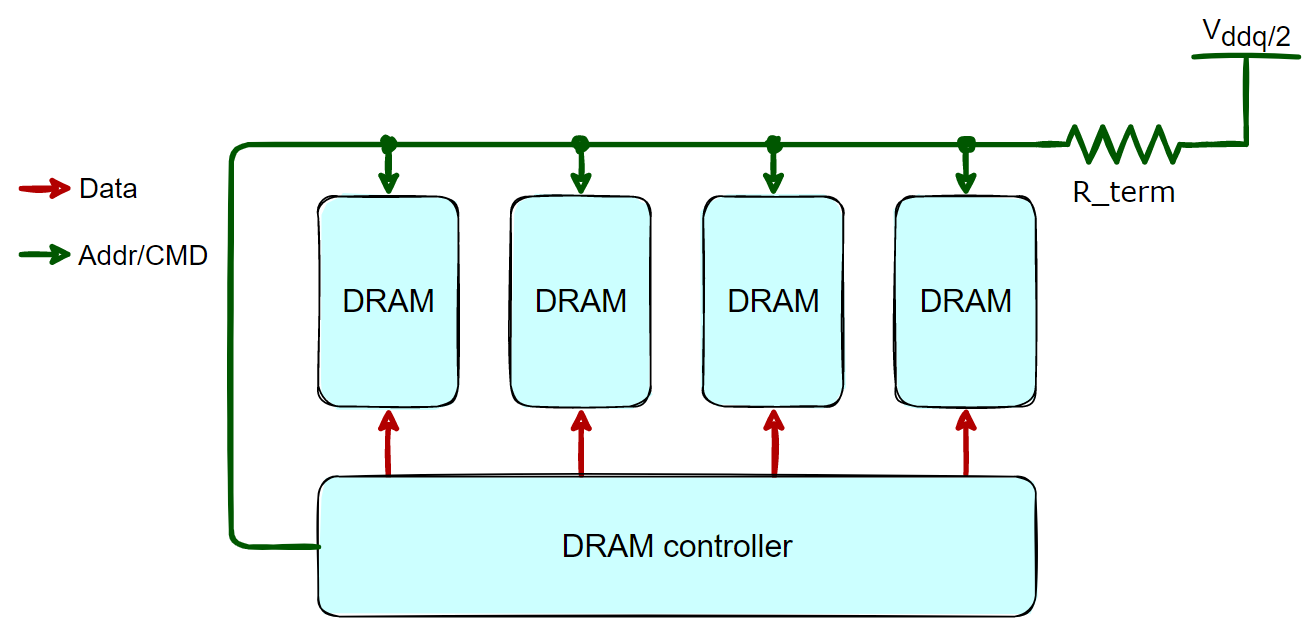

ADDR/CMD

ADDR/CMD общее

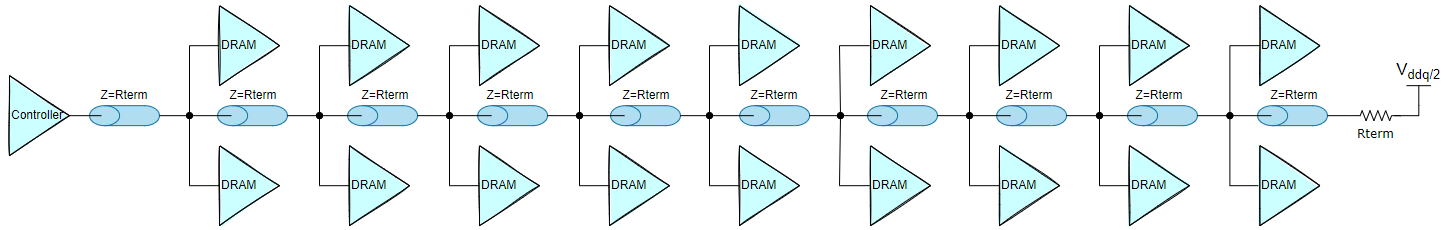

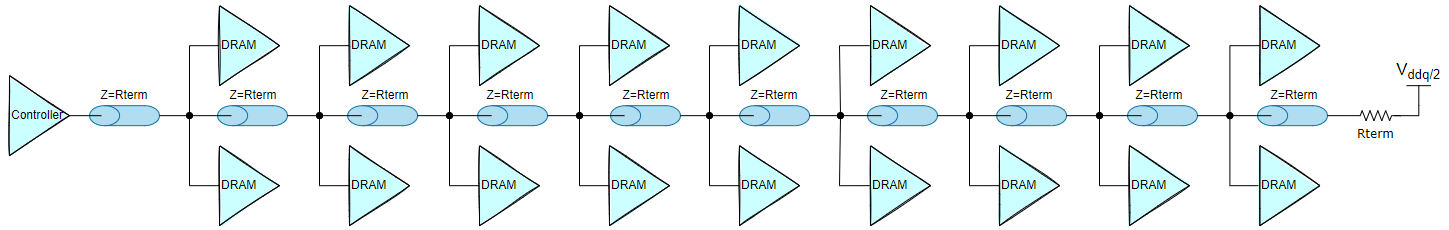

В DDR3/4 используется Fly-By топология для адресов и команд, с минимально возможными стабами до памяти и с терминацией на конце линии (так как эти сигналы не имеют внутреннего ODT):

R_term может быть в широком диапазоне значений, в модулях памяти R_term обычно в районе 40 Ом.

В модулях памяти UDIMM одна линия адресов/команд может подключаться к 9 микросхемам памяти (если используется ECC) в случае одного ранга и к 18 микросхемам в случае двух рангов:

А если будет использоваться 2 slot, то максимально возможно, что одна линия будет подключена к 36 микросхемам и терменирована на обоих модулях памяти. Таким образом линии адресов/команд подключаются на большую нагрузку.

Например, в RDIMM памяти уже может быть до 36 микросхем (если используются SDRAM в

которых по 4х bit data) в одном модуле и поэтому там используют уже буфер на адресах, что улучшает качество сигнала:

Терминирующий резистор нужен на конце линии что бы не возникало отражение, которое может сильно исказить сигнал на остальных микросхемах:

Так как каждая линия ADDR/CMD может подключаться к большому количеству микросхем стоит уделить пристальное внимание к однородности линии, что бы по ее пути не возникало отражений.

ADDR/CMD 1 Chip

Я встречал много дизайнов, где используя одну микросхему SDRAM применяют терминацию на конце линии, но это не обязательно. Это становится обязательным при использовании 2х микросхем и больше (причем на дальней микросхеме сигнал хороший):

Сигнал имеет хорошую форму без использования терминации. | Сигнал, отразившись от конца линии, исказил сигнал на DRAM которая ближе к контроллеру. Хоть сигнал возможно и попадает в маску, но он уже очень сильно искажен, и перекрестная помеха или шумы по питанию могут привести к неработоспособности интерфейса. |

ADDR/CMD 9 Chips

При разводке адресов и команд особенно важно, чтобы импеданс был постоянным и соответствовал R_term на всем пути следования сигнала. Иначе будут возникать отражения, вызывающие значительные искажения сигнала на SDRAMs. Но это сложно обеспечить, так как в Fly-By топологии у линии по пути много неоднородностей импеданса, таких как Via и емкостная нагрузка SDRAMs чипов.

Давайте рассмотрим вариант с следующим подключением:

Rterm=40 Ом

TDR:

Видно, что импеданс падает ниже Rterm, это как раз связано с входными емкостями SDRAMs чипов, которые распределены вдоль линии адресов.

Eye diagrams:

Самое хорошее раскрытие глазковой диаграммы на дальней микросхеме около терминирующего резистора. Это связано с тем, что входная емкость SDRAM, создает отражение сигнала, распространяющийся в обратном направлении.

Схемотехнически входную емкость SDRAM в линии адресов, можно представить следующим образом:

TDR такой схемы будет выглядеть:

Ослабить влияние этой неоднородности (емкости), можно с помощью компенсирующей неоднородности (индуктивности). Одна неоднородность скомпенсирует другую. То есть изменив ширину линии (увеличив ее импеданс) с обоих сторон от емкости, компенсируется ее неоднородность. Отраженный от емкостной неоднородности сигнал отрицательной полярности нейтрализуется сигналом положительной полярности, отраженным узким участком дорожки.

Это будет выглядеть следующим образом:

TDR:

Увеличение импеданса, позволяет уменьшить высоту отраженного сигнала при условии, что время нарастания или спада фронта набегающего сигнала превышает величину эффективной задержки, создаваемой скорректированным участком линии. L-comp, например основан на том же принципе:

Чем выше импеданс (уже проводник), по отношению к Z=Rterm тем более короткий участок скорректированного участка можно достичь, и тем самым меньше скачок импеданса будет. В UDIMM модулях, например дорожка между SDRAMs чипами равна 0,075мм, а в широком месте 0,15мм.

Именно такой способ уменьшения неоднородностей применяется в UDIMM модулях:

TDR:

Видно, что импеданс остается в районе Rterm(40 Ом).

Eye diagrams:

Видно, что раскрытие глазковой диаграммы заметно улучшилось по сравнению с прошлым случаем. Вот, например контур глазковой диаграммы с наихудшим случаем у обоих вариантов (первая микросхема):

Улучшение на ~30%

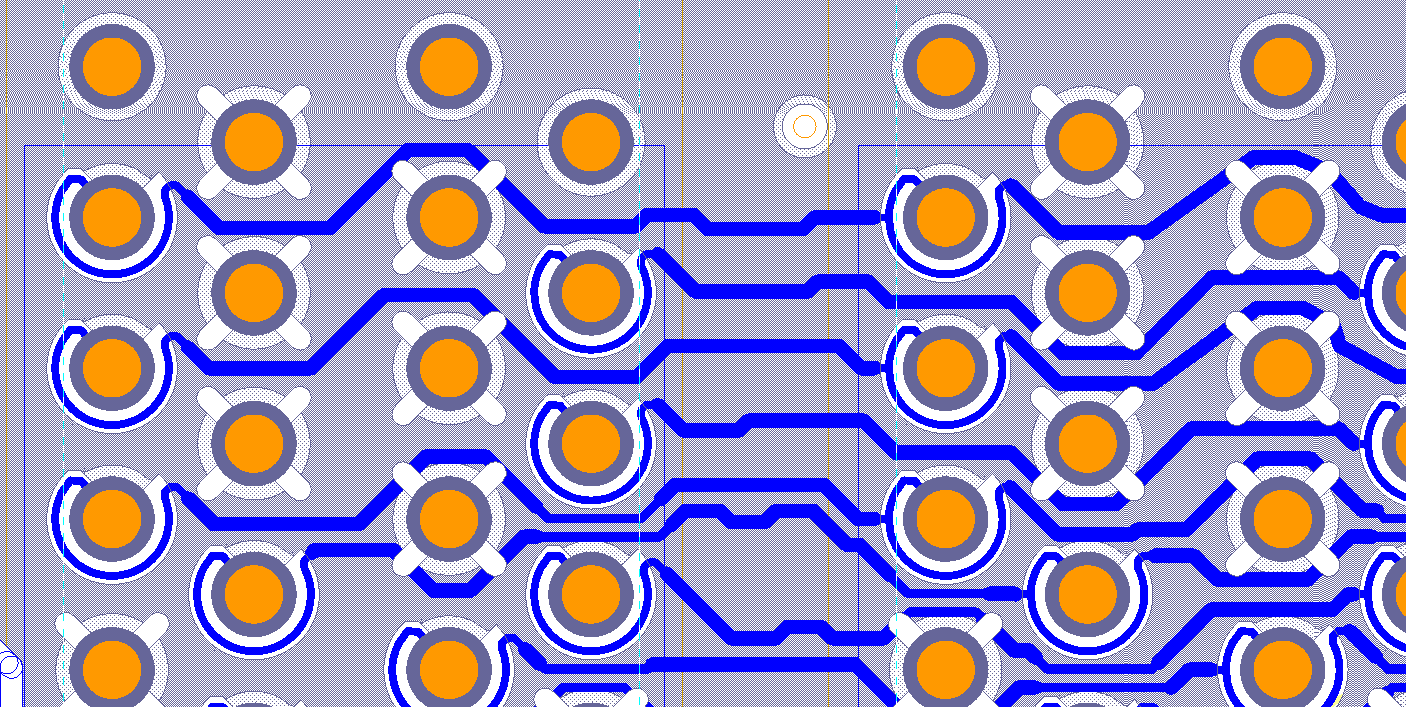

Давайте теперь попробуем разобраться какое влияние вносит via. В предыдущей конфигурации для подключения SDRAM чипов на шине адресов использовалась следующая структура межслойных подключений:

Так обычно разведены модули памяти UDIMM, при такой топологии требуется минимальное количество слоев. У такой via преобладает емкостная характеристика и она добавляется к входной емкости SDRAM, поэтому требуется такая большая разница в импедансе для ослабления этих неоднородностей.

Можно использовать вот такое подключение:

При таком подключении уже присутствует индуктивность, из-за которой требуется меньшая разница в импедансе для выравнивания TDR.

Давайте рассмотрим подключение с такими via, при Rterm=40 Ом:

TDR:

С таким via видно, что TDR заметно выше стало в сравнении с первым вариантом межслойных подключений, тем самым потребуется меньшая разница импедансов для компенсации этих неоднородностей.

Таким образом каждый случай в топологии уникальный и нужно подбирать параметры трасс, via и расположения сигнальных слоев. Тут можно только порекомендовать делать подключения однотипные по всем адресам, что облегчит подбор параметров топологии. Вот пример топологии, где из-за плотности были сделаны подключения разнотипные (тут один ранг, часть микросхем на top, часть на bottom):

Для такой топологии очень сложно и трудоемко спроектировать структуры для компенсации неоднородностей.

TDR этой линии выглядит следующим образом:

Мы можем наблюдать очень большое количество неоднородностей на TDR, которые вызывают отражения.

Как вы могли убедиться из этой статьи, что интерфейс DDR4 SDRAM весьма нетривиальная вещь с точки зрения SI. Инженеры, которые его развивали, проделали большой труд, чтобы с каждой новой версией интерфейса повышать скорость его работы. А я в свою очередь постараюсь в следующих статьях рассказать вам о не менее важных вещах при трассировке SDRAM, таких как выравнивание сигналов и перекрестные помехи.

P.S. Это моя первая статья и она не легко мне давалась, немного волнуясь надеюсь что она вам понравится 😊