В настоящее время существует не так уж и много open-source САПР. Тем не менее, среди САПР для электроники (EDA) есть весьма достойные продукты. Этот пост будет посвящён моделировщику электронных схем с открытым исходным кодом Qucs. Qucs написан на С++ с использованием фреймворка Qt4. Qucs является кроссплатформенным и выпущен для ОС Linux, Windows и MacOS.

Разработку данной САПР начали в 2004 году немцы Michael Margraf и Stefan Jahn (в настоящее время не активны). Сейчас Qucs разрабатывается интернациональной командой, в которую вхожу и я. Руководителями проекта являются Frans Schreuder и Guilherme Torri. Под катом будет рассказано о ключевых возможностях нашего моделировщика схем, его преимуществах и недостатках по сравнению с аналогами.

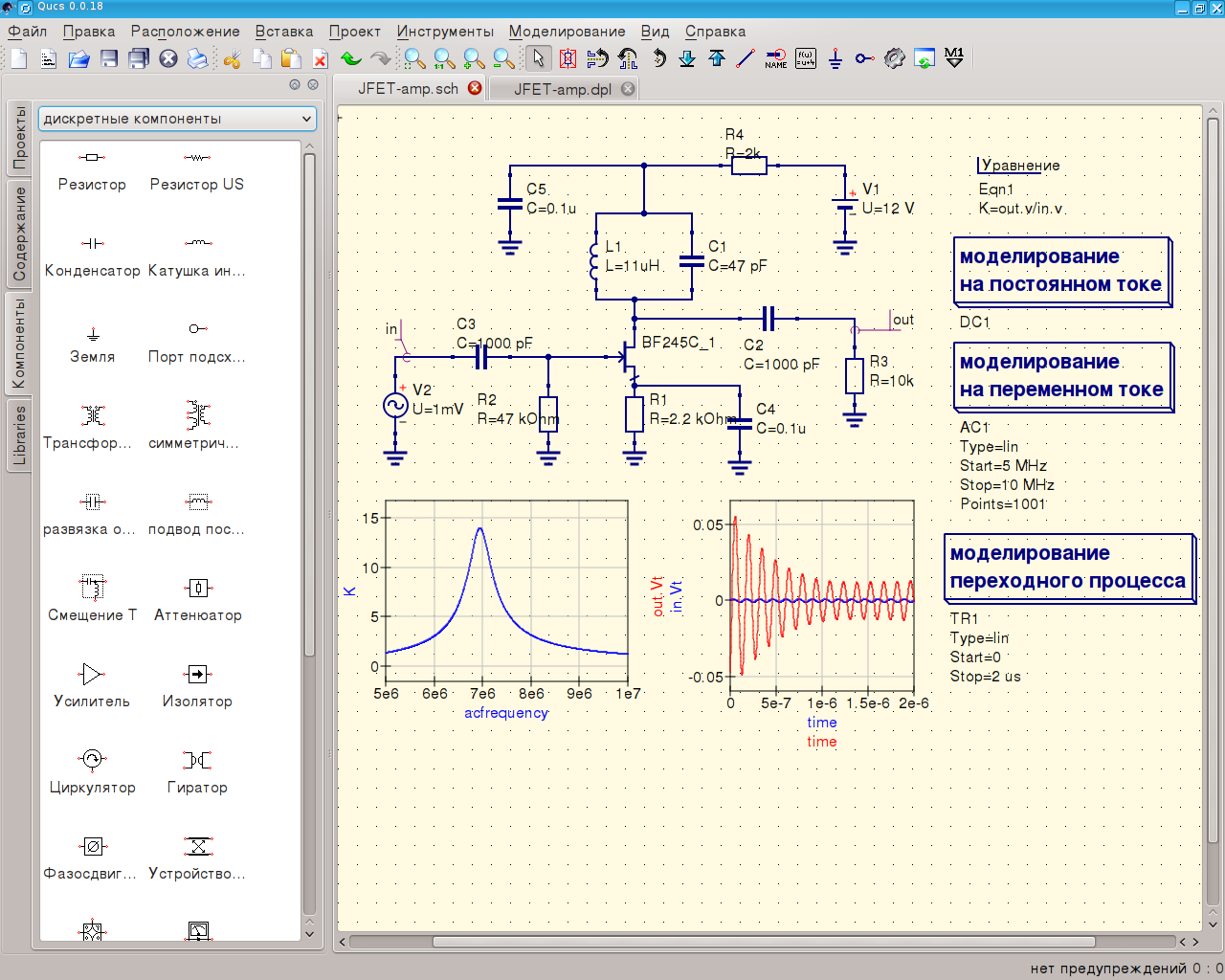

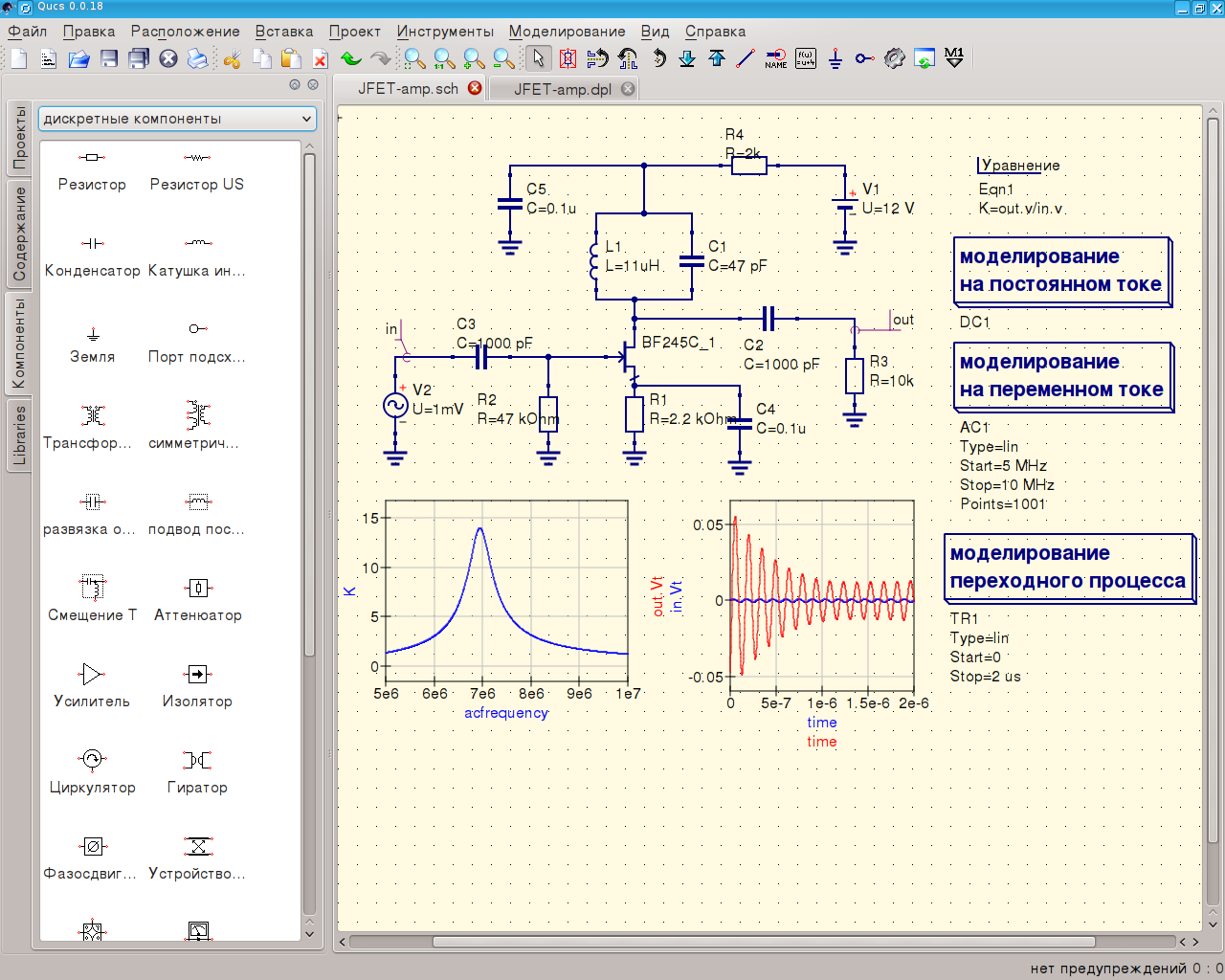

Главное окно программы показано на скриншоте. Там смоделирован резонансный усилитель на полевом транзисторе и получены осциллограммы напряжения на входе и выходе и также АЧХ.

Как видно, интерфейс интуитивно понятен. Центральную часть окна занимает собственно моделируемая схема. Компоненты размещаются на схеме методом перетаскивания из левой части окна. Виды моделирования и уравнения также являются особыми компонентами. Более подробно принципы редактирования схем описаны в документации к программе.

Формат схемного файла Qucs основан на XML и к нему поставляется документация. Поэтому схема Qucs может быть легко сгенерирована сторонними программами. Это позволяет создавать ПО для синтеза схем, которое является расширением Qucs. Проприетарное ПО как правило использует бинарные форматы.

Перечислим основные компоненты, имеющиеся в Qucs:

Библиотека компонентов использует собственный формат, основанный на XML. Но можно импортировать существующие библиотеки компонентов, основанные на Spice (приводятся в даташитах на электронные компоненты).

Поддерживаются следующие виды моделирования:

Результаты моделирования можно экспортировать в Octave/Matlab и выполнить там постобработку данных.

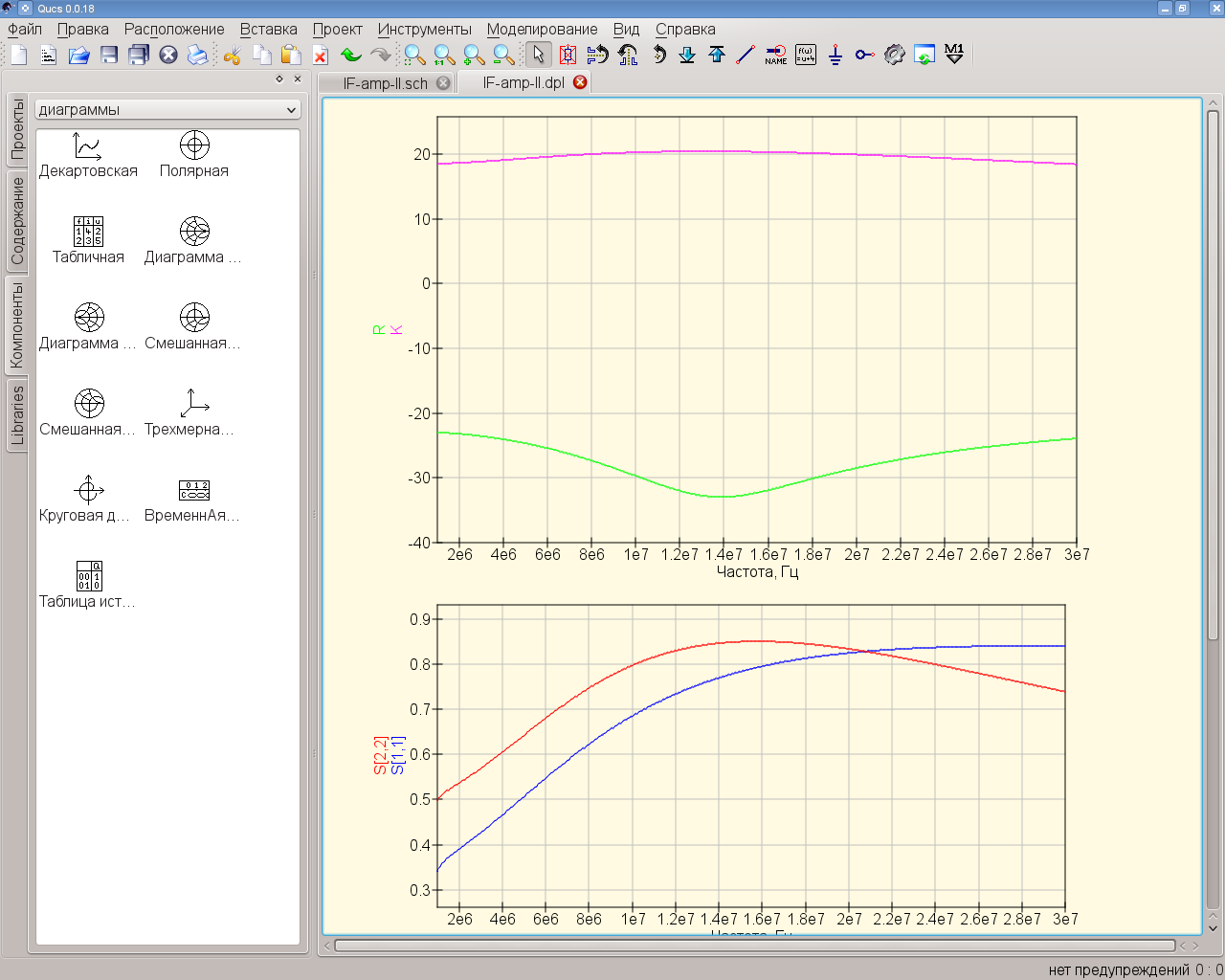

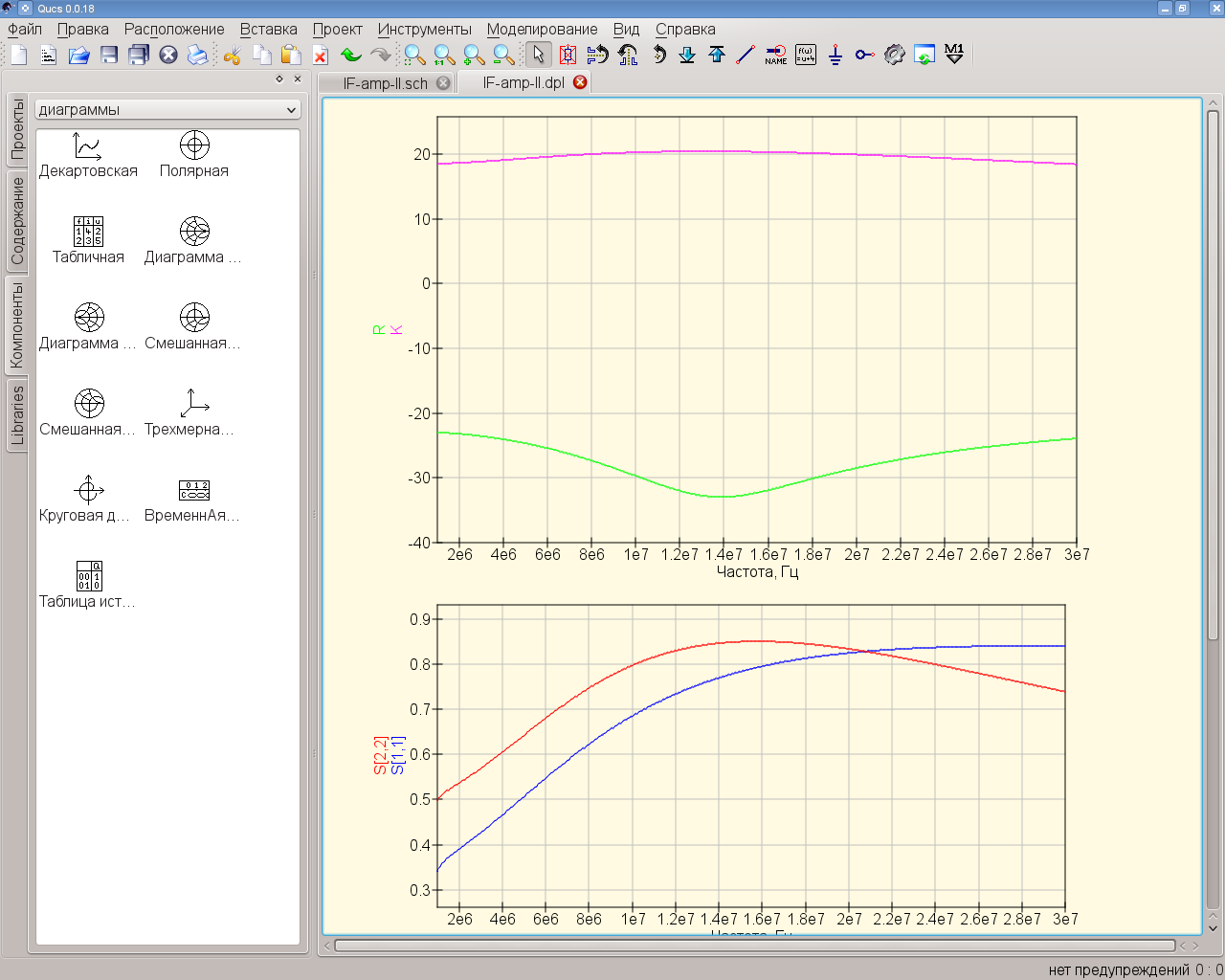

Qucs основан на вновь разработанном движке схемотехнического моделирования. Отличительной особенностью этого движка является встроенная возможность моделирования S-параметров и КСВ, что важно для анализа ВЧ-схем. Qucs может пересчитывать S-параметры в Y- и Z-параметры.

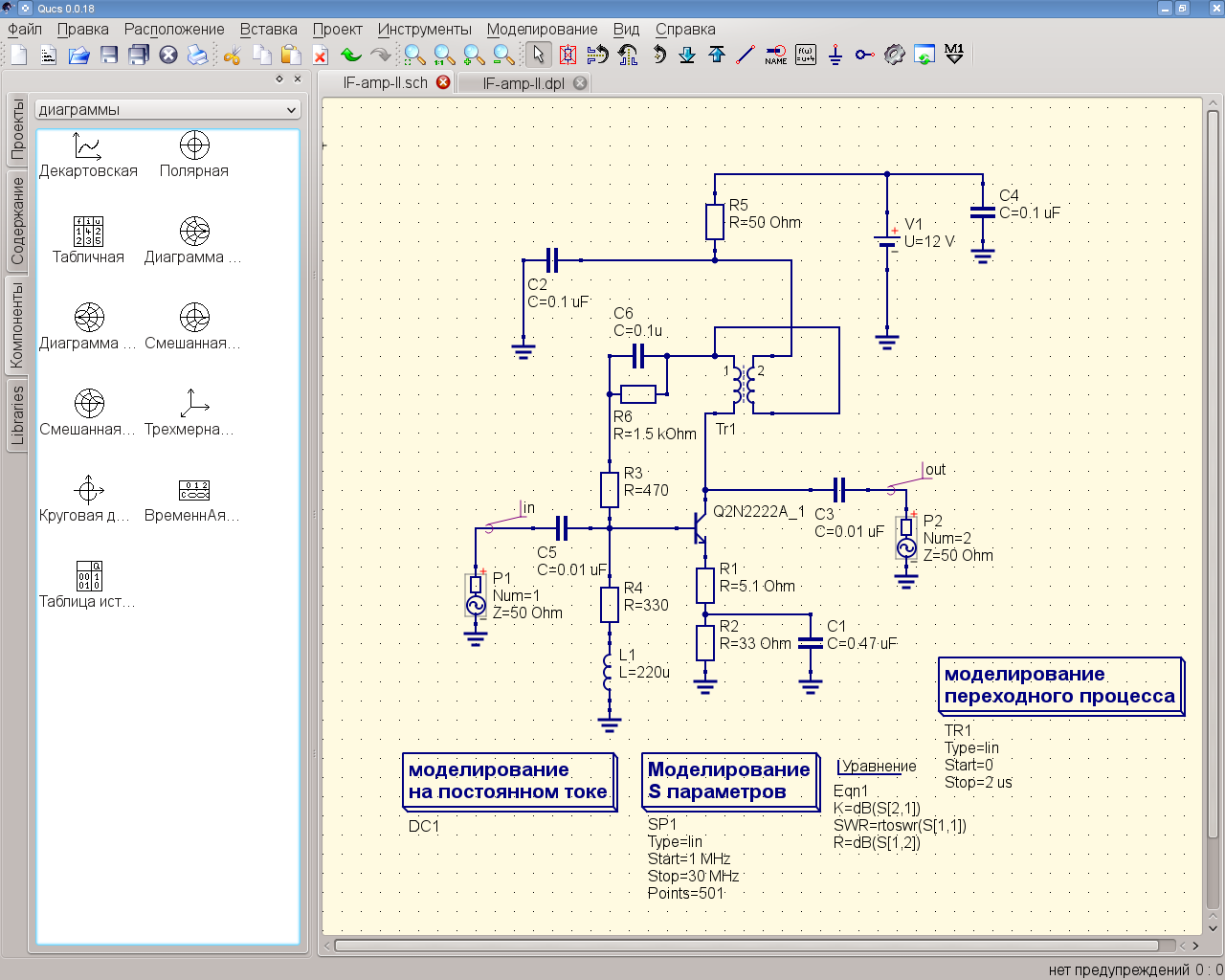

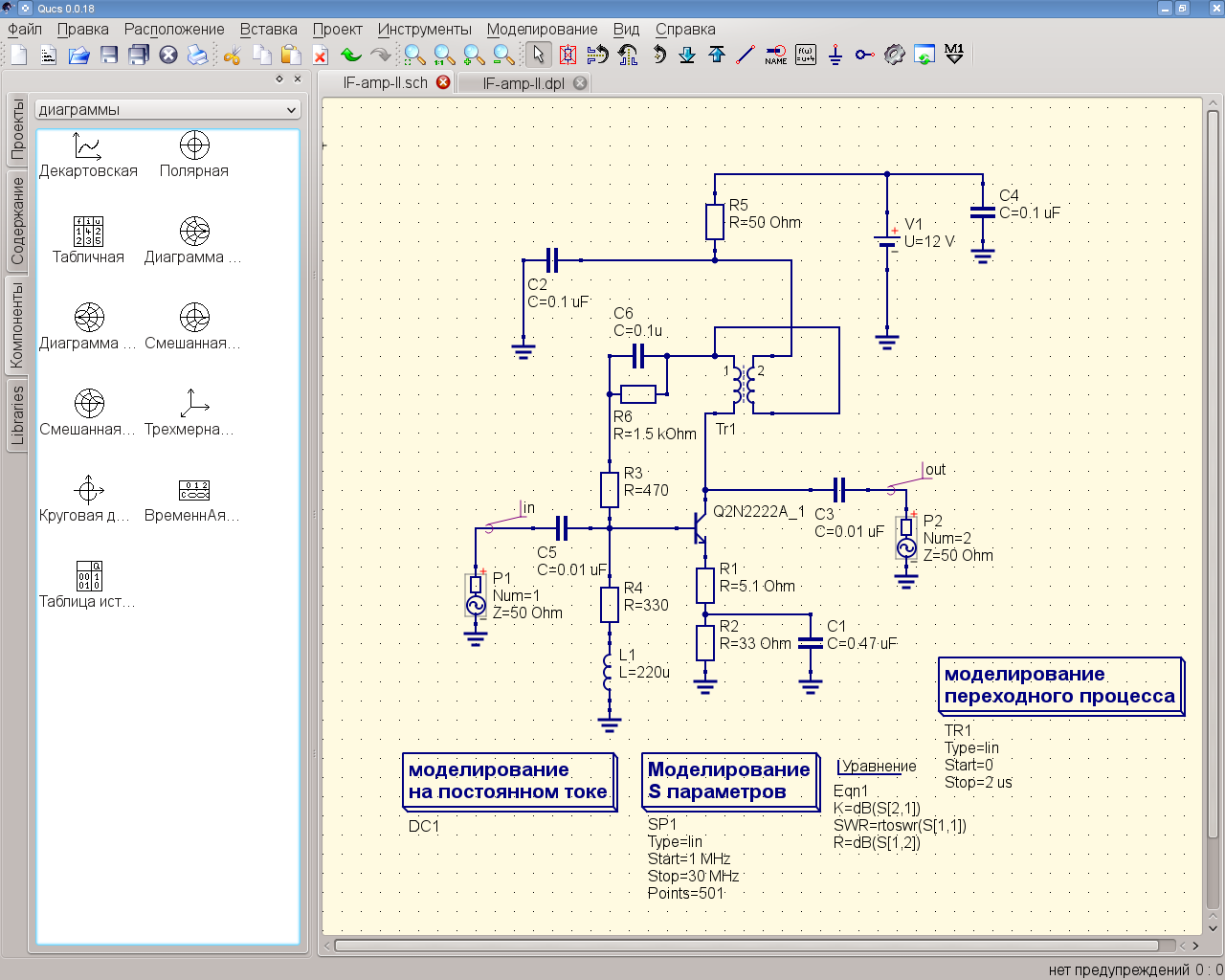

На скриншотах показан пример моделирования S-параметров широкополосного усилителя высокой частоты.

Итак, отличительной особенностью Qucs является возможность анализа комплексных частотных характеристик (КЧХ), построение графиков на комплексной плоскости и диаграмм Смита, анализ комплексных сопротивлений и S-параметров. Эти возможности отсутствуют в проприетарных системах MicroCAP и MultiSim, и здесь Qucs даже превосходит коммерческое ПО и позволяет получить недостижимые для симуляторов электронных схем, основанных на Spice результаты.

Недостатком Qucs является малое количество библиотечных компонентов. Но этот недостаток не является препятствием к использованию, так как Qucs совместим с форматом Spice в котором приводятся модели электронных компонентов в даташитах. Также моделировщик работает медленнее, чем аналогичные Spice-совместимые моделировщики (например MicroCAP (проприетарный) или Ngspice (open-source)).

В настоящее время мы работаем над возможностью предоставления пользователю выбора движка для моделирования схемы. Можно будет использовать встроенный движок Qucs, Ngspice (spice-совместимый консольный моделировщик, похожий на PSpice) или Xyce (моделировщик с поддержкой параллельных вычислений через OpenMPI )

Теперь рассмотрим перечень нововведений в недавнем релизе Qucs 0.0.18 перспективных направлений в разработке Qucs:

Можно заключить, что несмотря на свои недостатки Qucs представляет собой весьма достойную альтернативу проприетарным САПР для моделирования электронных схем.

Ресурсы по Qucs:

Сайт проекта: qucs.sourceforge.net

Репозиторий на Github: github.com/Qucs/qucs

Библиотека отечественных компонентов для Qucs: github.com/ra3xdh/qucs-rus-complib

Разработку данной САПР начали в 2004 году немцы Michael Margraf и Stefan Jahn (в настоящее время не активны). Сейчас Qucs разрабатывается интернациональной командой, в которую вхожу и я. Руководителями проекта являются Frans Schreuder и Guilherme Torri. Под катом будет рассказано о ключевых возможностях нашего моделировщика схем, его преимуществах и недостатках по сравнению с аналогами.

Главное окно программы показано на скриншоте. Там смоделирован резонансный усилитель на полевом транзисторе и получены осциллограммы напряжения на входе и выходе и также АЧХ.

Как видно, интерфейс интуитивно понятен. Центральную часть окна занимает собственно моделируемая схема. Компоненты размещаются на схеме методом перетаскивания из левой части окна. Виды моделирования и уравнения также являются особыми компонентами. Более подробно принципы редактирования схем описаны в документации к программе.

Формат схемного файла Qucs основан на XML и к нему поставляется документация. Поэтому схема Qucs может быть легко сгенерирована сторонними программами. Это позволяет создавать ПО для синтеза схем, которое является расширением Qucs. Проприетарное ПО как правило использует бинарные форматы.

Перечислим основные компоненты, имеющиеся в Qucs:

- Пассивные RCL-компоненты

- Диоды

- Биполярные транзисторы

- Полевые транзисторы (JFET, MOSFET, MESFET и СВЧ-транзисторы)

- Идеальные ОУ

- Коаксиальные и микрополосковые линии

- Библиотечные компоненты: транзисторы, диоды и микросхемы

- Файловые компоненты: подсхемы, spice-подсхемы, компоненты Verilog

Библиотека компонентов использует собственный формат, основанный на XML. Но можно импортировать существующие библиотеки компонентов, основанные на Spice (приводятся в даташитах на электронные компоненты).

Поддерживаются следующие виды моделирования:

- Моделирование рабочей точки на постоянном токе

- Моделирование в частотной области на переменном токе

- Моделирование переходного процесса во временной области

- Моделирование S-параметров

- Параметрический анализ

Результаты моделирования можно экспортировать в Octave/Matlab и выполнить там постобработку данных.

Qucs основан на вновь разработанном движке схемотехнического моделирования. Отличительной особенностью этого движка является встроенная возможность моделирования S-параметров и КСВ, что важно для анализа ВЧ-схем. Qucs может пересчитывать S-параметры в Y- и Z-параметры.

На скриншотах показан пример моделирования S-параметров широкополосного усилителя высокой частоты.

Итак, отличительной особенностью Qucs является возможность анализа комплексных частотных характеристик (КЧХ), построение графиков на комплексной плоскости и диаграмм Смита, анализ комплексных сопротивлений и S-параметров. Эти возможности отсутствуют в проприетарных системах MicroCAP и MultiSim, и здесь Qucs даже превосходит коммерческое ПО и позволяет получить недостижимые для симуляторов электронных схем, основанных на Spice результаты.

Недостатком Qucs является малое количество библиотечных компонентов. Но этот недостаток не является препятствием к использованию, так как Qucs совместим с форматом Spice в котором приводятся модели электронных компонентов в даташитах. Также моделировщик работает медленнее, чем аналогичные Spice-совместимые моделировщики (например MicroCAP (проприетарный) или Ngspice (open-source)).

В настоящее время мы работаем над возможностью предоставления пользователю выбора движка для моделирования схемы. Можно будет использовать встроенный движок Qucs, Ngspice (spice-совместимый консольный моделировщик, похожий на PSpice) или Xyce (моделировщик с поддержкой параллельных вычислений через OpenMPI )

Теперь рассмотрим перечень нововведений в недавнем релизе Qucs 0.0.18 перспективных направлений в разработке Qucs:

- Улучшена совместимость с Verilog

- Продолжается портирование интерфейса на Qt4

- Реализован список недавних открытых документов в главном меню.

- Реализован экспорт графиков, схем в растровые и векторные форматы: PNG, JPEG, PDF, EPS, SVG, PDF+LaTeX. Эта функция полезна при подготовке статей и отчётов, содержащих результаты моделирования

- Возможность открытия документа схемы из будущей версии программы.

- Исправлены баги, связанные с зависанием моделировщика при определённых условиях.

- Ведётся разработка системы синтеза активных фильтров для Qucs (ожидается в версии 0.0.19)

- Ведётся разработка сопряжения с прочими open-source движками для моделирования электронных схем (Ngspice, Xyce, Gnucap). В последующих версиях будет добавлена возможность выбора движка для моделирования схемы.

Можно заключить, что несмотря на свои недостатки Qucs представляет собой весьма достойную альтернативу проприетарным САПР для моделирования электронных схем.

Ресурсы по Qucs:

Сайт проекта: qucs.sourceforge.net

Репозиторий на Github: github.com/Qucs/qucs

Библиотека отечественных компонентов для Qucs: github.com/ra3xdh/qucs-rus-complib